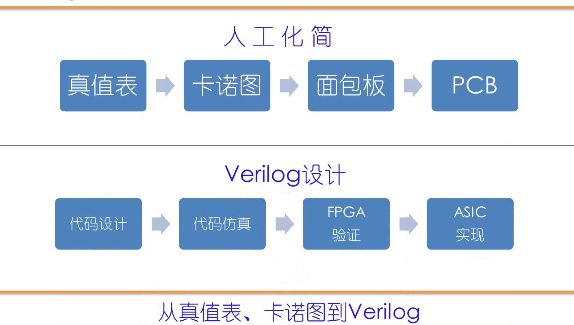

一、设计流程

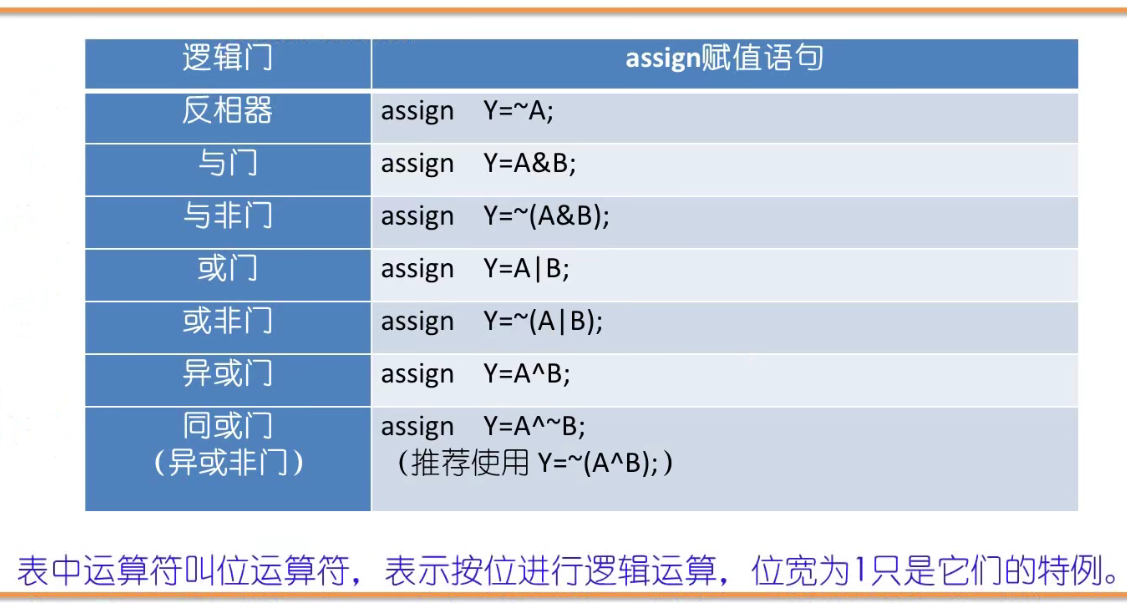

二、位逻辑操作运算符

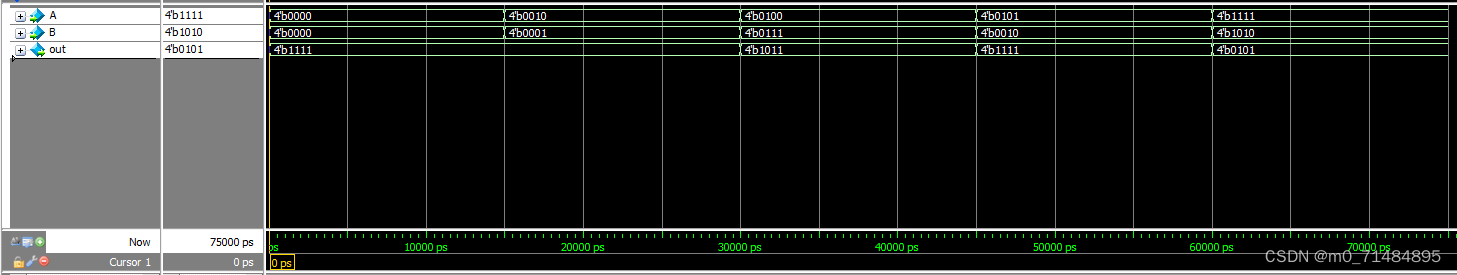

三、四位与非门代码

//2023-5-17

//4位与非门

`timescale 1ns/10ps

module nand_gat_4 (

A,

B,

out

);

input[3:0] A;

input[3:0] B;

output[3:0] out;

assign out = ~(A&B);

endmodule

//------testbench of nand_gate_4-----

module nand_gate_4_tb ;

reg[3:0] A;

reg[3:0] B;

wire[3:0] out;

nand_gat_4 nand_gat_4(

.A(A),

.B(B),

.out(out)

);

initial begin

A<=4'b0000;

B<=4'b0000;

#15

A<=4'b0010;

B<=4'b0001;

#15

A<=4'b0100;

B<=4'b0111;

#15

A<=4'b0101;

B<=4'b0010;

#15

A<=4'b1111;

B<=4'b1010;

#15

$stop;

end

endmodule四、仿真波形

PS:~代表按位取反

学习内容总结自网络,主讲教师为北京交通大学李金城老师

1710

1710

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?