- 实验目的

(1)熟悉Multisim 电路仿真软件的操作界面和功能;

(2)掌握逻辑电路综合设计,并采用仿真软件进行仿真。

- 实验内容

1.试设计一个简易CPU功能的数字电路,实验至少要求采用4个74HC/HCT194作为4个存储单元(可以预先对存储单元存储数据),74HC283作为计算单元。请实现通过第1个时钟脉冲信号取出存储单元中的数据1,第2个时钟脉冲信号取出存储单元中的数据2,第3个时钟脉冲信号计算数据1和数据2求和,第四个时钟脉冲求和数据存回存储单元。使用用Multisim进行逻辑功能仿真。

一、实验过程及分析

(一)设计前准备

1.明确每个时钟脉冲要做哪些事情

第1个时钟脉冲信号取出存储单元中的数据1,第2个时钟脉冲信号取出存储单元中的数据2,第3个时钟脉冲信号计算数据1和数据2求和,第4个时钟脉冲求和数据存回存储单元。

注:Multisim仿真实验中的时钟脉冲频率怎么调

(1)打开Multisim软件,创建一个新的电路设计。

(2)从元器件库中选择时钟脉冲元件,并将其拖入电路图中。

(3)右键单击时钟脉冲元件,选择“属性”命令,打开元件属性对话框。

(4)在属性对话框中,找到“频率”选项,将其值修改为所需的频率。例如,若原频率为1kHz,调慢为 100Hz,则将频率值改为0.1kHz(即100Hz)。需要注意的是,Multisim中时钟脉冲的频率单位是赫兹(Hz)。

2.了解设计所需要的核心元件

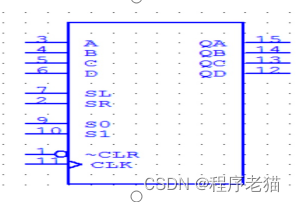

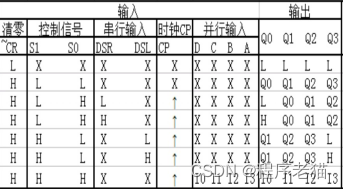

(1)74HC194:

| 如图 DSR端是右移串行数据输入端,DSL是左移串行数据输入端~CLR 为异步清零输入端。下表3为74HC194的功能表,表中第一行表示寄存器异步清零操作;第二行为保持状态; 第三、四行为串行数据右移操作;第五、六行为串行数据的左移操作;第七行为并行数据同步置数操作。

| 74HC194是一个4位双向移位寄存器,具有以下主要功能: MR:数据清零端,低电平有效。 D0~D3:并行数据输入端。 Q0~Q3:并行数据输出端。 SR:右移串行数据输入端。 SL:左移串行数据输入端。 S0和S1:运行方式控制。S0=S1=1时,数据并行输入;S1=0,S0=1时,数据右移输入;S1=1,S0=0时,数据左移输入;S1=S0=0时,寄存器处于保持状态。 CLK:时钟脉冲输入端,上升沿有效1 2。 使用方法: 将MR置高电平,选择控制方式。 若选择并行输入,则将S0和S1置1,给D3到D0数据,并使CP接收到一个上升沿,数据将被写入输出端Q3到Q0。 若选择串行左移输入,则将S0设为0,S1设为1,给SR数据a,CP输出一个上升沿,数据a将被写入D0;接着给SR数据b,CP输出一个上升沿,数据b将被写入D0,并依次移位。 若需要取消输出数据,可以使用MR置0的方式。 |

(2)74HC283:

| A3A2A1A0:四位二进制加数。B3B2B1B0:四位二进制加数。S3S2S1S0:和数。C-1:低位来的给A0的进位信号。C0:A3B3向高位的进位信号。

| 74HC283是一种快速累加器,可用于在数字系统中将两个4位二进制数相加。其工作原理如下: 串行进位:将低位的进位输出信号接到高位的进位输入端,任一位的加法运算必须在低一位的运算完成后进行。 工作流程:第一个全加器根据A0、B0和CI中的进位信号,输出最低位和数S0,把进位信号输出给下一个的全加器,这个全加器根据拿到的进位信号和A、B的输入信号重复上述操作。 电路设计:74LS283包含4个数据输入端口和4个数据输出端口,以及一个车载(Carry)端口和一个借位(Borrow)端口。这些端口可以用来控制计算器的各种操作。 借位功能:当某一位需要借位时,该位的借位端口会发出借位信号,通知前一位进行借位操作。 综上所述,74HC283能够快速地完成二进制数的累加操作,并且具有高度的可靠性和稳定性,因此在数字系统中得到了广泛的应用。 |

(3)74LS138:

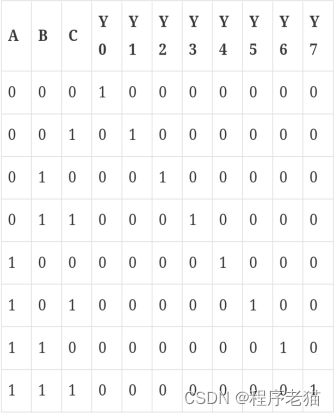

| 74LS138是一种三-八线译码器,用于将三位二进制信号转换为八个输出信号。其逻辑功能过程原理如下:该译码器有三个输入引脚A0、A1和A2,它们可以接收二进制信号,用于选择要解码的值。同时,该译码器还有八个输出引脚Y0-Y7,用于输出解码后的结果。当输入信号为000时,Y0引脚输出高电平,其他引脚输出低电平;当输入信号为001时,Y1引脚输出高电平,其他引脚输出低电平;以此类推,当输入信号为111时,Y7引脚输出高电平,其他引脚输出低电平。当使能引脚(E1、E2、E3)均为低电平时,输入信号会被正确地解码并输出到对应的输出引脚上。此外,74LS138还具有以下三种使能模式:1)E1为高电平,E2和E3为低电平:此时,只有Y0输出引脚会被置位。2)E2为高电平,E1和E3为低电平:此时,只有Y4-Y7输出引脚会被置位。3)E3为高电平,E1和E2为低电平:此时,只有Y0-Y5输出引脚会被置位。 |

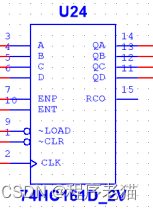

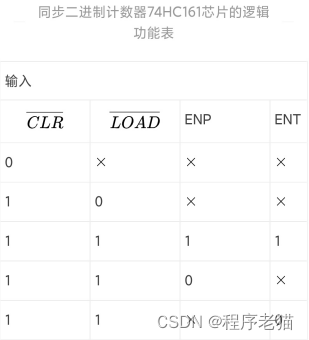

(4)74HC161:

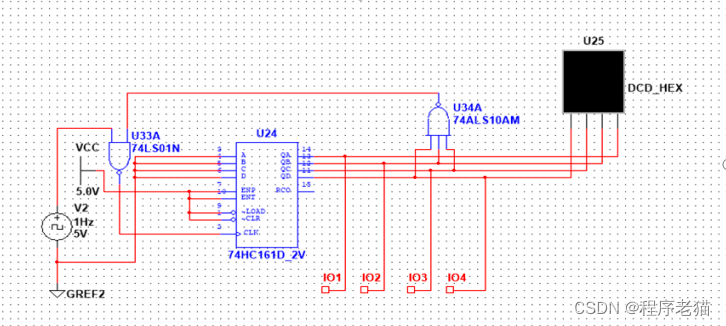

|

| 74HC161是CMOS型的,是常用的四位二进制可预置的同步加法计数器它可以灵活的运用在各种数字电路,以及单片机系统中实现分频器等很多重要的功能。 据输入端:ABCD 数据输出端:QA QB QC QD 同步置数:非LOAD 异步清零控制端:非CLR 置数控制端:ENT、ENP 进位输出端:RCO 时钟输入端:CLK 74hc161的主要功能如下: (1)异步清零功能:当CLR的反为零时,不论有无时钟脉冲CLK和其他信号输入,计数器被清零,即Qd~Qa都为0。 (2)同步并行置数功能:当CLR的反=1,LOAD的反=0时,在输入时钟脉冲CLK上升沿的作用下,并行输入的数据dcba被置入计数器,即Qd~Qa=dcba。 (3)计数功能:当LOAD的反=CLR的反=ENP=ENT=1,当CLK端输入计数脉冲时,计数器进行二进制加法计数 (4)保持功能:当LOAD的反=CLR的反=1时,且ENP和ENT中有”0“时,则计数器保持原来状态不变。 |

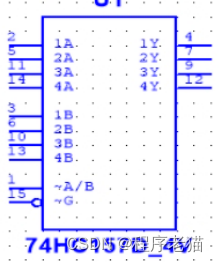

(5)74157:

|

74HC157功能表

| 所示为74×157的逻辑图和图形符号芯片内部集成了4个2选1数据选择器,同时,还有一个低电平有效的使能输入。图中信号名之前增加了一个数字用于分组,表示是哪一路数据选择器的输入、输出信号,这是器件数据手册中经常使用的一种方式。 由表可知,当=1时,不管通道选择输入S为何值,输出都为0。当=1时,数据选择器能够正常工作:若S=0,则将D0数据传送到相应的输出端;若S=1,则将D1,数据传送到相应的输出端。 |

(二)总的设计分析

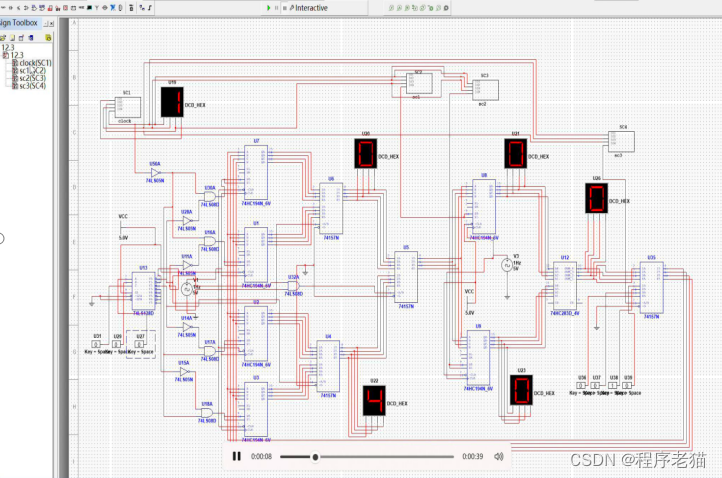

|

| 电路图中,我们采用74LS138三八译码器进行寄存器的选择,由二进制输入端输入的信号来决定选择哪些寄存器。 我们小组采用的是十六位计数器,其中脉冲设置为1赫兹,0到3秒输入加数,4到7秒输入被加数,输入被加数后加法器马上计算出和,8秒后将相加结果传回加数寄存器中。利用了38译码器给四个寄存器分配数据传人的地址。这里我们利用三个触发器构成的四路选择器将各个数进行寄存,选择的四个数由38译码器的BA输入端决定,即通过输入00 0110 11分别对应12 3 4。由于输入加数和被加数后加法器马上会得出结果,所以实际上并不是按实验要求8秒后得出和,因此我们小组设计利用一个寄存器实现8秒后将和传回前面的寄存器。为了实现这个过程,我们把输入数据的按键放到加法器这边方便传回数据,不过由于是讲和传回四个寄存器的输人端,所以地址会根据加数的地址改变。 |

- 封装函数分析

1.clock(SC1)作用分析:

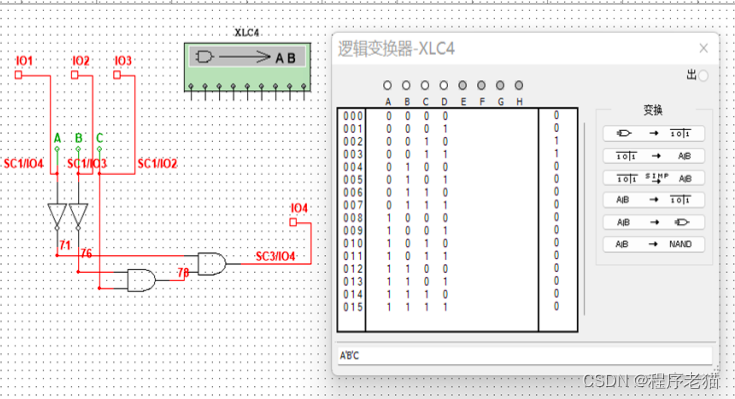

| |

| 输出的时钟脉冲信号用于(传递给U7、U1、U2、U3)控制整个电路中寄存器、计数器的工作情况 | 输出IO4、IO3、IO2、IO1 |

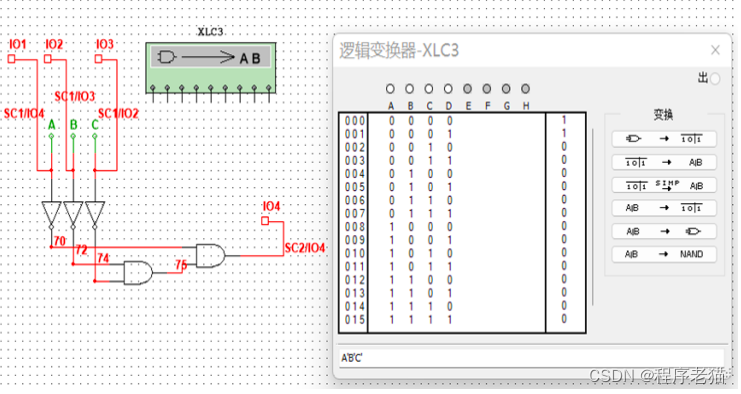

2.clock(SC2)作用分析

| |

| 输入IO1、IO2、IO3 | 输出IO4=A'B'C' |

| 来自时钟脉冲输出的的IO3、IO2、IO1 | 输出信号传递给U8的S0、S1 |

| 这里的信号属于第一个时钟脉冲信号0到3秒时,取出存储单元中的数据1,并存在相应的寄存器中 | |

3.clock(SC3)作用分析

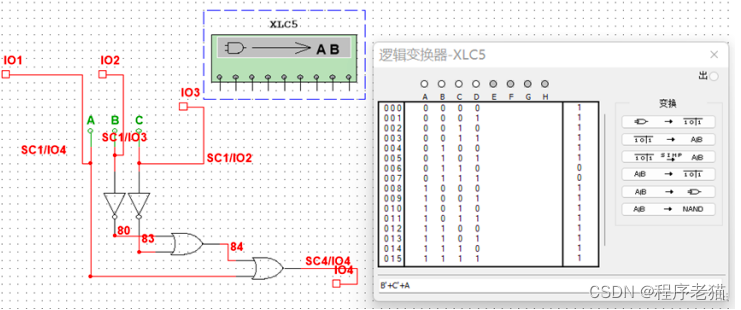

| |

| 输入IO1、IO2、IO3 | 输出IO4=A'B'C |

| 来自时钟脉冲输出的IO3、IO2、IO1 | 输出信号传递给U9的S0、S1 |

| 这里的信号属于第二个时钟脉冲信号4到7秒时,取出存储单元中的数据2,并存在相应的寄存器中,传到计数器,这时计数器得到加数 | |

4.clock(SC4)作用分析

| |

| 输入IO1、IO2、IO3 | 输出IO4=A+B'+C' |

| 来自时钟脉冲输出的IO4、IO3、IO2 | 输出信号传递给U35的~A/B |

| 这里的信号属于第三和四个时钟脉冲信号,第三个脉冲信号6到7秒时,计数器得到数据2作为被加数,并进行加数与被加数的求和,第四个脉冲信号6到8秒时,将和数返回原来(指定)的寄存器中 | |

- 实验成果

实验成果见附录视频。

- 实验总结

在仿真过程中,我们观察到每个时钟脉冲信号触发后,数据能够正确地从存储单元中取出,并送入计算单元进行计算,最后再将结果存回存储单元。通过本次实验,我们验证了数字电路设计的正确性和可行性。同时,也让我们更深入地了解了CPU的基本工作原理和数据处理流程。这对于我们在后续的数字电路设计和计算机系统开发中具有重要的指导意义。

此外,我们还发现,通过合理地选择和配置数字逻辑电路,我们可以实现各种不同的计算和数据处理功能。这为我们进一步探索和研究更复杂的计算机系统提供了无限的可能性。

本次实验达到了预期的目标,不仅提高了我们的数字电路设计能力,还拓宽了我们对计算机系统的认识和理解。增加了团队之间合作和团队之间的凝聚力。

实验通过Multisim软件设计了一个简易CPU功能的数字电路,利用74HC/HCT194作为存储单元,74HC283作为计算单元。每个时钟脉冲分别完成取数据、计算和存储操作,验证了数字电路设计的正确性,加深了对CPU工作原理的理解。

实验通过Multisim软件设计了一个简易CPU功能的数字电路,利用74HC/HCT194作为存储单元,74HC283作为计算单元。每个时钟脉冲分别完成取数据、计算和存储操作,验证了数字电路设计的正确性,加深了对CPU工作原理的理解。

2042

2042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?