问题:

在一个工程中,PCIE在FPGA芯片中默认的位置在X0Y0,如果管脚没在这个位置,在XDC中再次绑定时可能出错。

另外工程中还有JESD204B的PHY,PCIE有可能占用PHY的管脚,导致明明已经绑定了对应的JESD管脚,还是提示管脚没有绑定出错。这是PCIE默认的XDC把管脚占了。

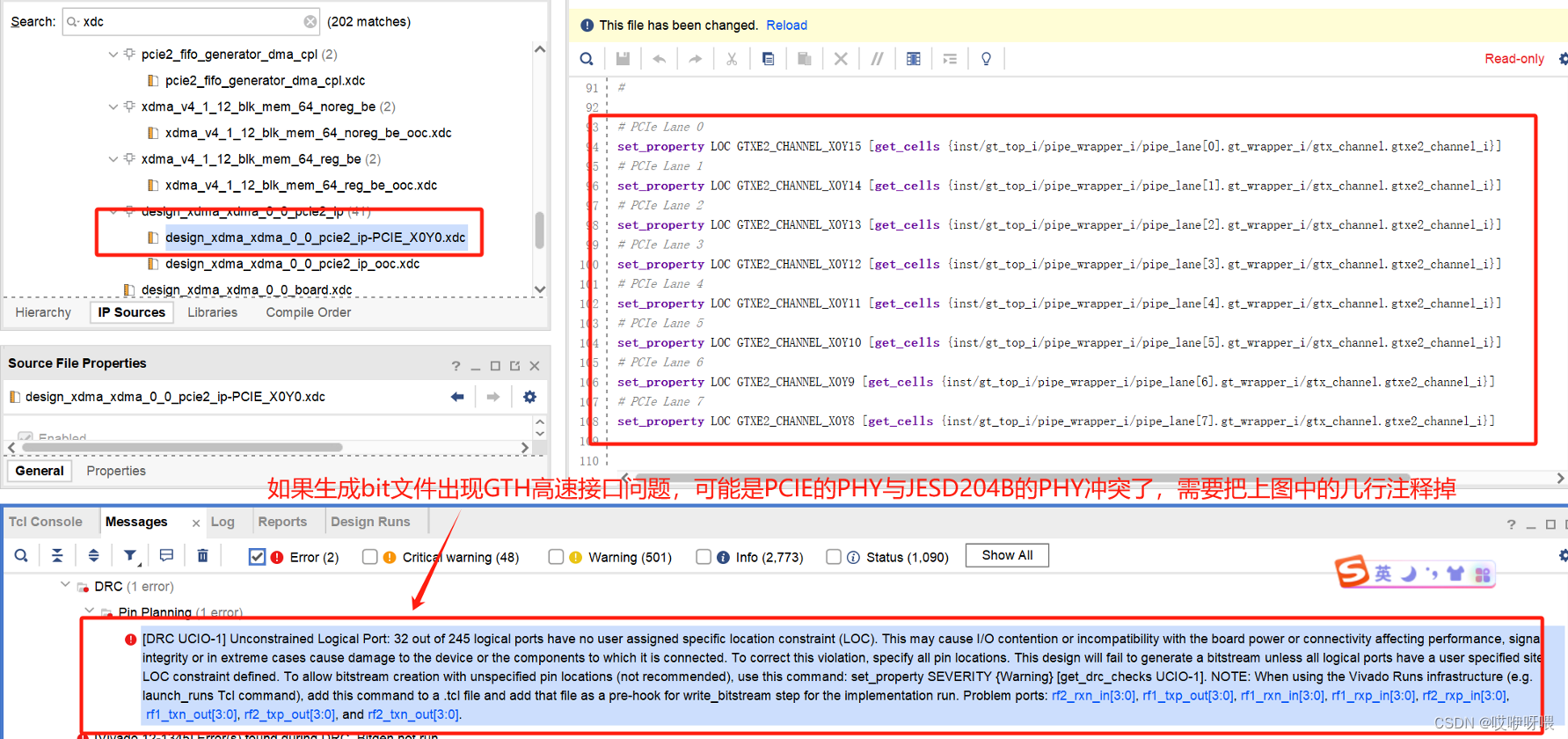

解决:

在IP中找到PCIE自带的XDC,把关于lane的管脚绑定注释掉,再跑一次工程问题就解决了。

官方解释:

问题:

在一个工程中,PCIE在FPGA芯片中默认的位置在X0Y0,如果管脚没在这个位置,在XDC中再次绑定时可能出错。

另外工程中还有JESD204B的PHY,PCIE有可能占用PHY的管脚,导致明明已经绑定了对应的JESD管脚,还是提示管脚没有绑定出错。这是PCIE默认的XDC把管脚占了。

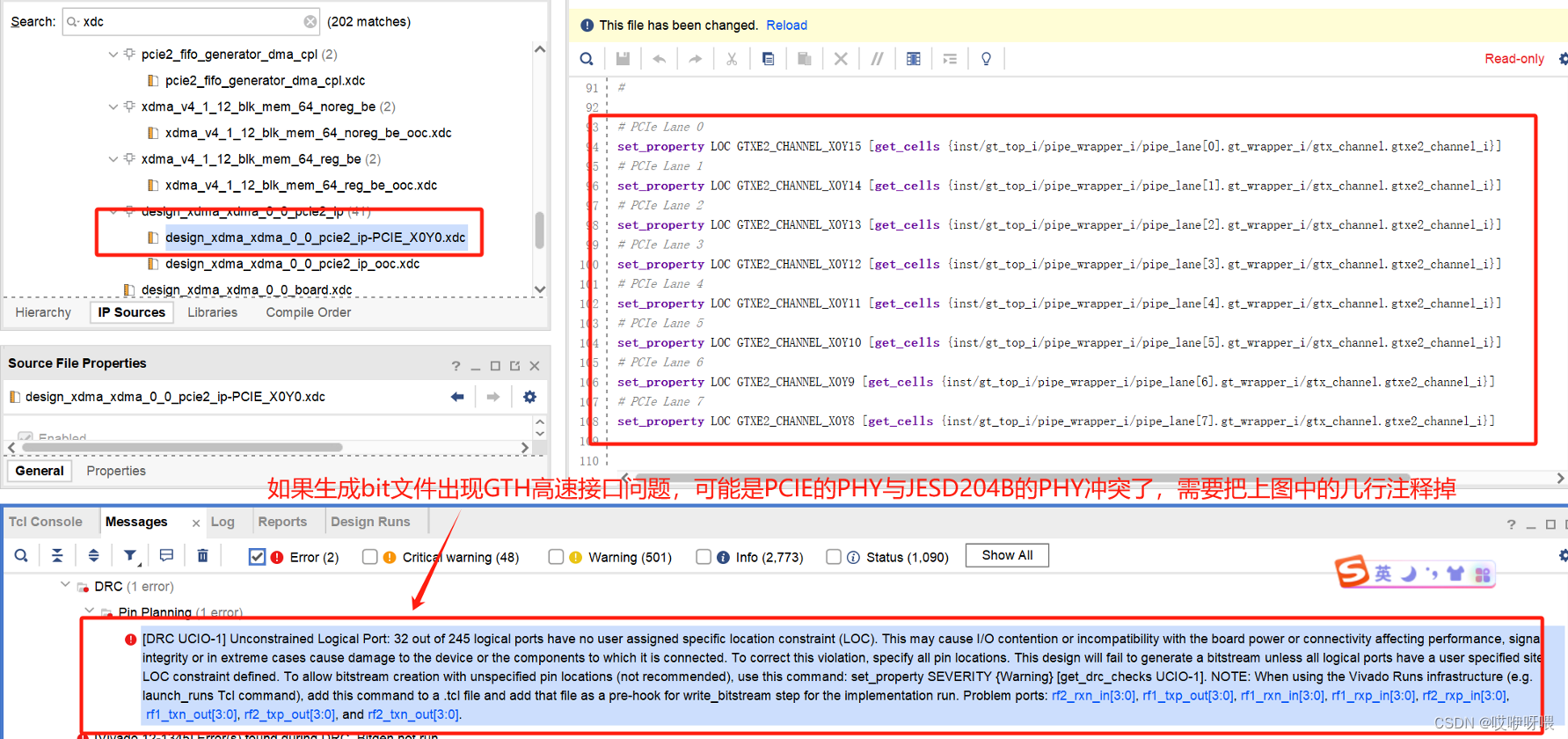

解决:

在IP中找到PCIE自带的XDC,把关于lane的管脚绑定注释掉,再跑一次工程问题就解决了。

官方解释:

1万+

1万+

9035

9035

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?