目录

概述

本文主要介绍ARM Contex-CM3相关的知识,包括内核架构,寄存器组,和指令集等内容。

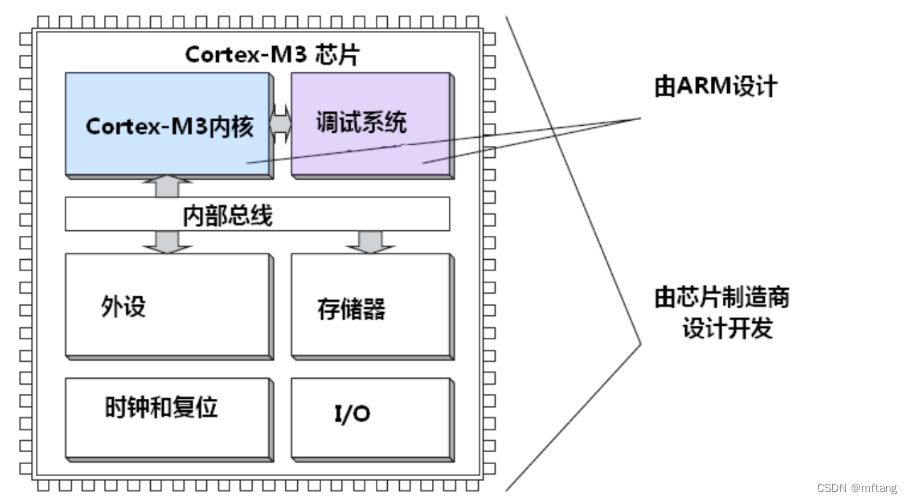

1. Cortex-M3类型MCU

1.1 MCU 架构

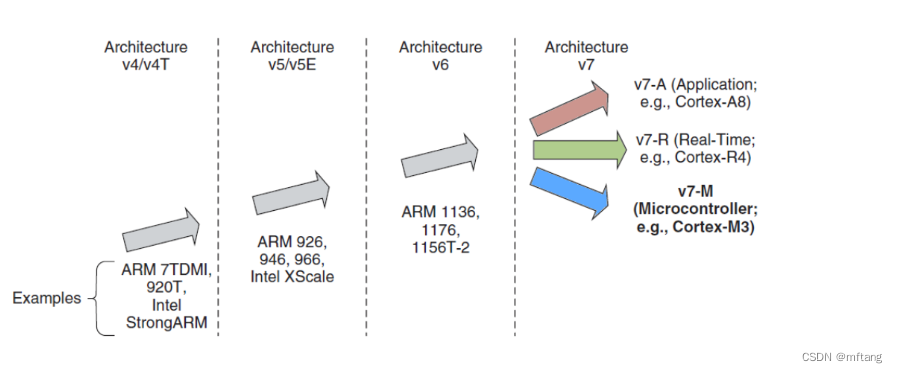

历史:

-

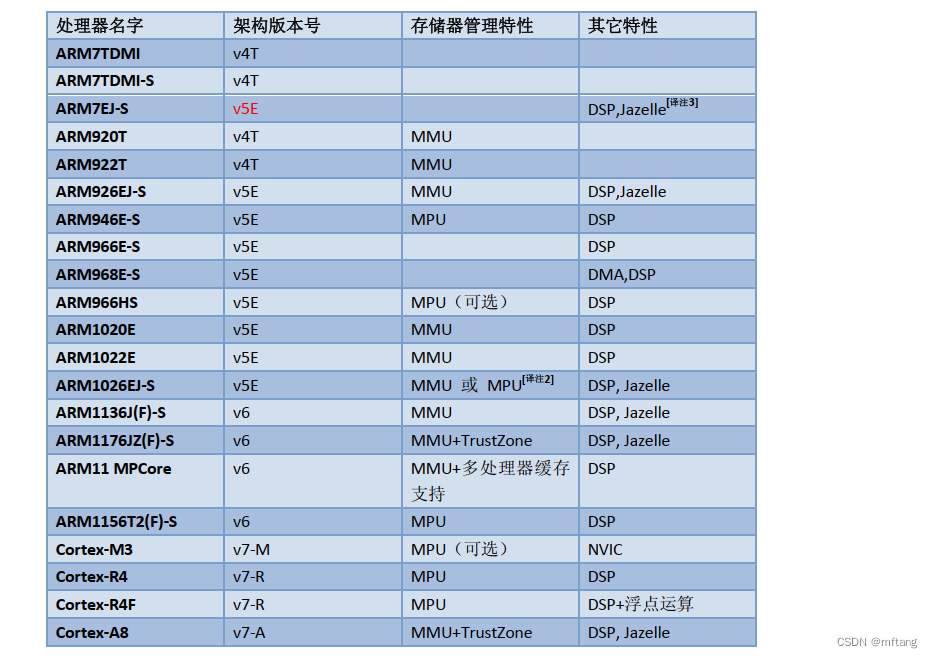

ARMv4T架构: ARM7TDMI(T表示支持“Thumb指令”)

-

ARMv5TE架构: ARM9E处理器 , ARM9E家族成员包括ARM926E-S和ARM946E-S ,

特点:

ARMv5TE架构添加了“服务于多媒体应用增强的DSP指令”

-

ARMv6架构 : ARM1136J(F)-S, ARM1156T2(F)-S,以及 ARM1176JZ(F)-S

特点:

1)单指令流多数据流(SIMD)指令也是从v6开始首次引入的;

2)优化Thumb-2指令集

-

ARMv7架构 :

| 类型 | 描述 |

|---|---|

| 款式A | 设计用于高性能的“开放应用平台”——越来越接近电脑,特点:支持大型嵌入式操作系统 |

| 款式R | 用于高端的嵌入式系统,尤其是那些带有实时要求的——又要快又要实时。 特点: 硬实时且高性能的处理器。标的是高端实时 |

| 款式M | 用于深度嵌入的,单片机风格的系统中。认准了旧世代单片机的应用而量身定制。在这些应用中,尤其是对于实 时控制系统,低成本、低功耗、极速中断反应以及高处理效率,都是至关重要的。 |

ARM处理器架构进化史

1.2 实时性系统概念

从定义的角度讲,“实时”就是指系统必须在给定的死线(deadline,亦称作“最后期限” )内做出响应。在一个以ARM处理器为核心的系统中,决定能否达到“实时”这个目标的,有很多因素,主要如下:

1)中断延迟

2)存储器延时

3)当时处理器是否在运行更高优先级的中断服务例程

1.3 处理器命名法

一个demo:

1.4 MCU的一些知识

1. MMU(储器管理单元)

用于实现虚拟内存和内存的分区保护,这是应用处理器与嵌入式处理器的分水岭。电脑和数码产品所使用的处理器几乎清一色地都带MMU。 但是MMU也引入了不确定性,这有时是嵌入式领域——尤其是实时系统不可接受的。然而对于安全关键(safety-critical)的嵌入式系统, 还是不能没有内存的分区保护的。为解决矛盾, 于是就有了MPU。 可以把MPU认为是MMU的功能子集,它只支持分区保护,不支持具有“定位决定性”的虚拟内存机制。

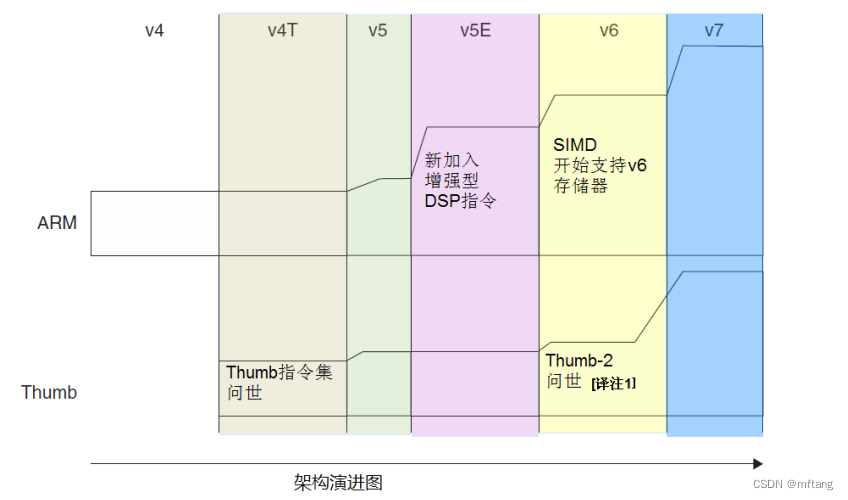

2. 指令集

ARM处理器一直支持两种形式上相对独立的指令集,在程序的执行过程中,处理器可以动态地 在两种执行状态之中切换。Thumb指令集在功能上是ARM指令集的一个子集它们分别是 :

32位的ARM指令集,对应处理器状态: ARM状态

16位的Thumb指令集,对应处理器状态: Thumb状态

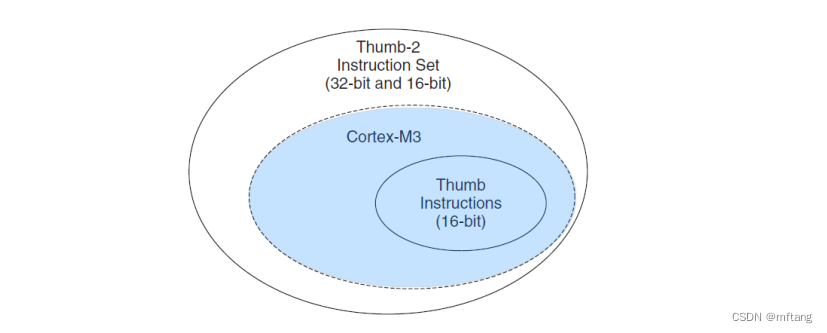

3. Thumb-2 指令集体系体系结构

Thumb-2是16位Thumb指令集的一个超集,在Thumb-2中, 16位指令首次与32位指令并存,结果在Thumb状态下可以做的事情一下子丰富了许多,同样工作需要的指令周期数也明显下降。

2. Cortex-M3 概览

2.1 Cortex-M3综述

Cortex-M3 是一个 32 位处理器内核。内部的数据路径是 32 位的,寄存器是 32 位的,存储器接口也是 32 位的。 CM3 采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访 问并行不悖。这样一来数据访问不再占用指令总线,从而提升了性能。为实现这个特性, CM3 内部 含有好几条总线接口,每条都为自己的应用场合优化过,并且它们可以并行工作。但是另一方面, 指令总线和数据总线共享同一个存储器空间(一个统一的存储器系统)。换句话说,不是因为有两 条总线,可寻址空间就变成 8GB 了。

特点:

Cortex-M3 是 32 位处理器内核,其内部路径和寄存器都是32位

采用哈佛结构:拥有独立的指令总线和数据总线

支持大端和小端模式

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3516

3516

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?