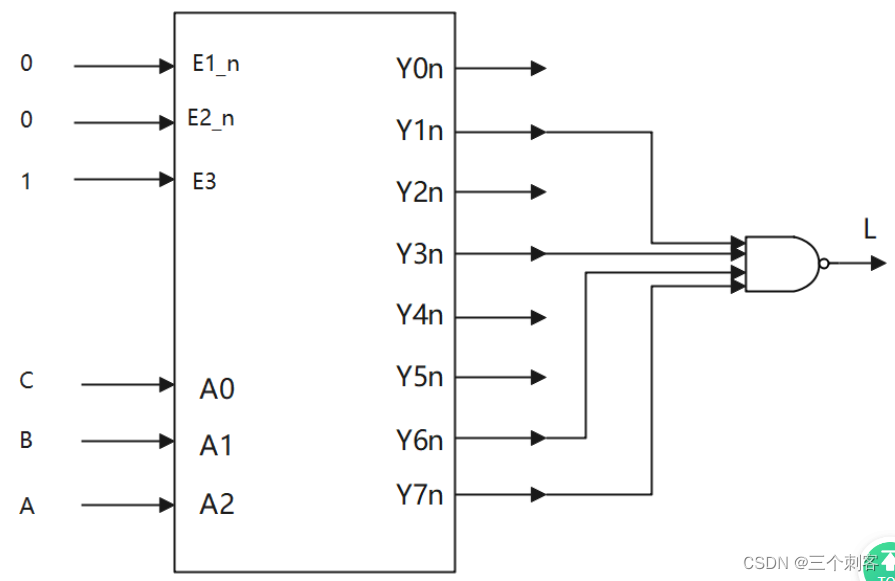

思路:此方法可适合于任何逻辑函数,需要将L=(~A)·C+A·B 逻辑式转换为最小项的形式。

实现逻辑表达式

38译码器的输出实际上包含了输入A2 A1 A0组成的所有最小项,而该逻辑表达式作为组合电路,其输出最终可化简为最小项的形式。

由于译码器的输出为最小项取反,而逻辑函数可以写成最小项之和的形式,故可以利用附加的门电路和译码器实现逻辑函数。

由逻辑表达式可得出,输出L的逻辑表达式用最小项表示为:

L = m1+m3+m6+m7

由于译码器的输出为最小项取反,下面需要将表达式中的最小项转换为最小项取反的形式。根据反演定理,转换结果如下:

L = (m1’m3’m6’m7’)’;

‘表示取反。

由上式可知,采用与非门即可实现该电路的组合逻辑输出。

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

wire Y0_n;

wire Y1_n;

wire Y2_n;

wire Y3_n;

wire Y4_n;

wire Y5_n;

wire Y6_n;

wire Y7_n;

decoder_38 U0(

.E1_n(1'b0),

.E2_n(1'b0),

.E3(1'b1),

.A0(C),

.A1(B),

.A2(A),

.Y0_n(Y0_n),

.Y1_n(Y1_n),

.Y2_n(Y2_n),

.Y3_n(Y3_n),

.Y4_n(Y4_n),

.Y5_n(Y5_n),

.Y6_n(Y6_n),

.Y7_n(Y7_n)

);

assign L = ~(Y1_n & Y3_n & Y6_n & Y7_n);

endmoduleY1_n相当于~m1

此方法是A、B、C分别对应接入3-8译码器的A2、A1、A0,所以最小项是1、3、6、7

如果C、B、A分别对应接入3-8译码器的A2、A1、A0,所以最小项是3、4、6、7,就变成下面的解法

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

wire [7:0] Y;

assign L = ~Y[3] + ~Y[4] + ~Y[6] + ~Y[7];

decoder_38 inst(

.E1_n(0),

.E2_n(0),

.E3 (1),

.A0(A),

.A1(B),

.A2(C),

.Y0_n(Y[0]),

.Y1_n(Y[1]),

.Y2_n(Y[2]),

.Y3_n(Y[3]),

.Y4_n(Y[4]),

.Y5_n(Y[5]),

.Y6_n(Y[6]),

.Y7_n(Y[7])

);

endmodule解法三:最容易想到的

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

assign L = (~A&C)|(A&B);

endmodule解法四:简单

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

wire y0,y1,y2,y3,y4,y5,y6,y7;

decoder_38 inst(0,0,1,C,B,A,y0,y1,y2,y3,y4,y5,y6,y7);

assign L = ~y1 + ~y3 + ~y6 + ~y7;

endmodule在例化时不用写点和括号了

本文介绍如何使用3-8译码器实现特定逻辑函数。通过将逻辑表达式转换为最小项形式,并利用译码器输出的最小项进行组合,可以实现任意逻辑函数。文中提供了几种不同的实现方案。

本文介绍如何使用3-8译码器实现特定逻辑函数。通过将逻辑表达式转换为最小项形式,并利用译码器输出的最小项进行组合,可以实现任意逻辑函数。文中提供了几种不同的实现方案。

1992

1992

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?