首先,什么是38译码器?38译码器,顾名思义,3线8线译码器,3线指三位二进制数字,会组成000到111共8个不同的数字,所以有八种状态,所以取名三八译码器,4线16线也是如此。

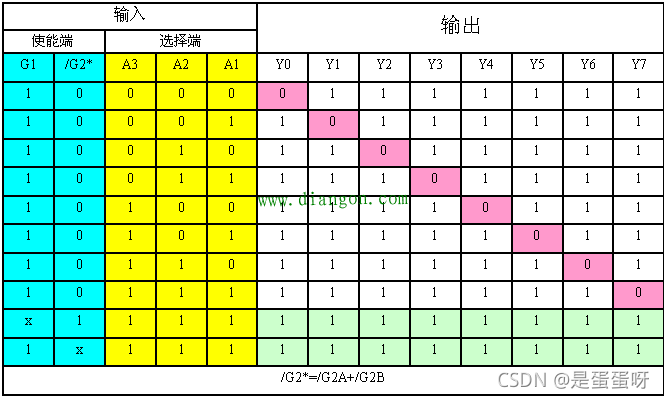

一般来说,38译码器有A1、A2、A3分别为输入端,G1为使能端的高电平,Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7分别为输出端。下面是38译码器真值表:

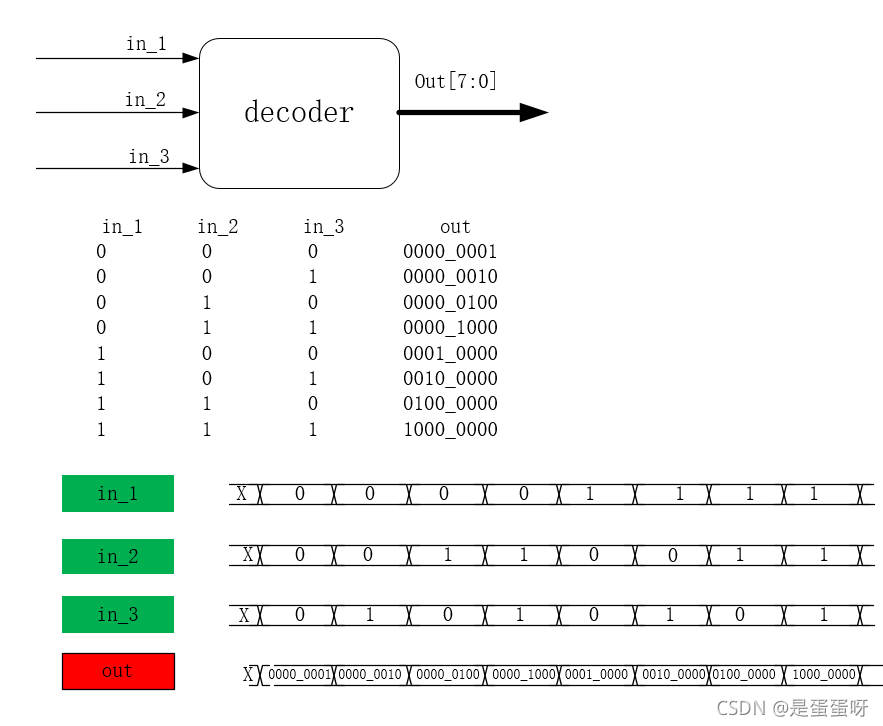

代码中,输出out是上图真值表的反码,即输入000输出0000_0001,

首先用Visio软件进行绘图,绘制出输入以及对于的输出

那么,如何用FPGA实现38译码器的功能呢?下面进行介绍

module decoder

(

input wire in_1,

input wire in_2,

input wire in_3,

output reg [7:0] out

);

/* always@(*)

if({in_1,in_2,in_3} == 3'b000)

out = 8'b0000_0001;

else if({in_1,in_2,in_3} == 3'b001)

out = 8'b0000_0010;

else if({in_1,in_2,in_3} == 3'b010)

out = 8'b0000_0100;

else if({in_1,in_2,in_3} == 3'b011)

out = 8'b0000_1000;

else if({in_1,in_2,in_3} == 3'b100)

out = 8'b0001_0000;

else if({in_1,in_2,in_3} == 3'b101)

out = 8'b0010_0000;

else if({in_1,in_2,in_3} == 3'b110)

out = 8'b0100_0000;

else if({in_1,in_2,in_3} == 3'b111)

out = 8'b1000_0000;

else

out = 8'b0000_0000; */

always@(*)

case({in_1,in_2,in_3})

3'b000:out = 8'b0000_0001;

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

default:out = 8'b0000_0000;

endcase

endmodule注:这里编写程序时没用添加使能端和置位端口,读者可自行添加,代码段用了两种程序,一个是 if 语句,另外一个是 case 语句,其中 if 语句已经被注释掉,读者可自行更换。

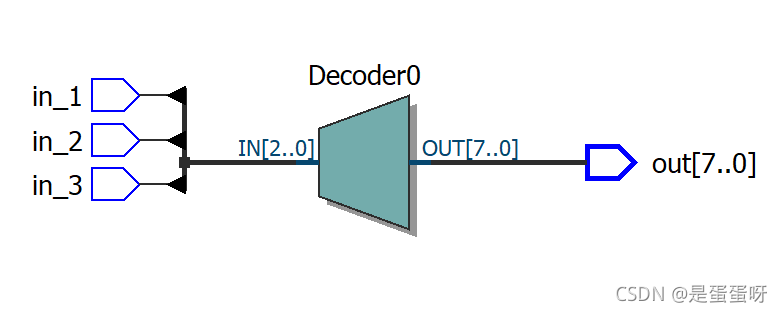

用case编程在Quartus中生成的RTL视图如下,

输入为 in_1,in_2,in_3,输出为 out

下面是赋值程序:

`timescale 1ns/1ns

module tb_decoder();

reg in_1;

reg in_2;

reg in_3;

wire [7:0] out;

initial

begin

in_1 <= 1'b0;

in_2 <= 1'b0;

in_3 <= 1'b0;

end

always #10 in_1 <= {$random}%2;

always #10 in_2 <= {$random}%2;

always #10 in_3 <= {$random}%2;

decoder decoder_inst

(

.in_1(in_1),

.in_2(in_2),

.in_3(in_3),

.out(out)

);

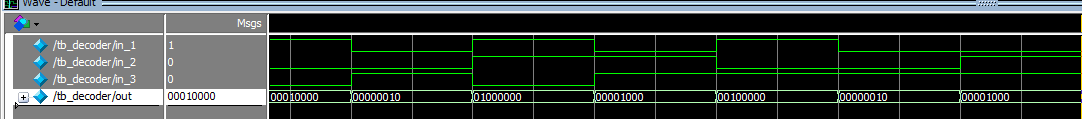

endmodule程序中,random 的作用是产生一个随机数,用产生的这个随机数%2得到数非0即1,可以作为输入。再用ModeSim进行波形仿真如下:

符合预期效果

本文详细介绍了38译码器的工作原理,包括其结构、真值表和Visio绘图。核心内容是如何使用Verilog在FPGA中编码实现,并提供了使用case语句的代码示例。通过ModeSim波形仿真验证了译码器的正确性。

本文详细介绍了38译码器的工作原理,包括其结构、真值表和Visio绘图。核心内容是如何使用Verilog在FPGA中编码实现,并提供了使用case语句的代码示例。通过ModeSim波形仿真验证了译码器的正确性。

1985

1985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?