一、题目

请使用3-8译码器①和必要的逻辑门实现函数L=(~A)·C+A·B

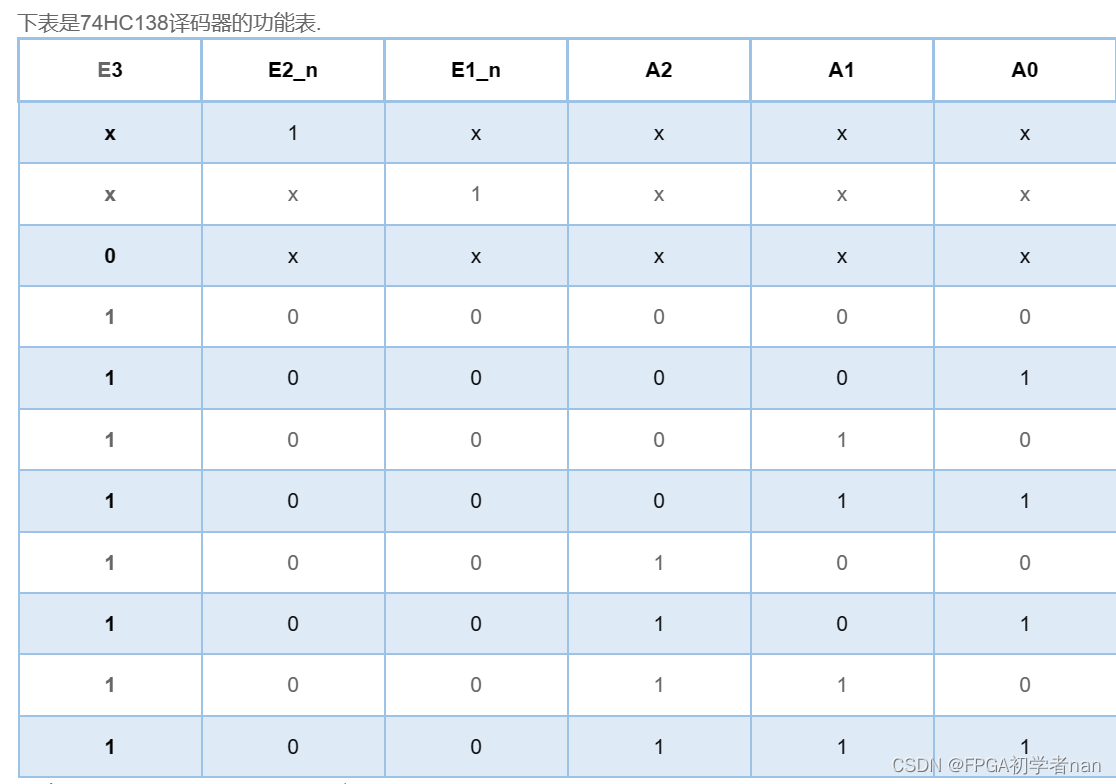

可在本题答案中添加并例化3-8译码器①代码,3-8译码器①代码如下:

module decoder_38( input E1_n , input E2_n , input E3 , input A0 , input A1 , input A2 , output wire Y0_n , output wire Y1_n , output wire Y2_n , output wire Y3_n , output wire Y4_n , output wire Y5_n , output wire Y6_n , output wire Y7_n ); wire E ; assign E = E3 & ~E2_n & ~E1_n; assign Y0_n = ~(E & ~A2 & ~A1 & ~A0); assign Y1_n = ~(E & ~A2 & ~A1 & A0); assign Y2_n = ~(E & ~A2 & A1 & ~A0); assign Y3_n = ~(E & ~A2 & A1 & A0); assign Y4_n = ~(E & A2 & ~A1 & ~A0); assign Y5_n = ~(E & A2 & ~A1 & A0); assign Y6_n = ~(E & A2 & A1 & ~A0); assign Y7_n = ~(E & A2 & A1 & A0); endmodule

输入描述:

input A ,

input B ,

input C

输出描述:

output wire L

二、分析题目

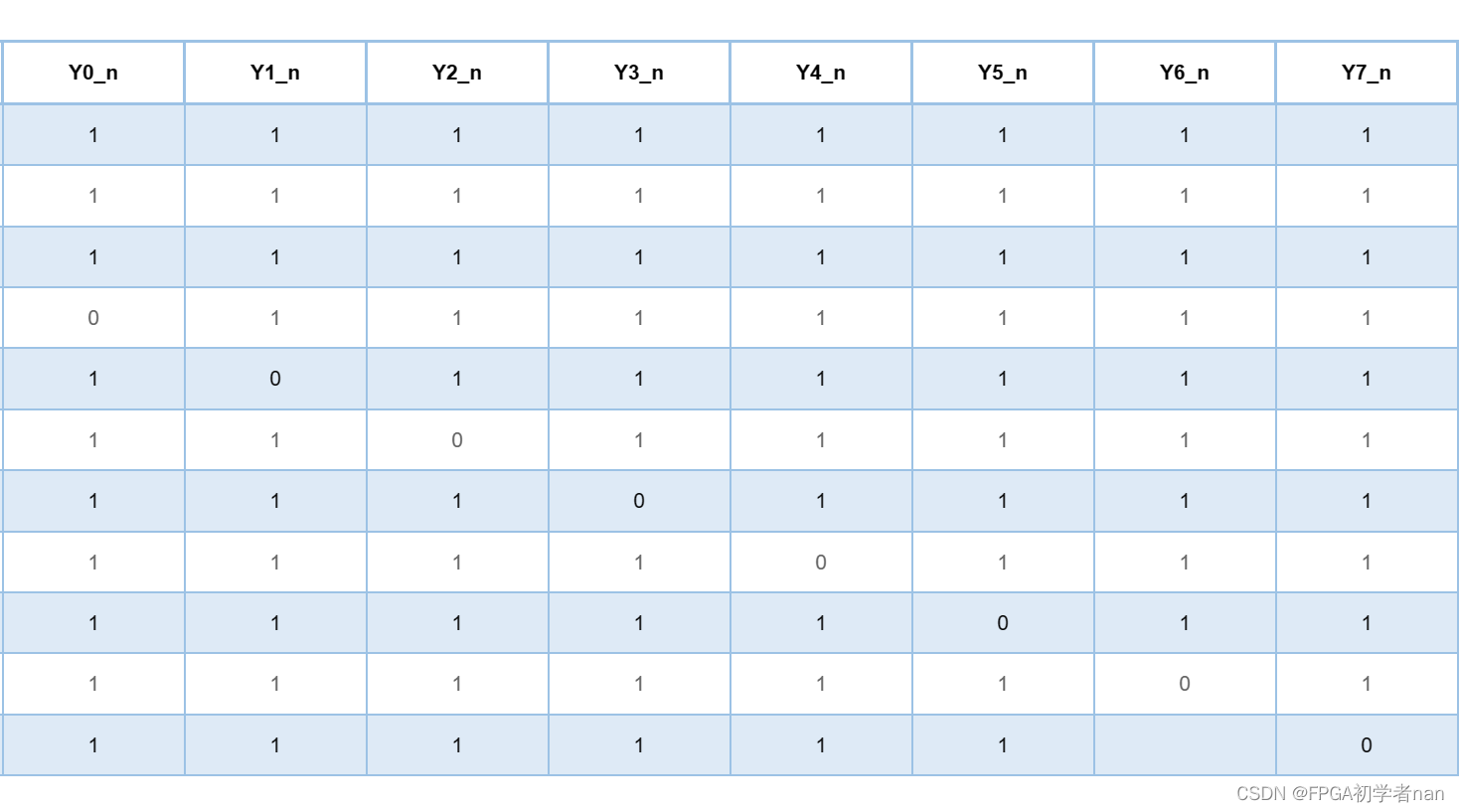

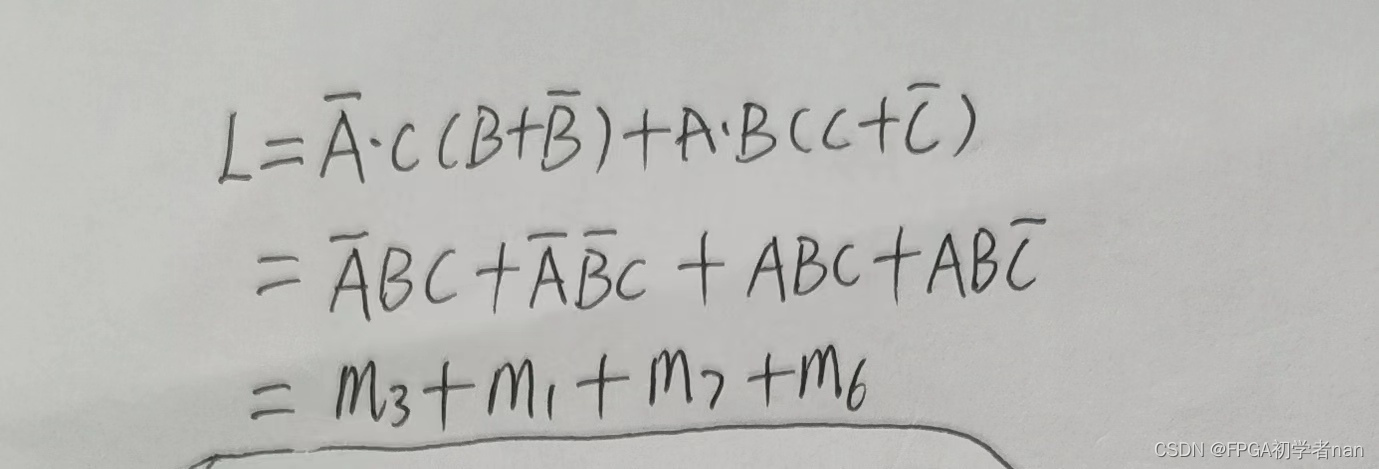

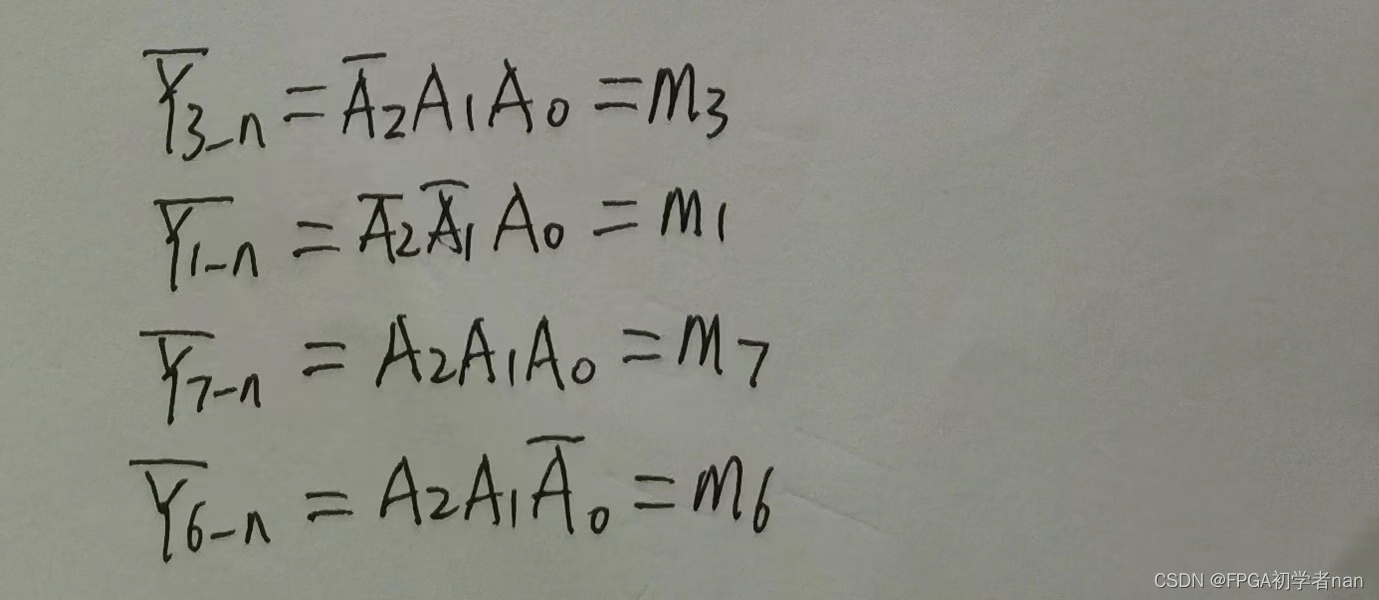

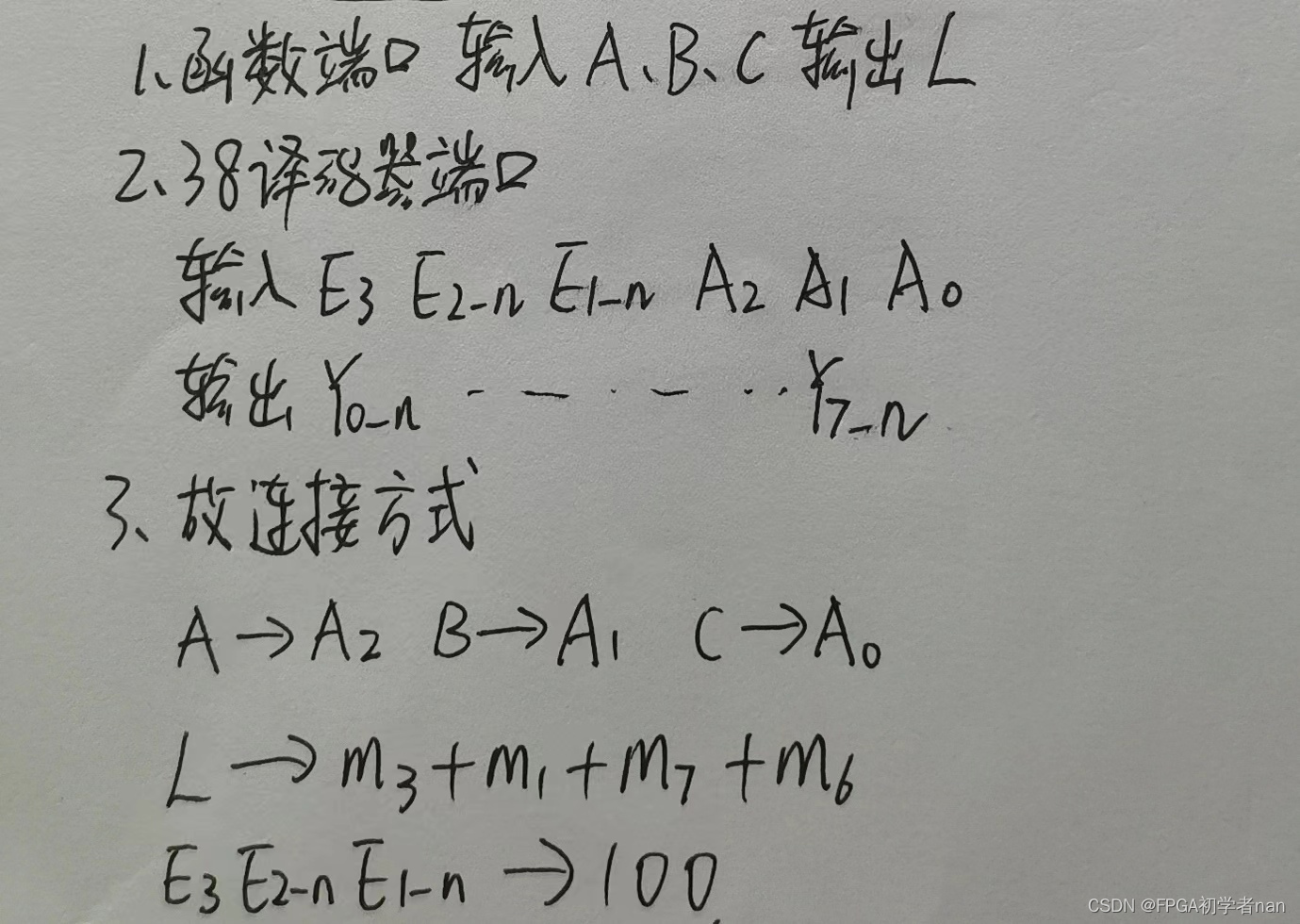

1、函数 L=(~A)·C+A·B 写成最小项后如下

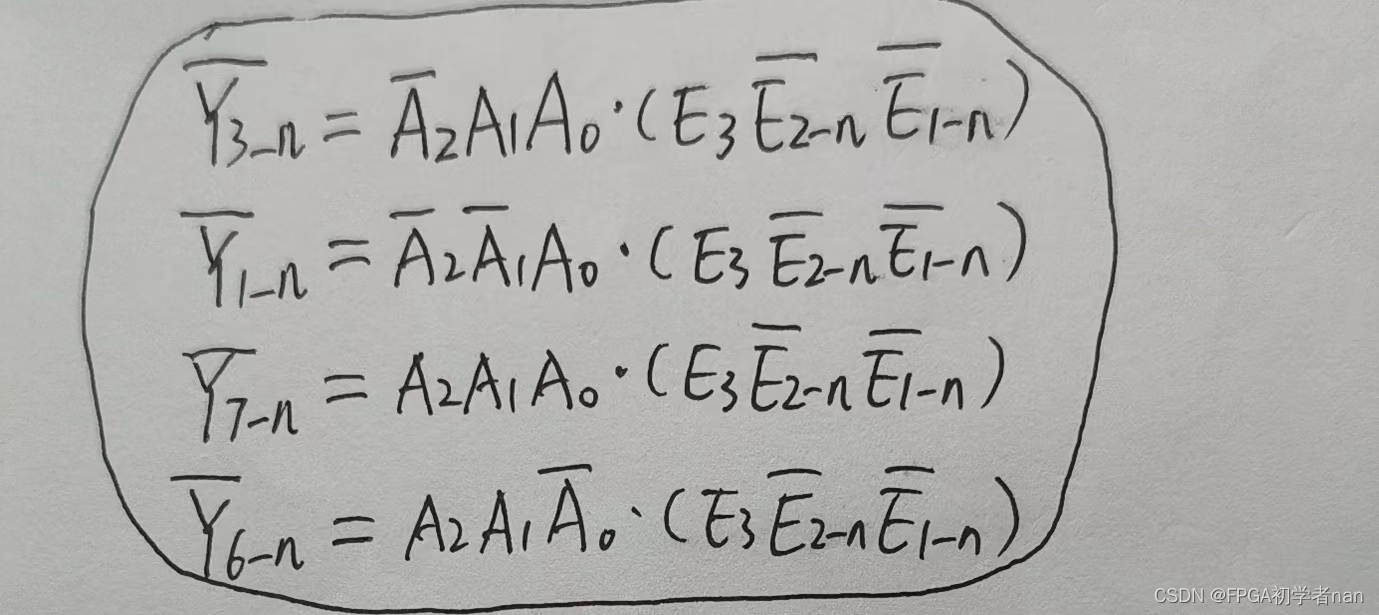

2、接着把38译码器的输出用最小项表示出来

注意,

38译码器只有在正常工作时的输出才是最小项,所以使用最小项时,38译码器的使能端必须是正常工作时的值。即 E3 E2_n E1_n 的值是 1 0 0 表示译码器正常工作。

是把38译码器的输出用最小项表示出来,而不是把38译码器的输出通式表达出来,38译码器的输出通式如下,这个通式是指包括译码器不正常工作时的的状态,但是这个通式不是最小项。所以即使这个表达式没有问题,但是对实现题目的函数功能没有用。

3、根据38译码器的端口和函数模块的端口,进行连接。38译码器和函数模块的输入端可以对应上,但是函数模块只有一个输出,而38译码器有多个输出。所以需要用导线把38译码器的输出端引出,再经过逻辑门接到函数模块的输出端。

4、代码

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

wire Y0_nw,Y1_nw,Y2_nw,Y3_nw,Y4_nw,Y5_nw,Y6_nw,Y7_nw;

decoder_38 decoder_38_inst(

.E1_n(1'b0) ,

.E2_n(1'b0) ,

.E3(1'b1) ,

.A0(C) ,

.A1(B) ,

.A2(A) , //好像端口可以直接和端口相接

//只不过38译码器和 函数模块没有相应的输出接口

//所以需要另外声明导线引出来38译码器的输出

.Y0_n(Y0_nw) , //然后当作函数输出

.Y1_n(Y1_nw) ,

.Y2_n(Y2_nw) , //38译码器端口引出导线

.Y3_n(Y3_nw) ,

.Y4_n(Y4_nw) ,

.Y5_n(Y5_nw) ,

.Y6_n(Y6_nw) ,

.Y7_n(Y7_nw)

);

assign L = ~Y3_nw | ~Y1_nw | ~Y7_nw | ~Y6_nw; //用引出的导线加逻辑门后接到

//函数的输出端

endmodule

文章描述了如何利用3-8译码器和必要的逻辑门来实现逻辑函数L=(~A)·C+A·B。首先将函数转换为最小项,然后分析3-8译码器在正常工作状态下的输出,接着将3-8译码器的输出与所需函数连接,最后展示了一个VHDL/Verilog代码示例,展示了如何实例化3-8译码器并连接逻辑门以得到最终的函数输出。

文章描述了如何利用3-8译码器和必要的逻辑门来实现逻辑函数L=(~A)·C+A·B。首先将函数转换为最小项,然后分析3-8译码器在正常工作状态下的输出,接着将3-8译码器的输出与所需函数连接,最后展示了一个VHDL/Verilog代码示例,展示了如何实例化3-8译码器并连接逻辑门以得到最终的函数输出。

1803

1803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?