t_slack (建立时间余量)=要求到达时间 - 实际到达时间

t_hd_slack(保持时间余量)=实际撤销时间-要求撤销时间

决定时钟跑的快慢只和建立时间余量有关

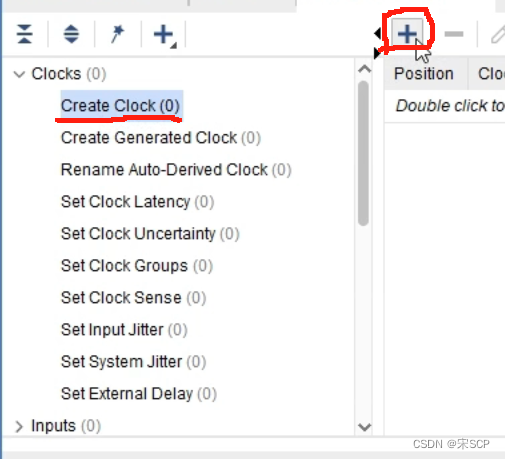

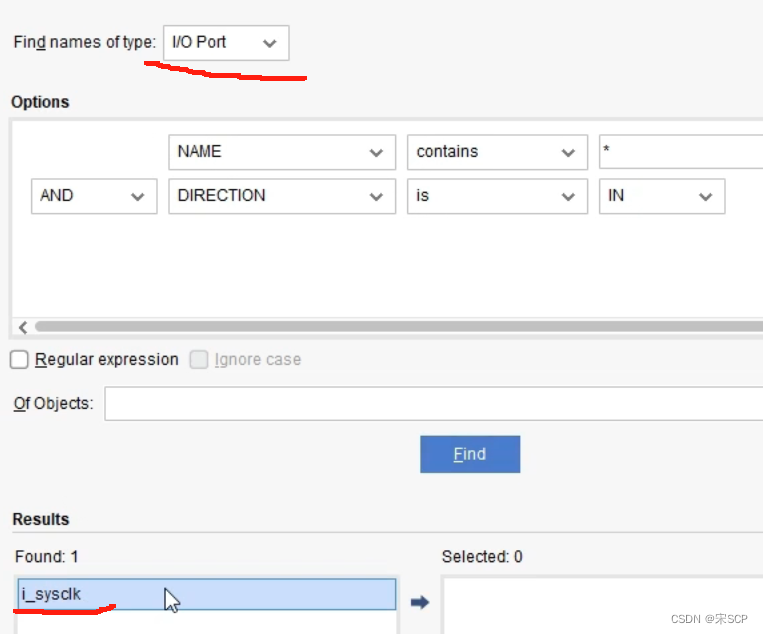

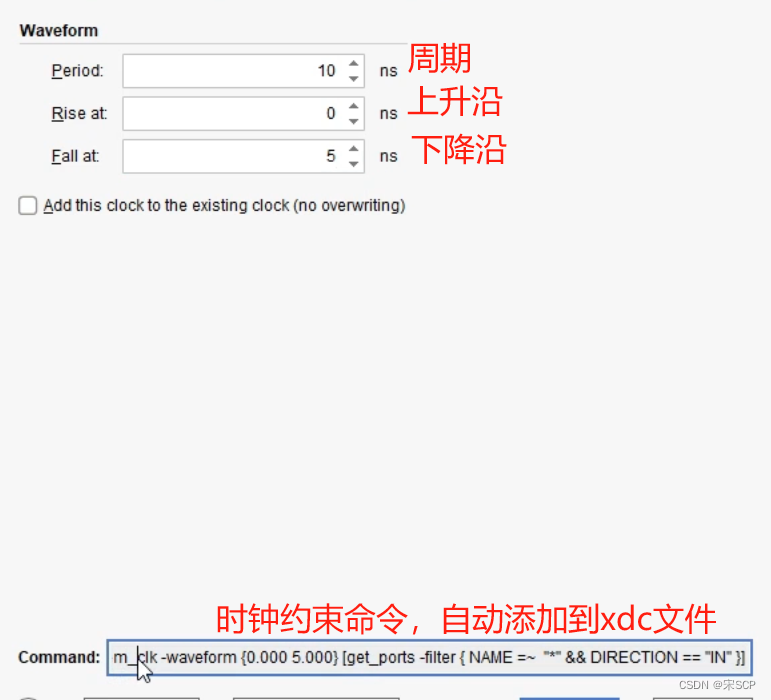

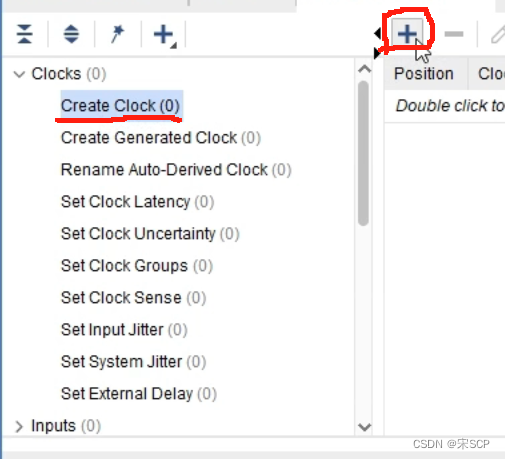

编辑时序约束

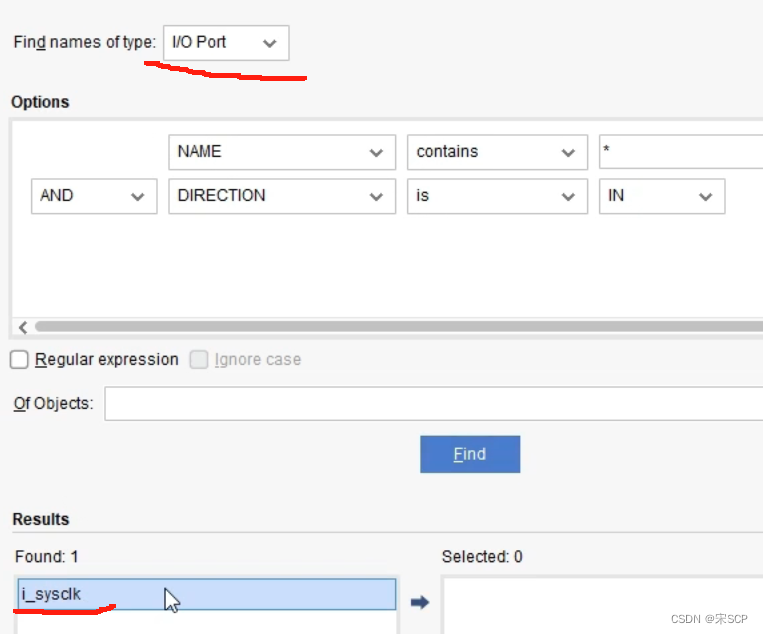

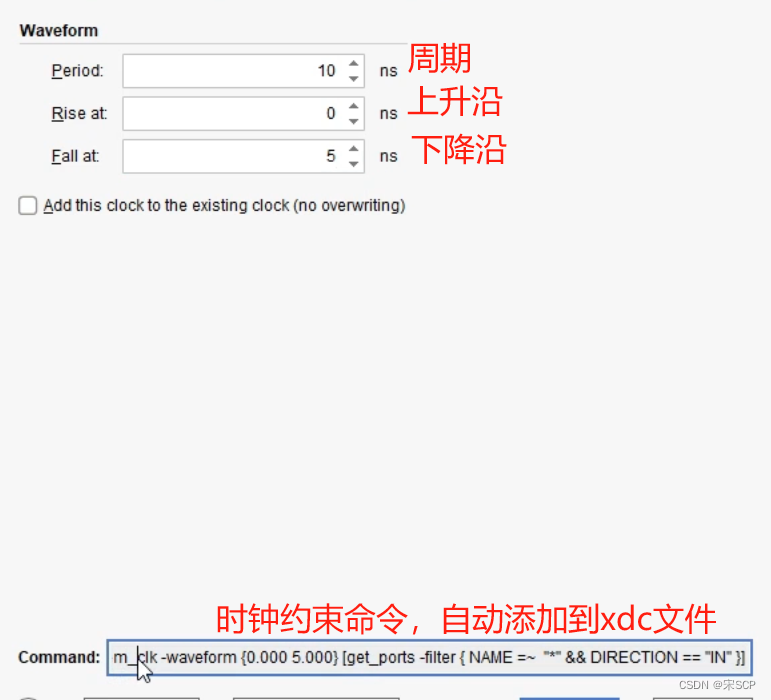

源时钟约束,创建

本文探讨了在编辑过程中,建立时间余量(t_slack)和保持时间余量(t_hd_slack)如何影响时钟的速度,以及源时钟约束在创建时序中的作用。

本文探讨了在编辑过程中,建立时间余量(t_slack)和保持时间余量(t_hd_slack)如何影响时钟的速度,以及源时钟约束在创建时序中的作用。

t_slack (建立时间余量)=要求到达时间 - 实际到达时间

t_hd_slack(保持时间余量)=实际撤销时间-要求撤销时间

决定时钟跑的快慢只和建立时间余量有关

编辑时序约束

源时钟约束,创建

2560

2560

1052

1052

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?