建立时间:tsu 保持时间:thd

跨时钟域问题,高速ADC传入低速UART,在时钟上升沿到来之前数据应该tsu时间前来才能成功赋值,并且在保持时间thd之后才能撤销。否则出现问题xxxxx亚稳态。

解决办法:跨时钟处理

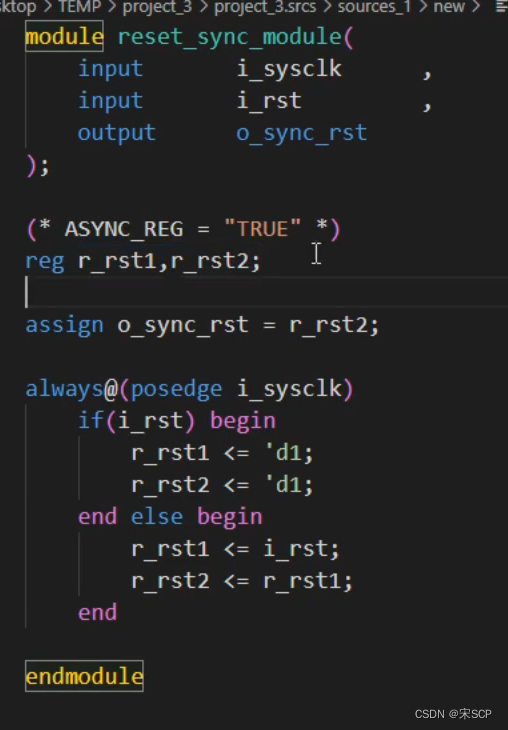

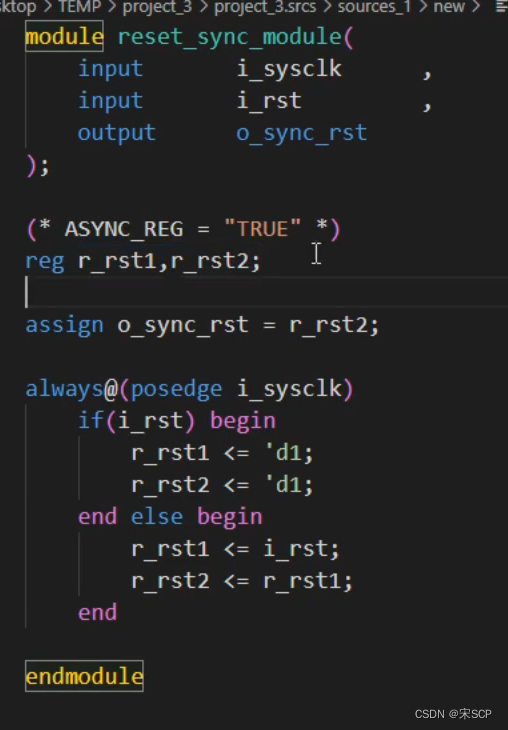

1。异步赋值,同步释放

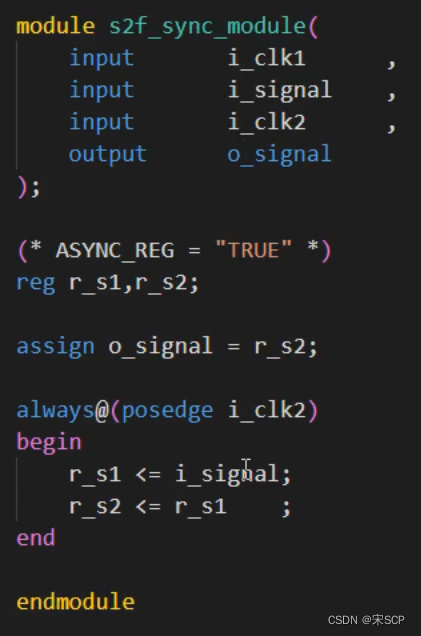

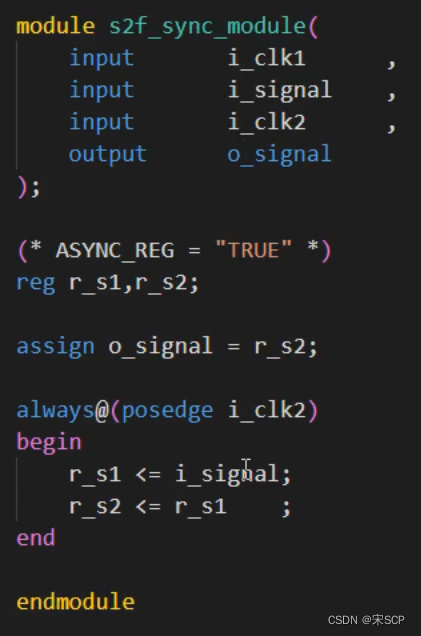

2.慢时钟域到快时钟域(单bit)

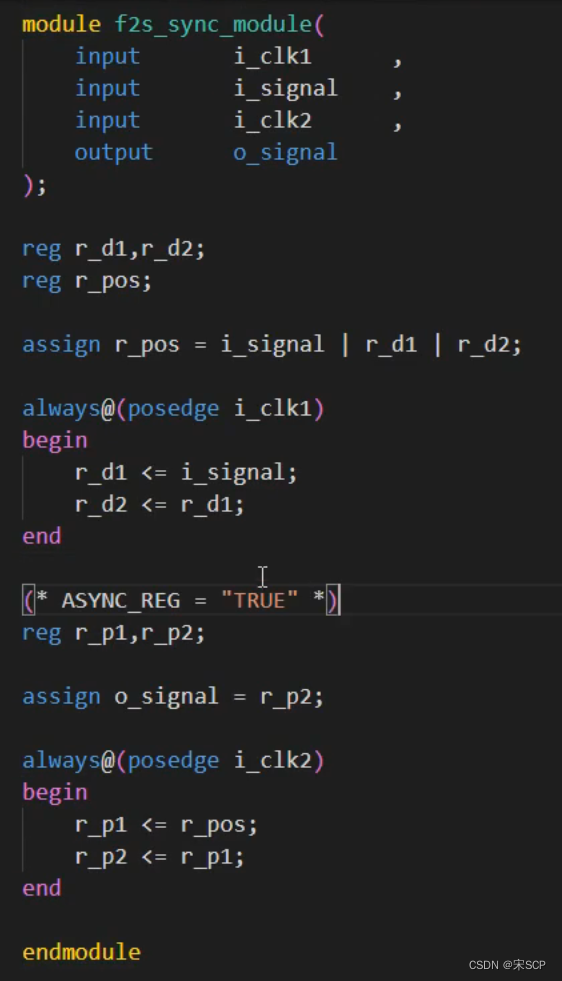

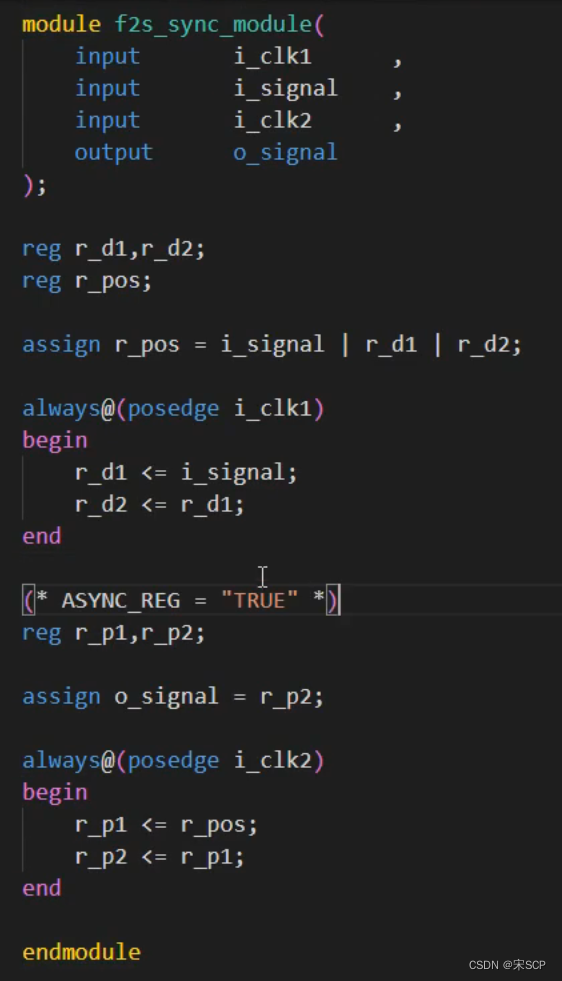

3快时钟域到慢时钟域(单bit)

FPGA跨时钟域学习笔记

最新推荐文章于 2024-07-20 15:32:35 发布

建立时间:tsu 保持时间:thd

跨时钟域问题,高速ADC传入低速UART,在时钟上升沿到来之前数据应该tsu时间前来才能成功赋值,并且在保持时间thd之后才能撤销。否则出现问题xxxxx亚稳态。

解决办法:跨时钟处理

1。异步赋值,同步释放

2.慢时钟域到快时钟域(单bit)

3快时钟域到慢时钟域(单bit)

1万+

1万+

9527

9527

1052

1052

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?