一、

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。

在QuartusII的一个培训文档里面解释了什么时候要用到FALSE PATH:

1. 从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。

2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径。

二、

芯片接口的三态数据总线实现时在芯片顶层把三态数据总线转为单向的两组总线

三、

同步复位在时钟沿采复位信号,完成复位动作

异步复位不管时钟,只要复位信号满足条件,就完成复位

异步复位对复位信号要求比较高,不能有毛刺

异步复位也需要同步到对应的时钟域,以便后续STA分析

四、多周期路径

多周期路径的约束语法为:

set_multicycle_path <path_multiplier> [-setup|-hold] [-start|-end] [-from <startpoints>] [-to <endpoints>] [-through <pins|cells|nets>]

set_multicycle_path N -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path N-1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

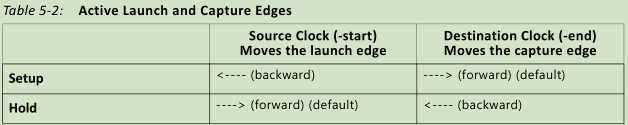

| 参数名称 | 含义 |

|---|---|

| -setup | 表示分析建立时间所需要移动的时钟周期个数 |

| -hold | 表示分析保持时间时,相较于设置了setup后默认的hold check edge,实际hold check edge偏差的时钟周期个数 |

| -start | 表示以目的端时钟作为时钟周期计数基准 |

| -end | 表示以源端时钟作为时钟周期的计数基准 |

active launch edge和capture edge的移动:

默认的检查规则为:

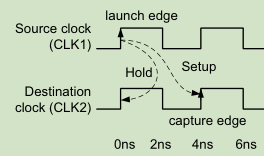

set_multicycle_path 1 -setup -end -from [get_clocks s_clk] -to [get_clocks d_clk]

set_multicycle_path 0 -hold -start -from [get_clocks s_clk] -to [get_clocks d_clk]

setup和-end搭配使用,hold和-start搭配使用,如图所示:

一旦确定建立时间路径,保持时间路径会自动根据规则做调整。如果保持时间想要回到原来的位置,则需要添加-hold的约束。

1、同一时钟域的多周期路径

当数据逻辑较为复杂,延时较大时,使得数据无法在一个时钟周期内稳定下来或是需要将数据发送几个周期后才使用。一般会使用时钟使能控制数据捕获,如图所示:

本文详细介绍了时序分析中的FALSE PATH概念,强调了在不同场景下使用FALSE PATH的原因。接着讨论了同步复位和异步复位的区别,并深入探讨了多周期路径的约束设置,包括在同一时钟域、相同时钟周期但有相移、从慢时钟到快时钟以及从快时钟到慢时钟的情况。最后,文章提到了时序裕度在同步电路设计中的重要性。

本文详细介绍了时序分析中的FALSE PATH概念,强调了在不同场景下使用FALSE PATH的原因。接着讨论了同步复位和异步复位的区别,并深入探讨了多周期路径的约束设置,包括在同一时钟域、相同时钟周期但有相移、从慢时钟到快时钟以及从快时钟到慢时钟的情况。最后,文章提到了时序裕度在同步电路设计中的重要性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3018

3018

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?