一、阻抗

- 阻抗 定义为 Z = V / I , 当信号沿着互连传播时,它将不断探测互连的阻抗并作出反应,如果知道了互连的阻抗和传播时延,就几乎知道了所有的电气特性。

- 理想电阻器的阻抗是恒定的 Z = R

- 理想电容器的阻抗 Z = V / (C * dV / dt)

*电容器的电流并不是传导电流,而是位移电流,在电介质中可以视为 电场发生改变引起的束缚电荷极化增大或减小时,出现的电荷移动。即电容器极板上电压改变造成的电介质束缚电荷发生位移因而产生电流。

大电容意味着低电压能储存大电量。

频域中电容器的阻抗 Z = 1/(wC) --这里谈论阻抗一般只关心阻抗的幅值

电容器的阻抗会随着频率的增大而减小。 - 理想电容器的阻抗 Z = L * (dI / dt ) / I

如果流过电感器的电流迅速增加或减少,阻抗很大,;如果流过的电流变化微弱,则阻抗很小。流电流,电感器的阻抗近似为0。

大电感意味着电流的微小变化能产生大电压。

电感会产生感应电压,流进电流持续增加的那一端是感应电压的正极。

频域中电感器的阻抗 Z = wL

电感器的阻抗会随着频率的增大而增大。 - 给出电路元件怎样连接在一起称为拓扑结构;确定每个电路元件的值称为参数值和寄生值。

确定互连参数值的过程称为寄生参数提取。

二、电阻

-

方块电阻 R = ρ L t × w = ( ρ t ) × ( L w ) R=\rho\frac L{t\times w}=(\frac\rho t)\times(\frac Lw) R=ρt×wL=(tρ)×(wL)

第一项, (ρ/t) ,对于该层上厚度为 t 的所有线条来说,是个常数。在同一层上的所有线条都有相同的体电阻率和相同的厚度。第二项,(L/w) 表示具体线条的长宽比值,代表能划分的方块数目。方块电阻的单位是 Ω ,也即无论边长是多少,同样材料和厚度构成的正方形导体片 任意侧端面之间的电阻值是一样的。 -

1oz 的铜表示的是电路板铜层 1平方英尺 的重量为 1oz = 28.3495 g。1oz铜厚为35um,0.5oz的铜厚为17.5um。

0.5oz 的方块电阻为1 mΩ / sq , 5mil宽,5 in长的线条可以划分为1000个串联的方块,因此电阻值是1Ω。

三、电容

-

电容器是两个导体构成的,任意两个导体之间都有一定的电容量。

-

去耦电容的例子为了减少电源供电系统的电压轨道塌陷,在电源和地之间设计去耦电容,从而在 t 时间内,电容C可以阻止电源电压的下沉。电源轨道上电流消耗的指标是功耗,因为功耗等于电流和电压乘积。 芯片的功耗为P,那么电流为 I = P / V ,因为去耦电容的作用,电压下沉达到电源电压的 5% 所需要的时间为

δ t = C × 0.05 × V 2 P \delta t = C \times0. 05 \times\frac{V^2}{P} δt=C×0.05×PV2

芯片功耗为 1W,电源电压为3.3V 时,1nF 的去耦电容,能提供的去耦时间为 0.5ns。时间比较短,因此这个时候需要更大的电容量,一般需要5us的时间,即需要10uF的电容。 -

估算电源和地平面之间的去耦电容

C = ε 0 ε r A h C = \varepsilon_0\varepsilon_\text{r}\frac Ah C=ε0εrhA

其中 ε r \varepsilon_{\text{r}} εr 表示 FR4 的相对介电常数 4, ε 0 \varepsilon_{0} ε0表示自由空间的介电常数 0.225 pF/in 。

C = 0.225 p F / i n × 4 × 1 i n / h ≈ 1000 p F / h C=0.225 \mathrm{pF/in}\times4\times1 \mathrm{in/h}\approx1000 \mathrm{pF/h} C=0.225pF/in×4×1in/h≈1000pF/h

因此每平方英寸面积的、厚度为1 mil 的FR4材料电路板的电容为1 nF。显然,这个数值是比较小的,如果要提高单位inch面积的电容量,使用的介质需要有更薄的厚度和更高的相对介电常数。 -

大多数均匀互连都有固定的信号路径和返回路径,这样信号路径和返回路径的电容和路径长度成比例, C = C L × L e n C=C_{\mathrm{L}}\times\mathrm{Len} C=CL×Len,因此需要关注单位长度的电容。

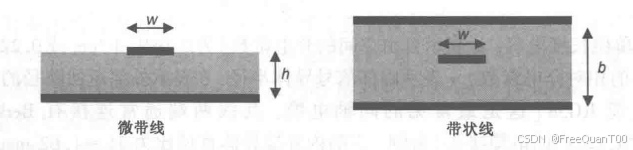

微带线的单位长度电容近似为:

C L = 0.67 ( 1.41 + ε r ) ln { 5.98 × h 0.8 × w + t } ≈ 0.67 ( 1.41 + ε r ) ln { 7.5 ( h w ) } C_{\mathrm{L}}=\frac{0.67(1.41+\varepsilon_{\mathrm{r}})}{\ln\left\{\frac{5.98\times h}{0.8\times w+t}\right\}}\approx\frac{0.67(1.41+\varepsilon_{\mathrm{r}})}{\ln\left\{7.5\left(\frac{h}{w}\right)\right\}} CL=ln{0.8×w+t5.98×h}0.67(1.41+εr)≈ln{7.5(wh)}0.67(1.41+εr)

微带线线宽w一般是介质厚度h的两倍,w=2h,计算得 C L = 2.7 p F / i n C_{\mathrm{L}}=2.7\mathrm{pF/in} CL=2.7pF/in。

带状线的单位长度电容近似为:

C L = 1.4 ε r ln { 1.9 × b 0.8 × w + t } ≈ 1.4 ε r ln { 2.4 ( b w ) } C_\mathrm{L} = \frac{1.4\varepsilon_\mathrm{r}}{\ln\left\{\frac{1.9\times b}{0.8\times w+t}\right\}}\approx\frac{1.4\varepsilon_\mathrm{r}}{\ln\left\{2.4\left(\frac{b}{w}\right)\right\}} CL=ln{0.8×w+t1.9×b}1.4εr≈ln{2.4(wb)}1.4εr

带状线线宽w一般是介质厚度h的1/2,w=0.5h,计算得 C L = 3.5 p F / i n C_{\mathrm{L}}=3.5\mathrm{pF/in} CL=3.5pF/in。

四、电感

- 电感是对表面磁场强度的数值积分:

L

=

1

I

∫

a

r

e

a

B

→

⋅

n

^

d

a

L = \frac{1}{I}\int_{\mathrm{area}}\overrightarrow{B} \cdot \hat{n}\mathrm{d}a

L=I1∫areaB⋅n^da。用于度量电感的单位是流过1A电流时,周围磁力线圈的韦伯值。1Wb/A = 1 H(亨利)。流过导体的电流加倍,磁力线圈数加倍,但比值不变,因此无论是1A还是100A,电感的数值是不变的。电感只和导体的几何结构有关,表征导体产生磁力线圈的效率。

L = N I L = \frac{N}{I} L=IN

电感是关于每安培电流周围磁力线匝数的度量,而不是某一点磁场强度的绝对值。

-

为了分清形成磁力线圈的源头,引入了自感和互感这两个术语。当计算一条导线周围的磁力线圈时,需要有一种方式表明磁力线圈的源头。把一条导线自身电流产生的磁力线圈称为自磁力线圈,把由邻近电流产生的磁力线圈称为互磁力线圈。一般称线圈的自感为电感。如果电流方向相同,第一条导线周围的磁力线总数就等于其自磁力线匝数加上互磁力线匝数。如果电流方向相反,第一条导线周围的磁力线总数就等于其自磁力线匝数中减去互磁力线匝数。

-

互感是指一条导线中流过单位安培电流时,所产生的环绕在另一条导线周围的磁力线匝数。互感是两个导线共有的特性,互感是对称的,互感的产生与两个导线的结构都相关,所以是两个导线之间的互感。无论从两个导线的任意一方去测量互感的数值都是相同的,而且测得的互感数值一定小于任意一个的自感数值。

-

如果导线的电流变化,导线周围的磁力线圈匝数也会变化,进而导线两端就会产生一个感应电压,电压的大小与变化的快慢有关。这一电压也被称为感应电动势 EMF,电压的极性阻碍原电流的变化。

V = Δ N Δ t = Δ L I Δ t = L d I d t V = \frac{\Delta N}{\Delta t} = \frac{\Delta LI}{\Delta t} = L \frac{\mathrm{d}I}{\mathrm{d}t} V=ΔtΔN=ΔtΔLI=LdtdI

感应电压正是电感在信号完整性中意义重大的根本原因。如果电流变化时没有产生感应电压,信号就不会受到电感的影响。这个由电流变化产生的感应电压引起了传输线效应、突变、串扰、开关噪声、轨道塌陷、地弹和大多数电磁干扰源。

- 两条相邻导线,其中一条电流变化时,另一条导线的磁力线数会发生变化,产生感应电压。这个电压噪声可以用互感描述: V n o i s e = M d I d t V_{\mathrm{noise}} = M \frac{\mathrm{d}I}{\mathrm{d}t} Vnoise=MdtdI。

- 局部电感,计算局部电感时假设导线的其他部分不存在,只有所研究的一段导体存在电流。对于简单形状的导体,局部电感存在近似公布公式。如直圆杆导线的自感可以用如下公式近似 L = 5 Len { ln ( 2 Len r ) − 3 4 } L = 5\text{Len}\Big\{\ln\Big(\frac{2\text{Len}}{r}\Big)-\frac{3}{4}\Big\} L=5Len{ln(r2Len)−43},两条直圆导线的互感可以用 M = 5 Len { ln ( 2 Len s ) − 1 } M = 5\text{Len}\Big\{\ln\Big(\frac{2\text{Len}}{s}\Big)- 1\Big\} M=5Len{ln(s2Len)−1} 近似。对于常见的30AWG的导线,半径5mil,线长度1inch时,局部自感是 25 nH。但导线长度加倍时,局部电感会加大,但不止两倍,因为还存在其他段的互感。而且,截面积越小,电流分布越密集,互感越大。 该公式同样适用于过孔,例如一个深度为64mil的过孔局部自感为 25 n H / i n × 0.064 i n = 1.6 n H ∘ 25\mathrm{~nH/in}\times0.064\mathrm{~in}=1.6\mathrm{~nH}_\circ 25 nH/in×0.064 in=1.6 nH∘。也可以看出局部互感随间距的增大而减小,当两个导线距离大于线段长度的时候,局部互感就可以忽略不计了。

30AWG导线的局部自感约等于25nH / inch 或者 1nH / mm

- 电感和地弹

支路a和支路b的电流方向相反,自感和互感反向,那么单个支路的总电感即是自感和互感的差值。

N t o t a l = N b − N a b = ( L b − L a b ) I N_{\mathrm{total}} = N_{\mathrm{b}} - N_{\mathrm{ab}} = ( L_{\mathrm{b}} - L_{\mathrm{ab}} ) I Ntotal=Nb−Nab=(Lb−Lab)I

如果第二条路径是返回路径,那么称该返回路径上的电压为地弹。则返回路径的地弹电压降为:

V g b = L t o t a l d I d t = ( L b − L a b ) d I d t V_{\mathrm{gb}} = L_{\mathrm{total}} \frac{\mathrm{d}I}{\mathrm{d}t} = ( L_{\mathrm{b}} - L_{\mathrm{ab}} ) \frac{\mathrm{d}I}{\mathrm{d}t} Vgb=LtotaldtdI=(Lb−Lab)dtdI

由此也可以看出,减小地弹电压降则需要减小电流变化率或者减小自感或增大互感。一般后者可以通过使用短而宽的互连降低自感,使信号电流和返回路径尽可能靠近以增大互感。

第二种电容器过孔布局更好些。每个电容器焊盘使用多个过

孔并联,并联的过孔数目越多,等效电感就越少,而且电源和地平面的接触面积加大,扩散电感也会减小。

采用下述设计规则可以使每条支路的净电感最小:电流方向相同的过孔之间的中心距应大于过孔的长度,电流方向相反的过孔之间的中心距应小于过孔的长度。

- 回路自感:沿着导线行走时遇到的回路中所有电流产生的磁力线总数。简化的回路电感可以用两条支路的净电感计算:

L l o o p = L a − L a b + L b − L a b = L a + L b − 2 L a b L_\mathrm{loop} = L_\mathrm{a} - L_\mathrm{ab} + L_\mathrm{b} - L_\mathrm{ab} = L_\mathrm{a} + L_\mathrm{b} - 2L_\mathrm{ab} Lloop=La−Lab+Lb−Lab=La+Lb−2Lab - 电压轨道塌陷,当进入芯片的电流发生突变时,变化的电流流经电源分配网络的互连阻抗时会发生电压降。因此为了减小电压降,就要减小互联阻抗或者减小电流变化。

要使电源分配网络的阻抗比较小,有两条设计原则:低频时,添加具有低回路电感的去耦电容器;高频时,使去耦电容器和芯片焊盘之间的回路电感最小,以保持它们之间的阻抗低于一定的值。

去耦电容几乎对每个供电芯片都是必须的,例如,若存储器芯片或小型专用集成电路的工作电压为3.3V,容许的波动为5%,功耗的典型值为1W,则所需的去耦电容总量为

C

=

1

0.05

⋅

1

3.

3

2

Δ

t

=

2

Δ

t

C = \frac{1}{0. 05}\cdot\frac{1}{3. 3^{2}}\Delta t = 2\Delta t

C=0.051⋅3.321Δt=2Δt

如果稳压器在10us内无法做出反应,那么就需要提供20uf的去耦时间。小于这个数值,在这段时间内芯片的电压沉降就会大于5%。

去耦电容的两端和芯片焊盘相连的导线也有相应的回路电感,以下时0603电容的阻抗,

低频时阻抗随频率的增大而减小。随着频率的升高,从某一点起,串联的回路电感开始在阻抗中起主导作用。该点的频率称为自谐振频率此后阻抗开始增大。当频率大于自谐振频率时,电容器的阻抗与电容量完全无关,只与相应的回路电感有关。所以,频率较高时,如果想减小去耦电容器的阻抗,就要减小相关的回路电感,而不是靠增大电容量。所以一般去耦电容的布置需要有严格的要求,比如:电容靠近芯片引脚;电源和地平面尽量靠近;减小过孔深度;焊盘和过孔尽量近;多电容并联等。

486

486

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?