1 理论学习

2 实战演练 偶分频

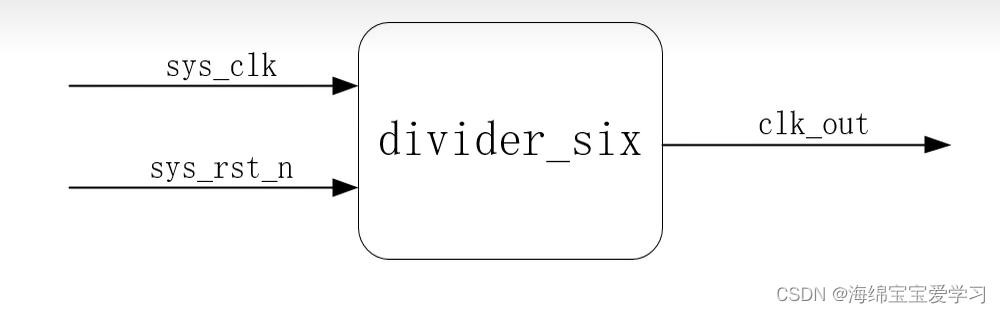

2.1 设计规划

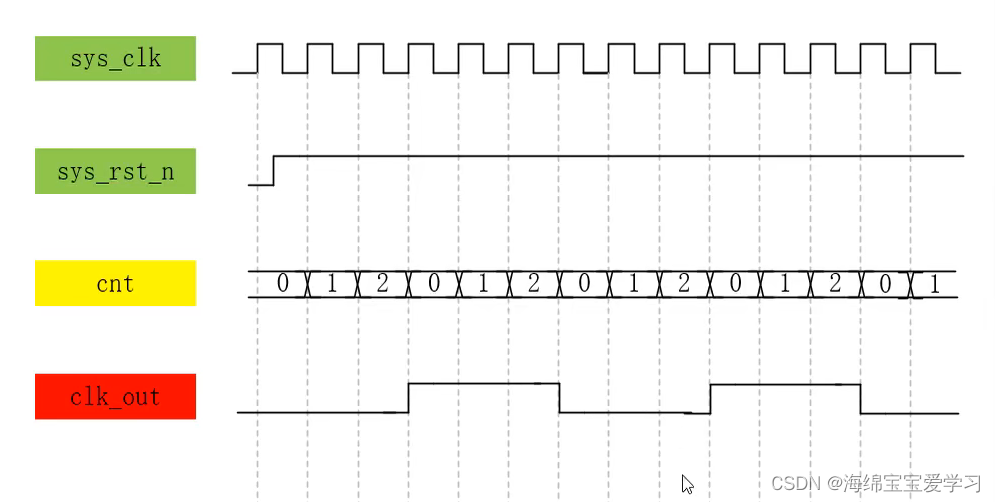

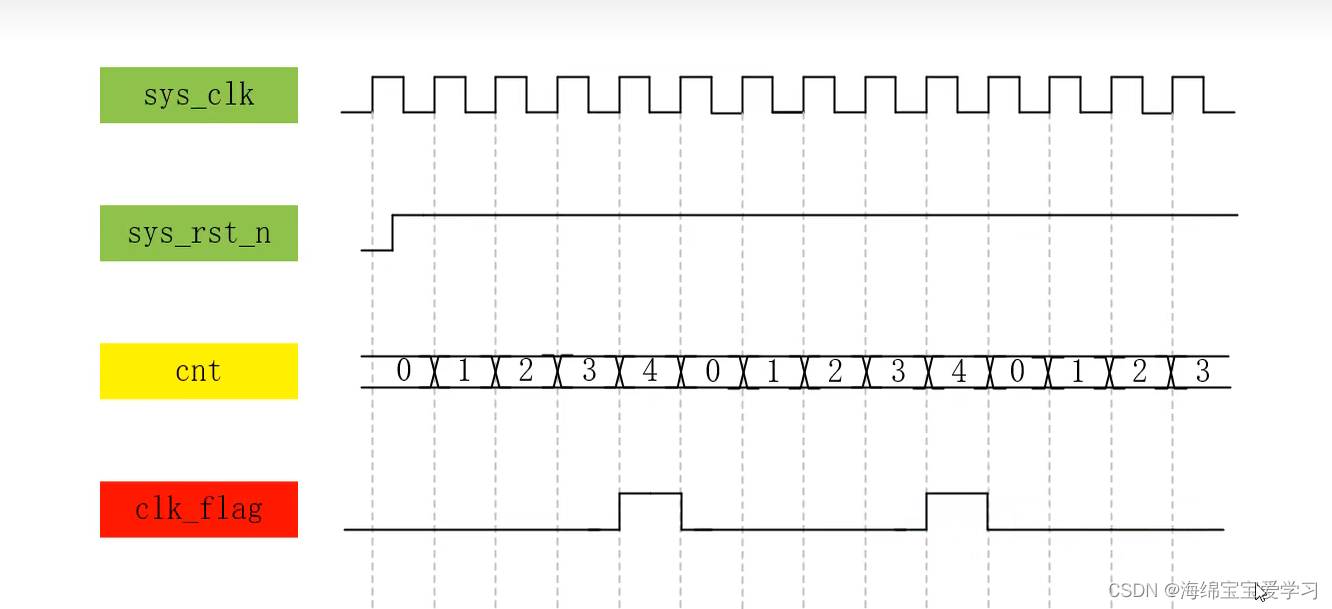

2.2 波形绘制

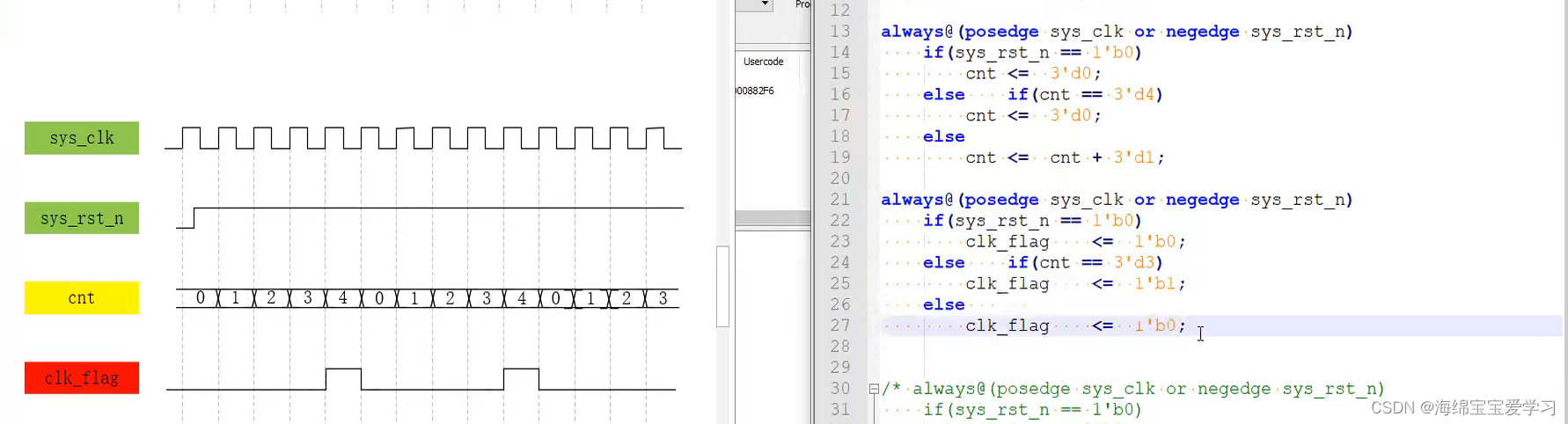

2.3 代码编写与调试

module divider_six

(

input wire sys_clk,

input wire sys_clk_n,

output wire clk_out

);

reg [1:0] cnt;

// 使用异步复位

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 2'd0;

else if(cnt == 2'd2)

cnt <= 2'd0;

else

cnt <= cnt + 1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_out <= 1'b0;

else if(cnt == 2'd2)

clk_out <= ~clk_out;

else

clk_out <= clk_out;

endmodule

tb_divder_six:

`timescale 1ns\1ns

module tb_divder_six();

// 1

reg sys_clk;

reg sys_rst_n;

wire clk_out;

// 2

initial begin

sys_clk <= 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

// 3

divider_six divider_six_inst

(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.clk_out(clk_out)

);

endmodule

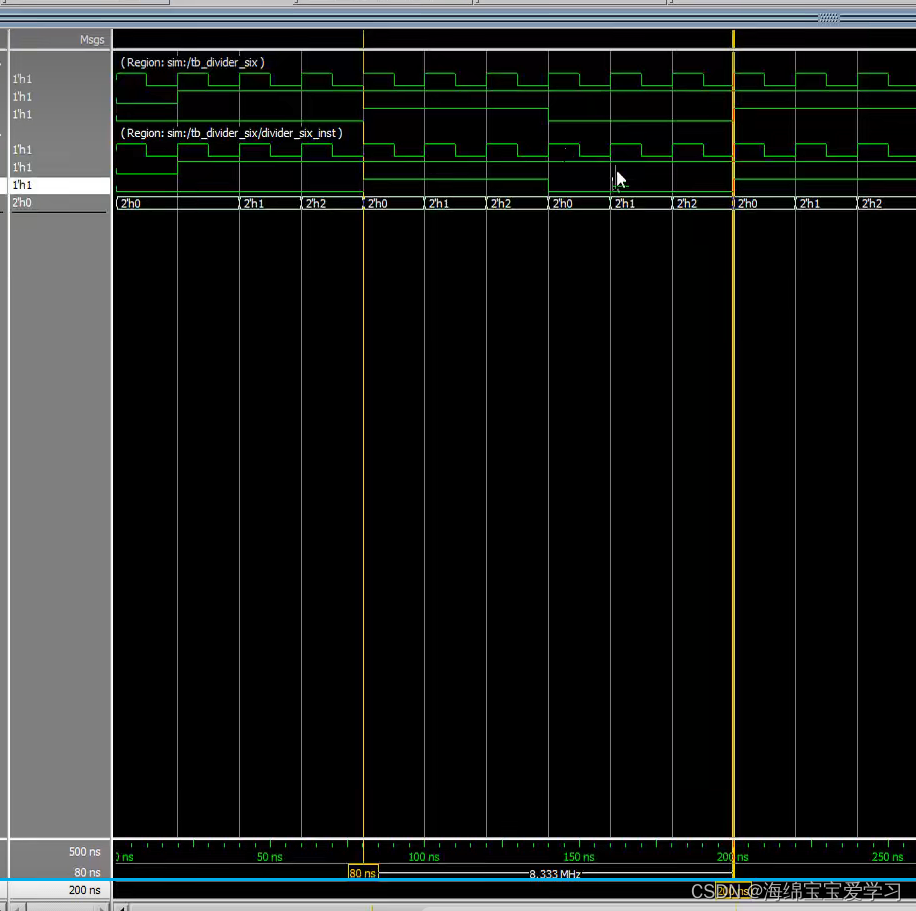

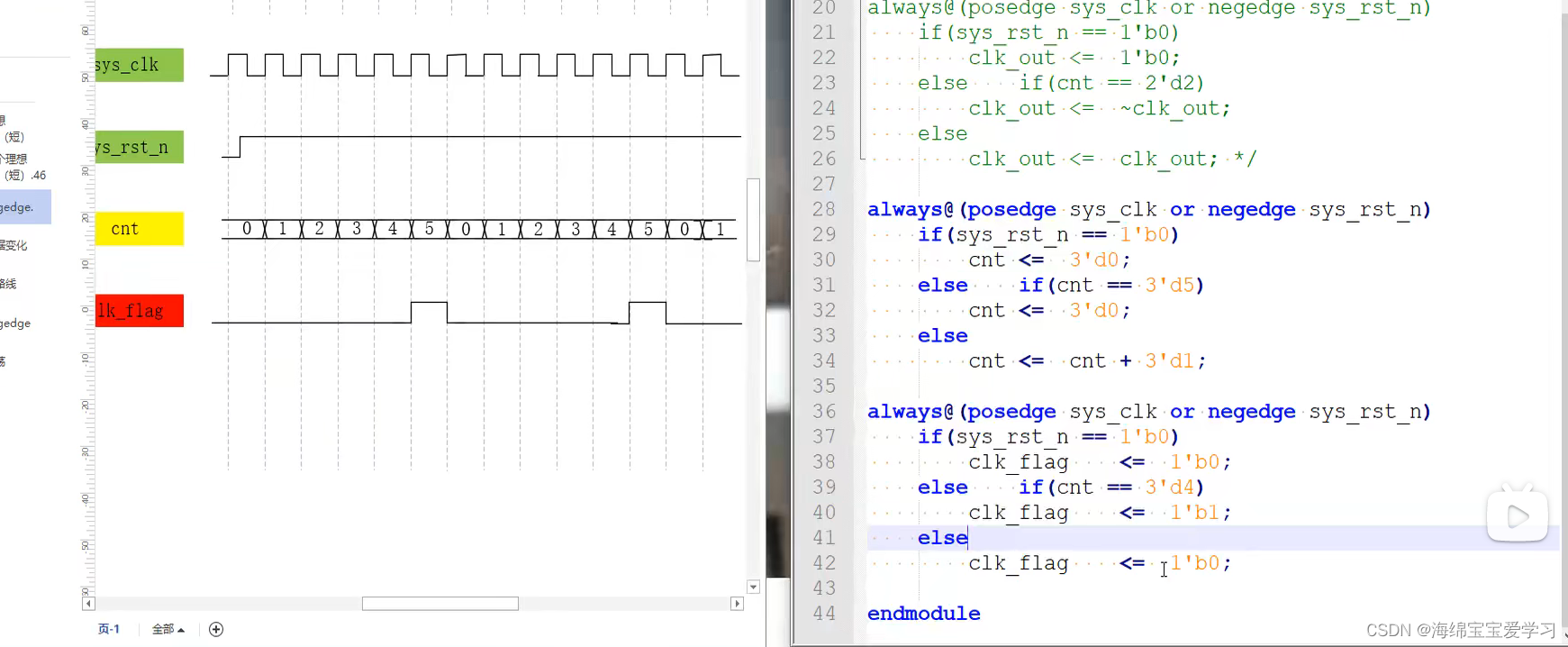

2.4 仿真验证和波形对比分析

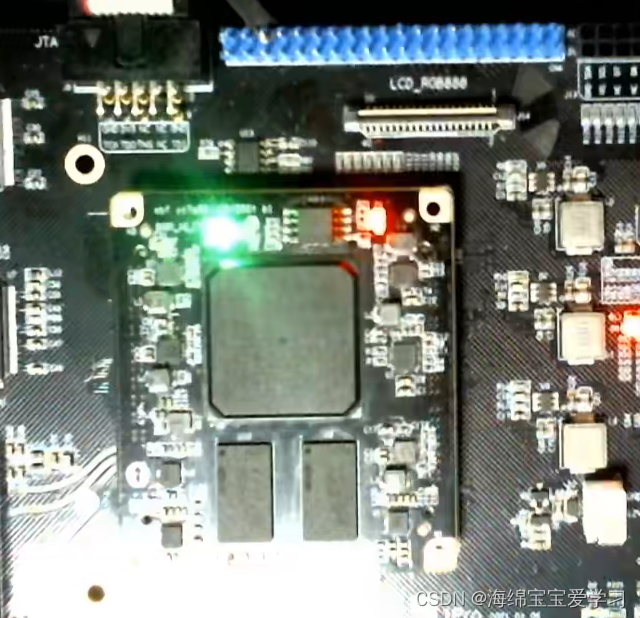

2.5 绑定管脚和上电

实现了六分频

2.6 问题改进(全局时钟数)

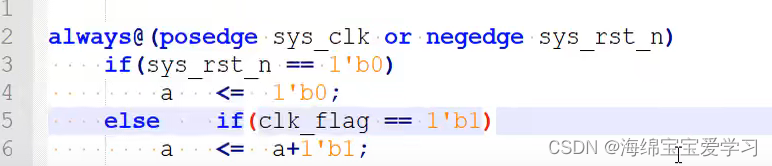

减少时序问题的产生,并没有连接到了时钟树。尽量使用系统时钟。联想到我们上一章的分频标志信号flag。改进代码

看上去与第一种只是占空比的不同

如果是赋值a:第一种。低频是可以的,但是高频不行

第二种:

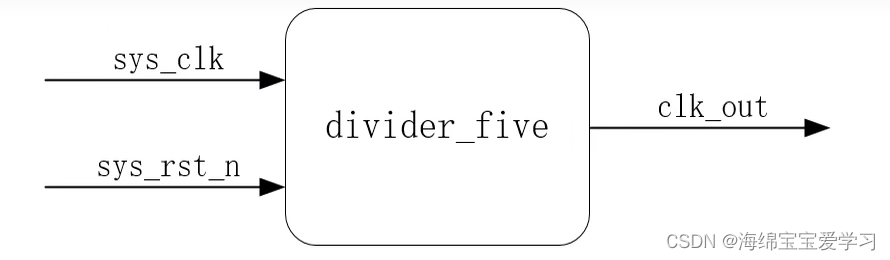

3 实战演练 奇分频

3.1 设计规划

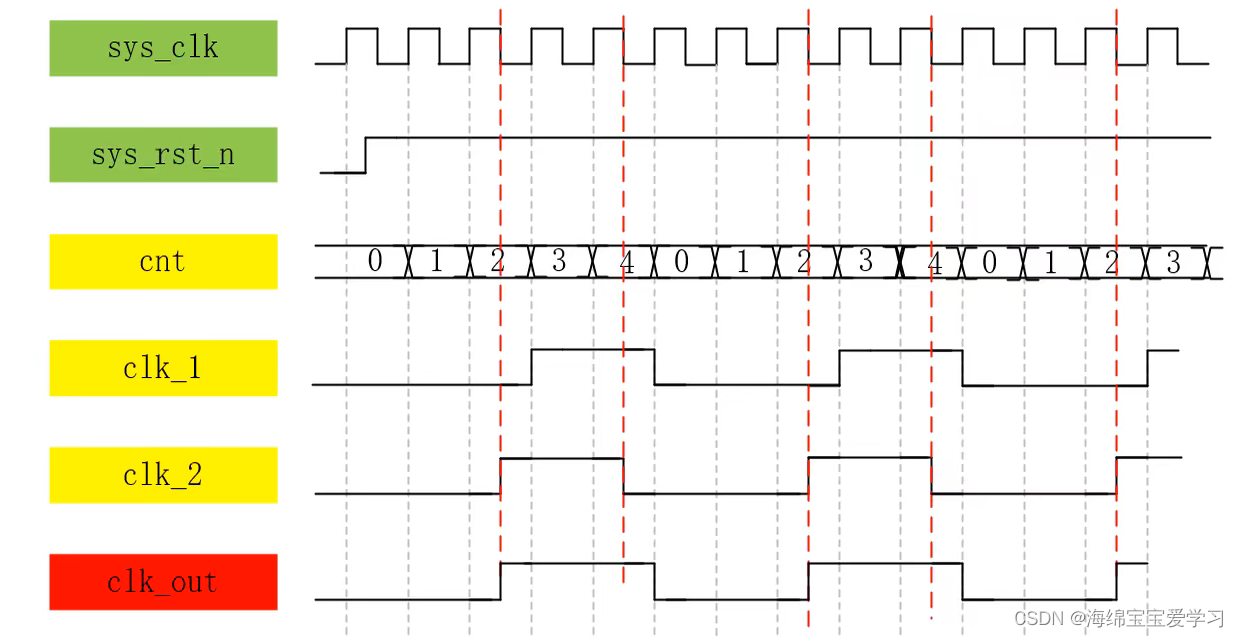

3.2 波形绘制

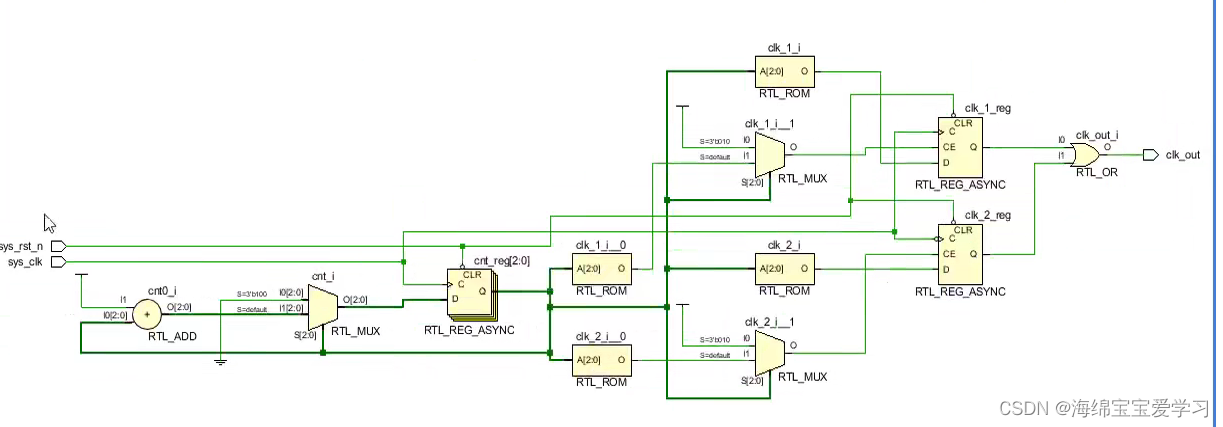

3.3 代码编写

module divder_five

(

input wire sys_clk,

input wire sys_rst_n,

output wire clk_out

);

reg [2:0] cnt;

reg clk_1;

reg clk_2;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt <= 3'd0;

else if(cnt == 3’d4)

cnt <= 3'd0;

else

cnt <= cnt + 1;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clk_1 <= 1'b0;

else if(cnt == 3'd2)

clk_1 <= 1'b1;

else if(cnt == 3'd4)

clk_1 <= 1'b0;

else

clk_1 <= clk_1 ;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clk_1 <= 1'b0;

else if(cnt == 3'd2)

clk_1 <= 1'b1;

else if(cnt == 3'd4)

clk_1 <= 1'b0;

else

clk_1 <= clk_1;

always@(negedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clk_2 <= 1'b0;

else if(cnt == 3'd2)

clk_2 <= 1'b1;

else if(cnt == 3'd4)

clk_2 <= 1'b0;

else

clk_2 <= clk_2;

assign clk_out = (clk_1 | clk_2);

endmodule

tb文件

`timescale 1ns\1ns

module tb_divder_dive();

// 1

reg sys_clk;

reg sys_rst_n;

wire clk_out;

// 2

initial begin

sys_clk <= 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

// 3

divider_five divider_five_inst

(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.clk_out(clk_out)

);

endmodule

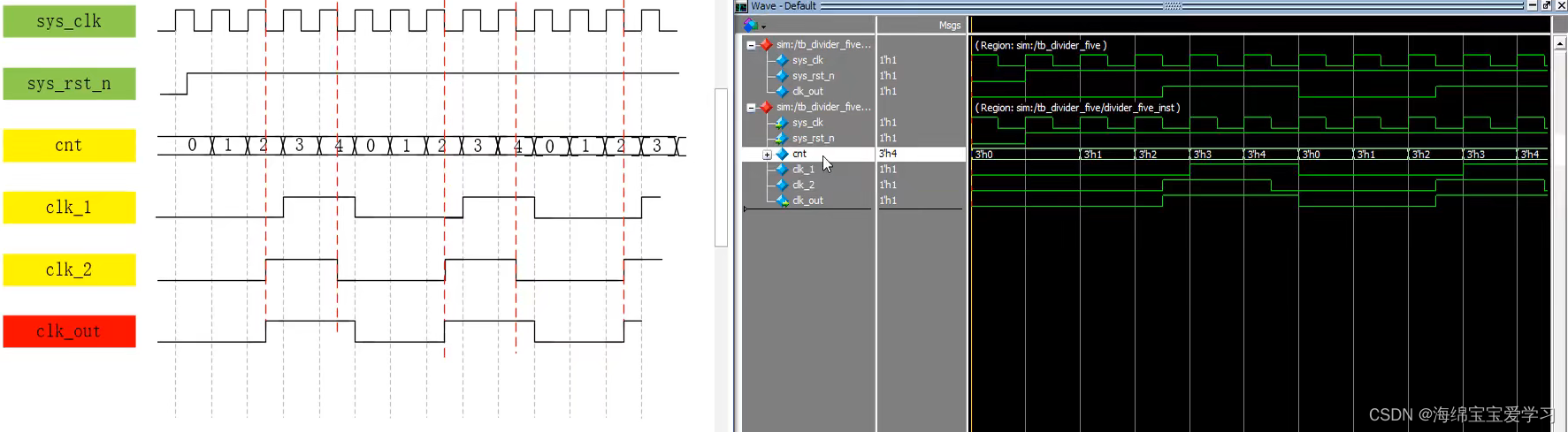

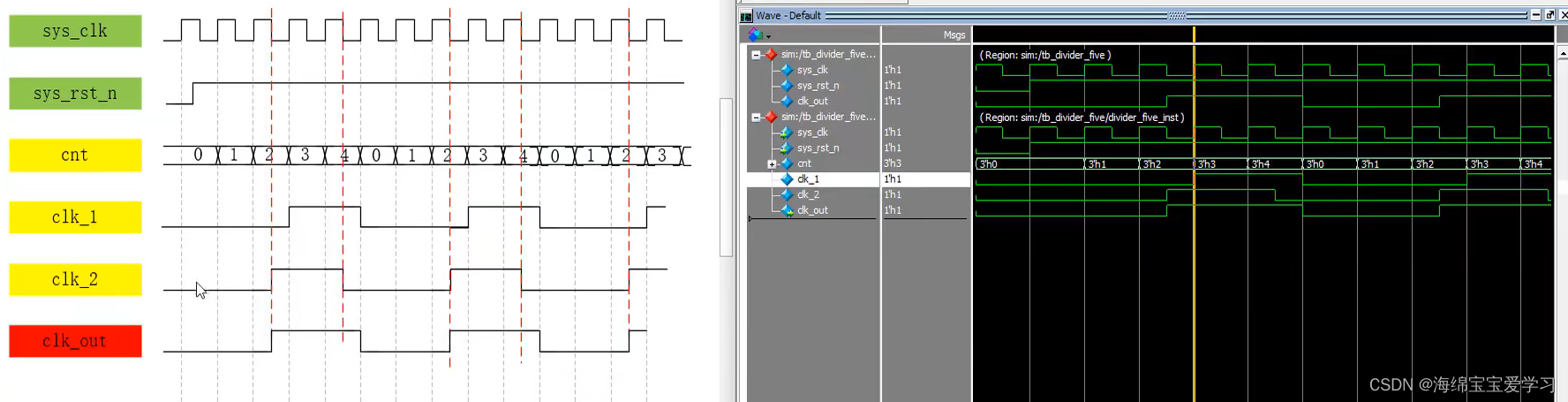

3.4 仿真波形与对比

3.5 使用降频的方法

1786

1786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?