时钟体系构架:

全局时钟树(Global clock tree)跨整个器件提供同步时钟。每个7系列单片设备有32条全局时钟线。

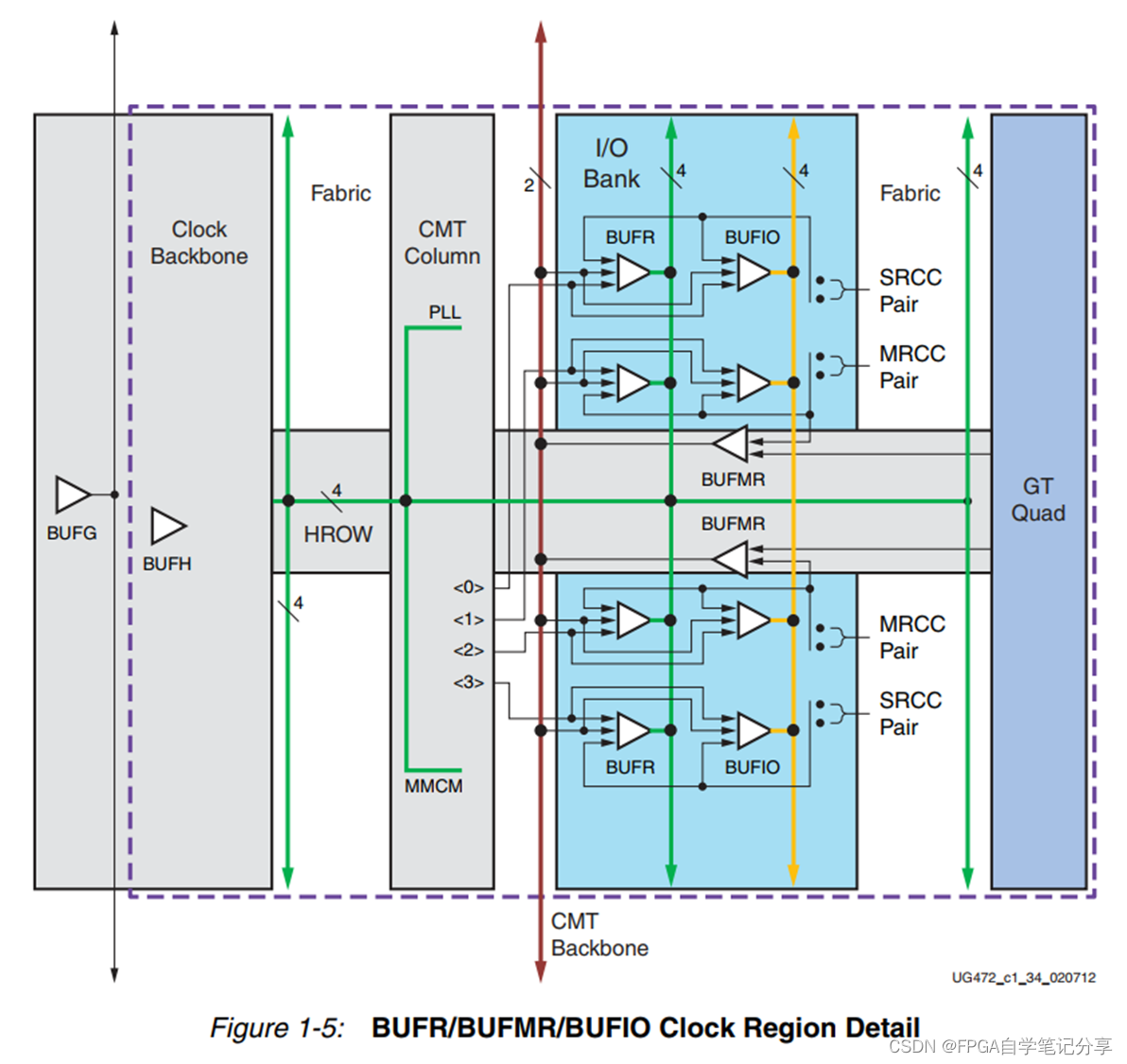

I/O 和 时钟域时钟树(regional clock tree)最多允许跨3个垂直相邻的时钟域,最多有24个时钟域。

CMT 含一个 混合模式时钟管理器(mixed-mode clock manager ,MMCM) 和一个 锁相环(phase-locked loop,PLL)。CMT 列与 I/O 列相邻。

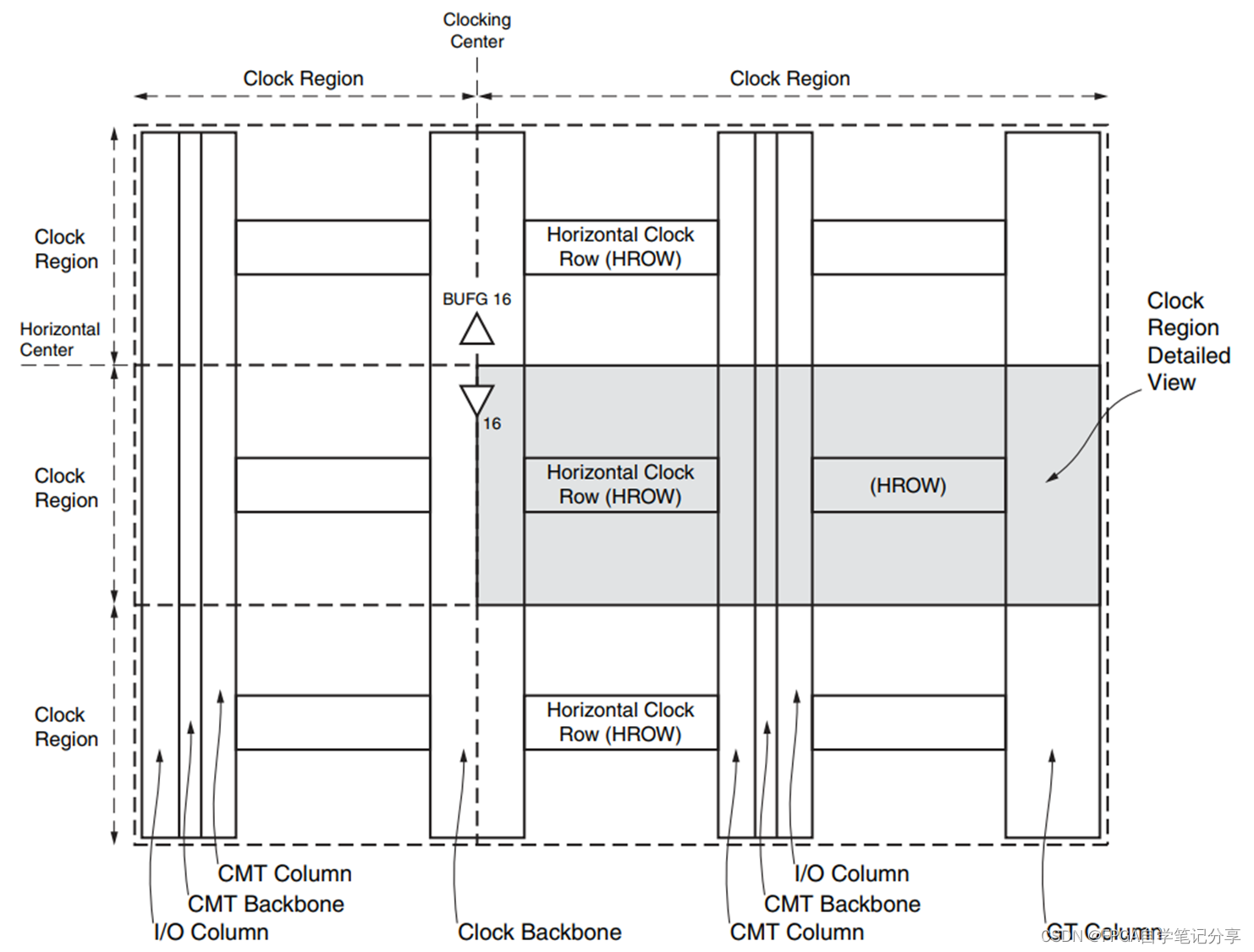

时钟域的划分如下所示,根据芯片资源的大小,每片FPGA最多有24个时钟域。

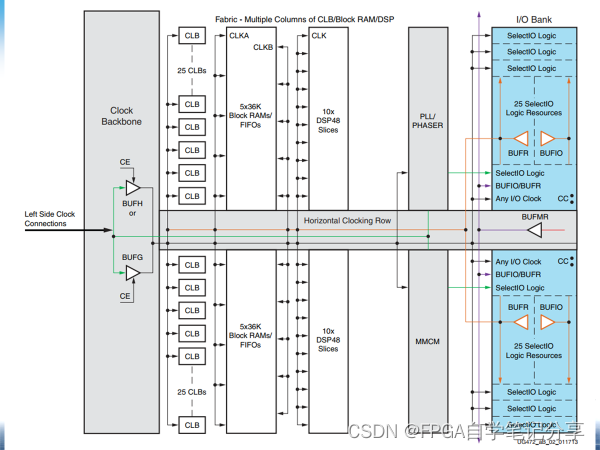

如下图,每个时钟域最多支持12个全局时钟线。每个时钟域包含所有的时序单元(CLB,I/O,串行收发器,DSP,block RAM,CMT),跨50行CLB(HROW上下各覆盖25行CLB)和5个I/O bank(50个I/O),20个DSP,12个BUFH,1个CMT,中间有一个水平时钟行( horizontal clock row,HROW)。

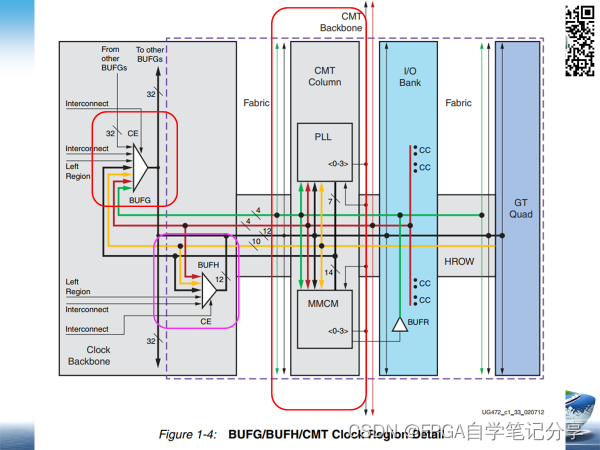

BUFG BUFH BUFR等时钟域的详细作用情况如下图所示:

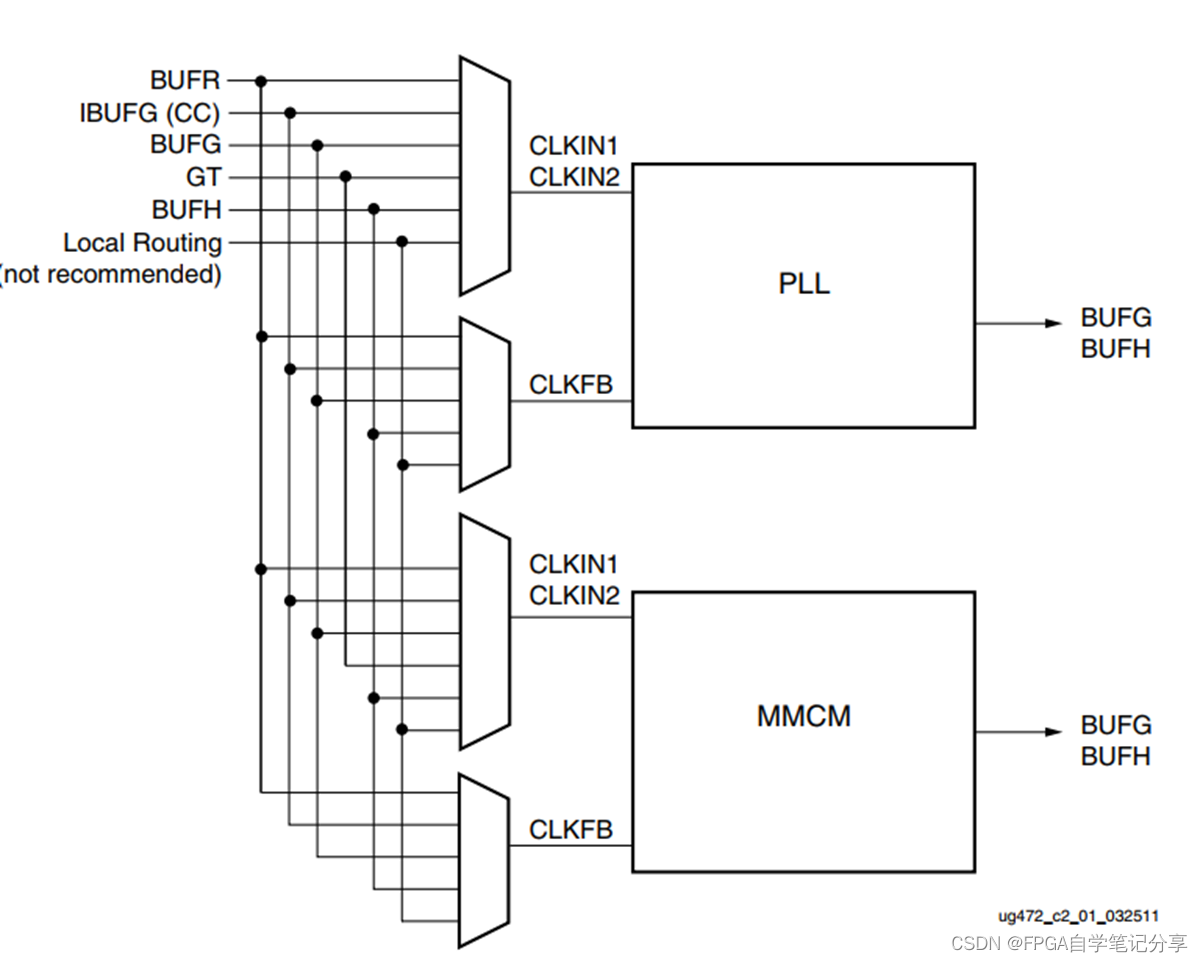

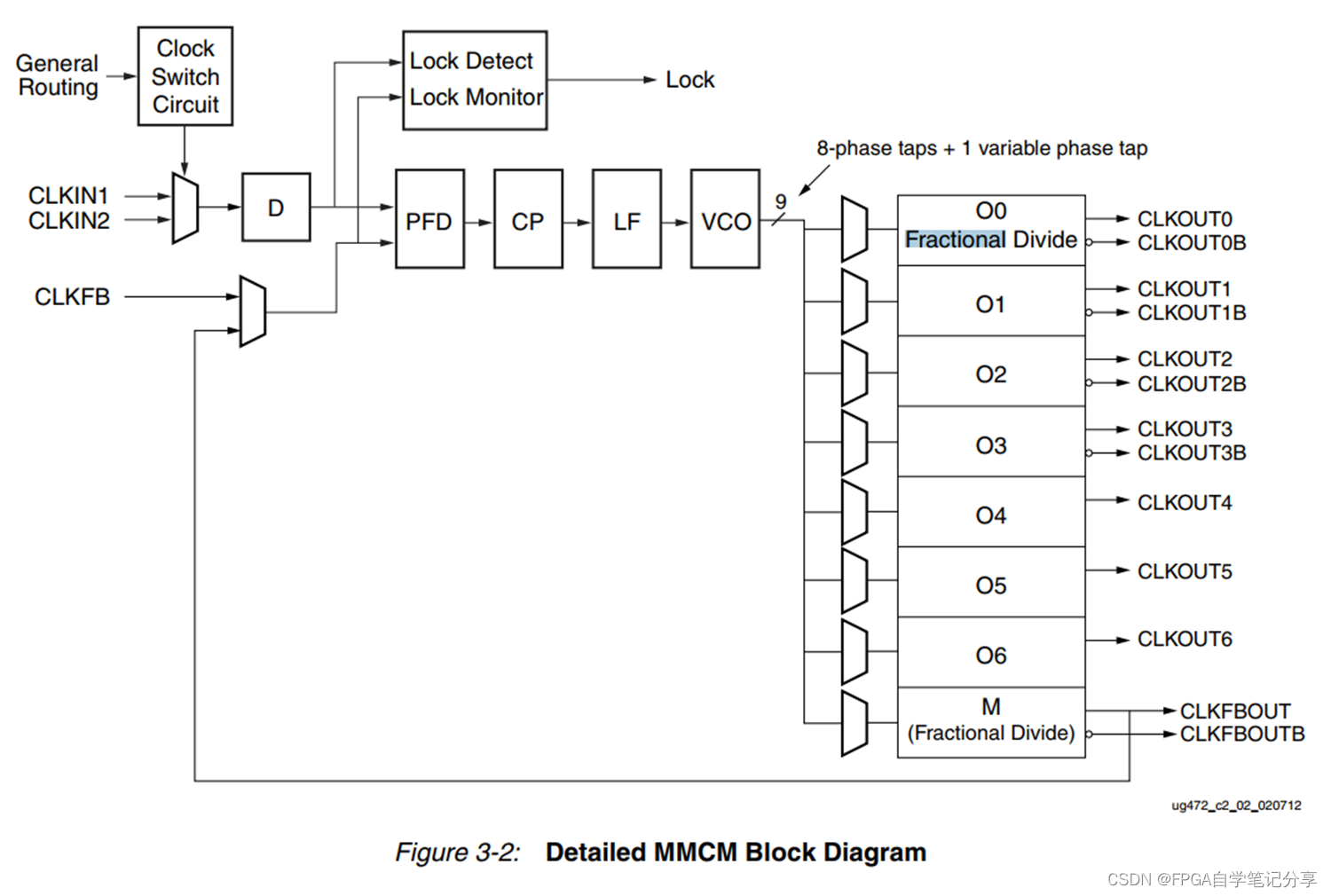

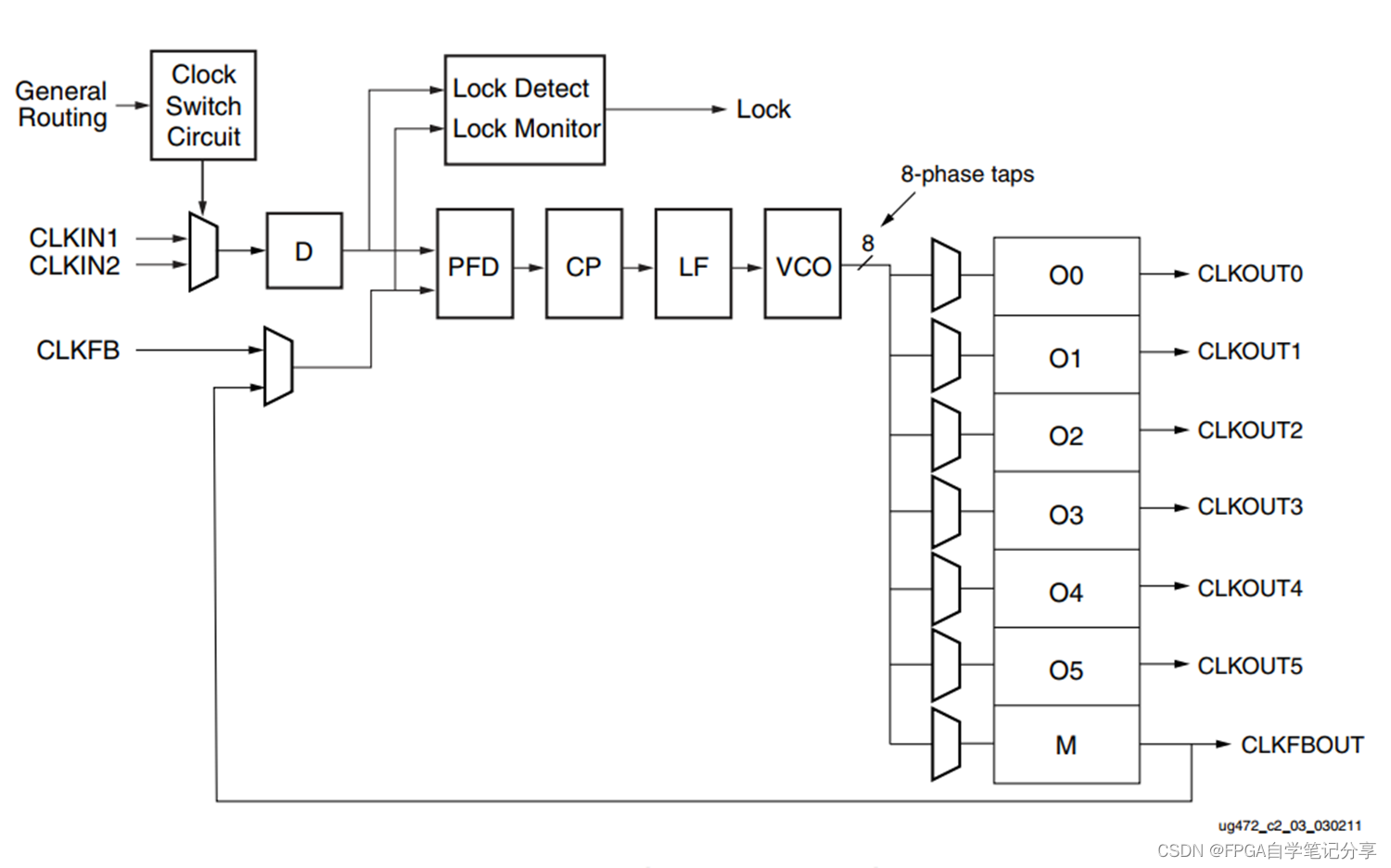

7系列FPGA最多支持24个CMT,每个CMT包含一个MMCM和一个PLL。MMCMs和PLL用作频率合成器,用于各种频率,用作外部或内部时钟的抖动滤波器,以及时钟去斜。如下图所示,PLL是MMCM功能的一个子集,MMCM在时钟输出和分频上的能力大于PLL。

详细的视频讲解见B站视频:【FPGA的底层资源之时钟】 https://www.bilibili.com/video/BV1Jd4y1T7ix/?share_source=copy_web&vd_source=9736f43bc2eebc284f4fbbe5805247a7

837

837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?