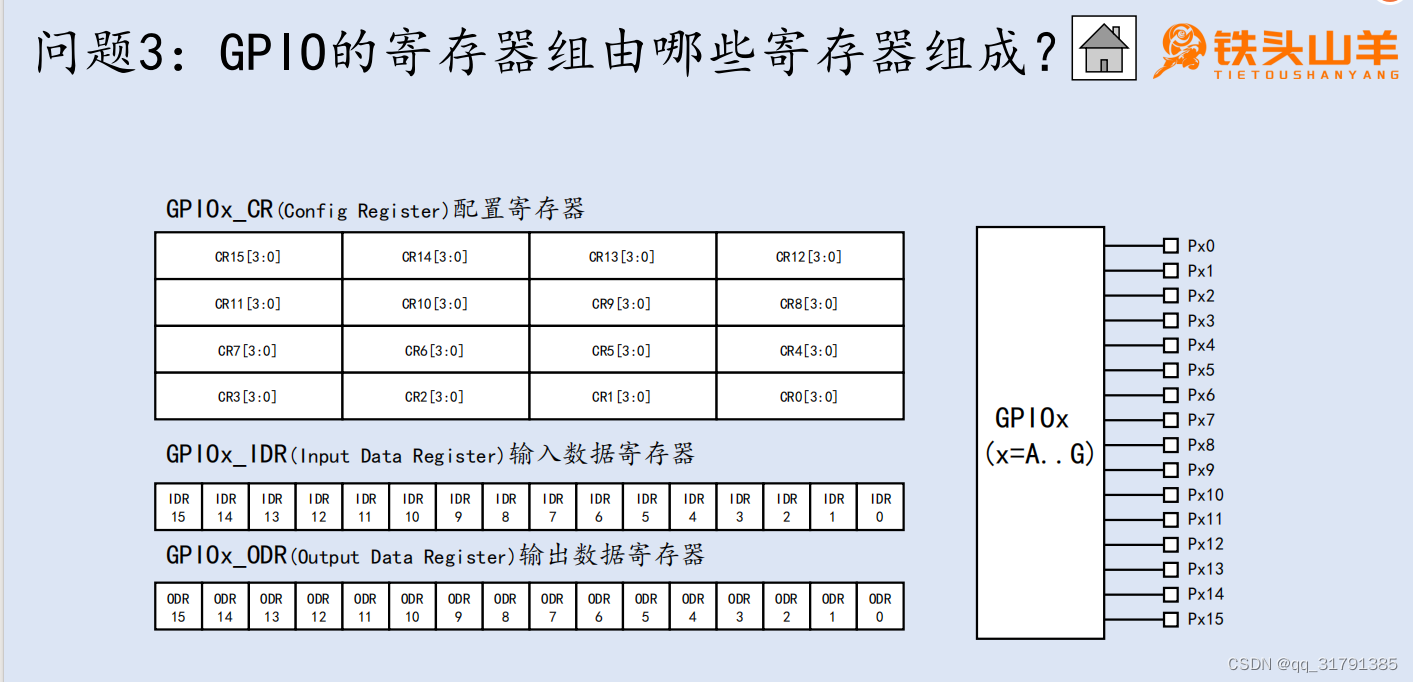

gpio寄存器组

一个配置寄存器和两个数据寄存器:

1个配置寄存器,1个输入数据寄存器,1个输出数据寄存器

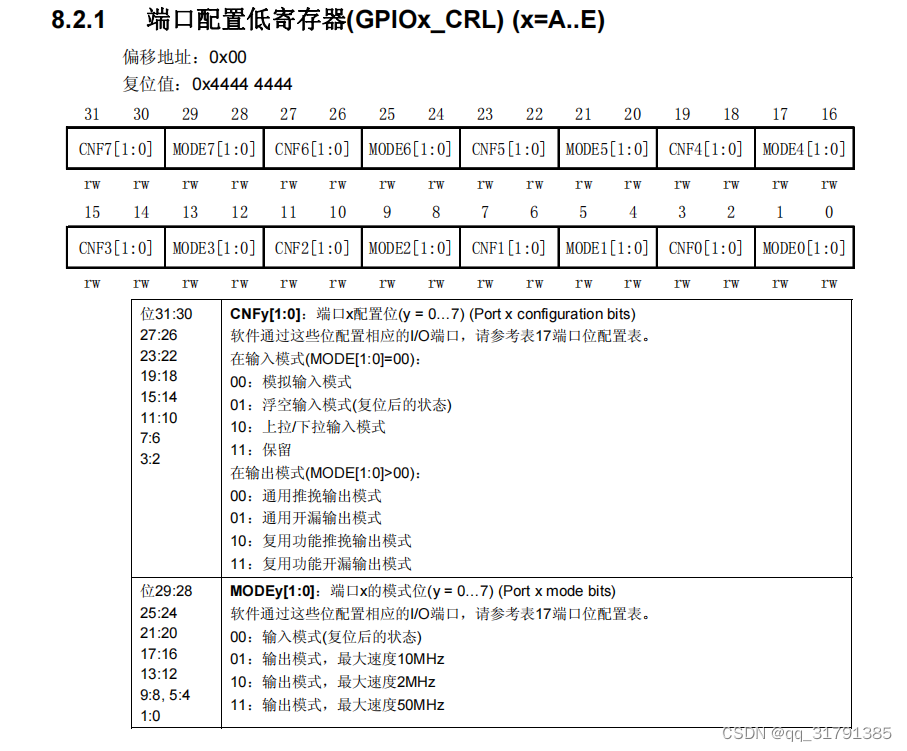

每个GPIOx(A~G)都有自己的寄存器组,因为每个GPIO端口至多有16个引脚,所以每个寄存器被分为16个小组,引脚信息只有高电平或低电平两个状态,一位二进制可以表示,所以输入寄存器和输出寄存器每个小组占1位共16位(实际上数据寄存器是32位的,但只用了16位高16位暂时没用),配置寄存器为4位又分为两个部分,CNF和MODE,MODE是选择输入模式还是2MHZ输出,10MHZ输出,50MHZ输出模式,四种状态用两位表示,CNF在输入模式和输出模式下各有四个模式,所以也是两位

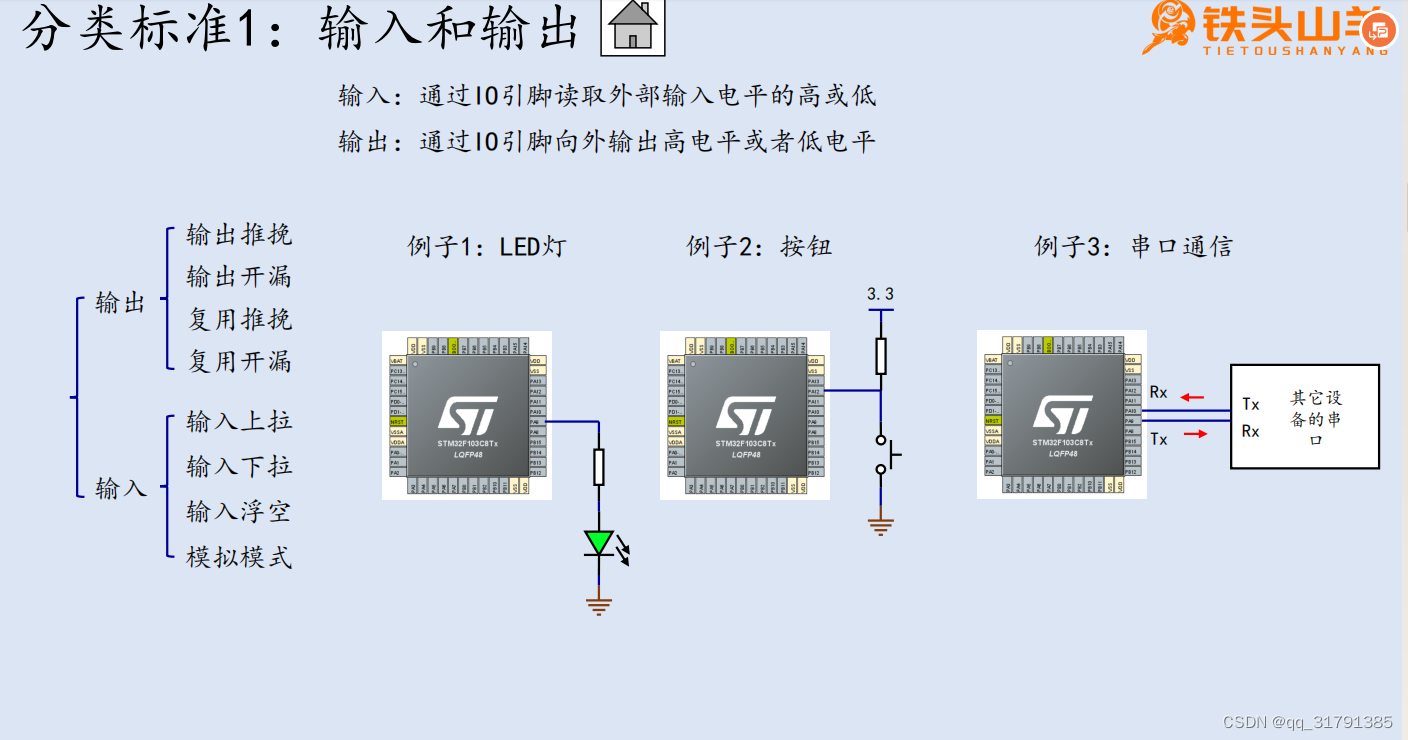

8种模式

分别是:

上拉输入,下拉输入,浮空输入,模拟输入

通用推挽输出,通用开漏输出,复用推挽输出,复用开漏输出

4种分类方法:

分类标准1:输入和输出

输入模式下单片机获取引脚电平的高低并转化为数据,输出模式下单片机控制引脚的电平高低

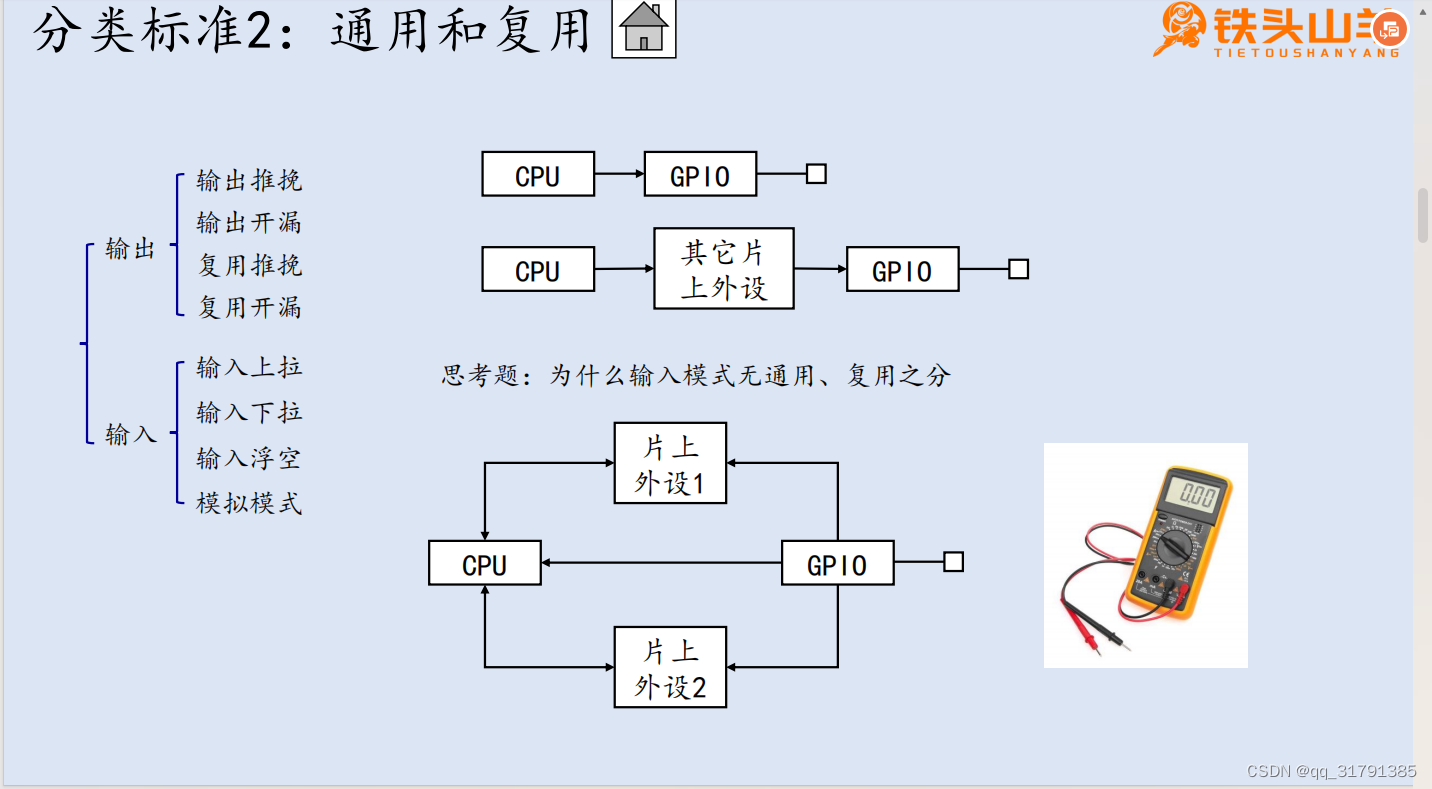

分类标准2:通用和复用

输入没有通用和复用之分,只有输出才分通用和复用

原因:输出是单片机控制引脚的高低电平,引脚只能听一个人的,如果cpu想让引脚高电平,而片上外设想让引脚为低电平,有冲突是不可以同时满足的.但输入大家都可以获取输入信息并不会产生冲突,所以输出需要分通用和复用,输入不用

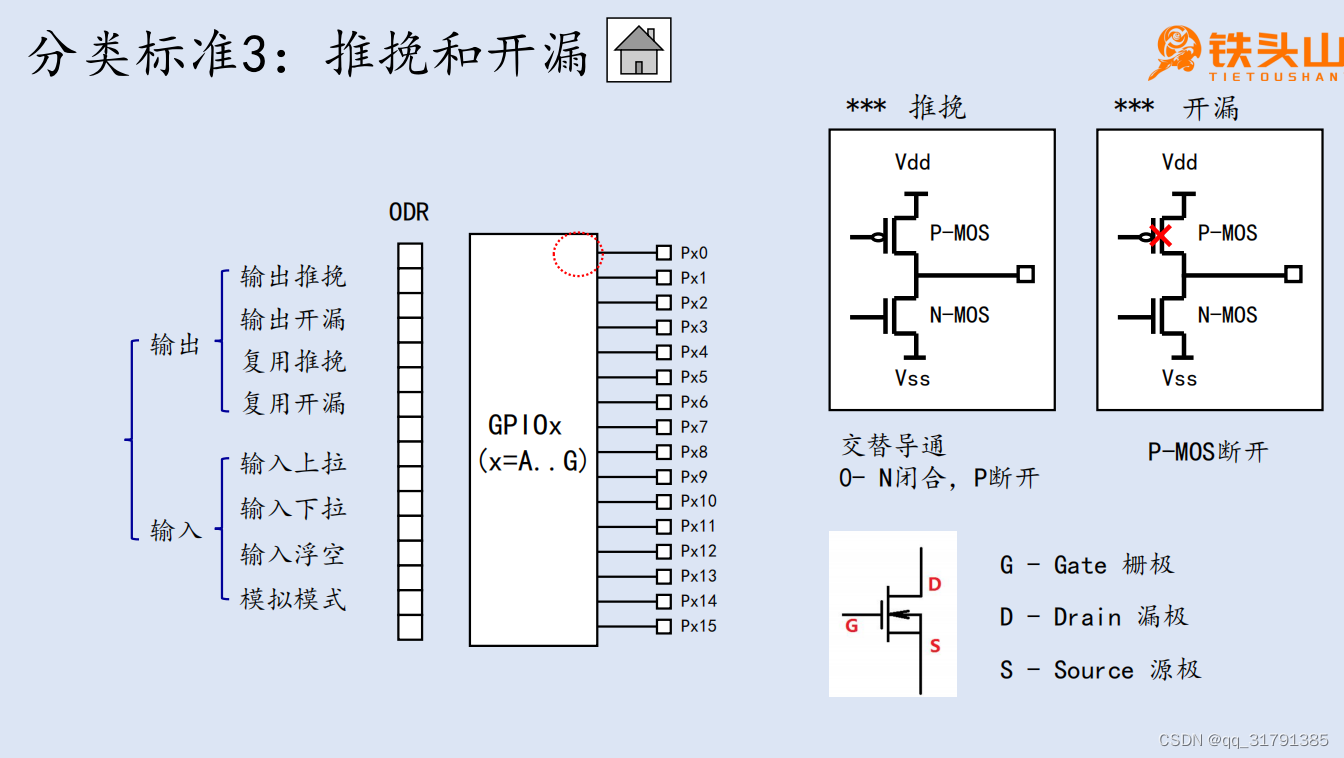

分类标准3:推挽和开漏

推挽可以输出高电平和低电平,开漏可以输出高电平和高阻态

推挽模式下,两个MOS不会同时导通,若输出数据寄存器里是1,则PMOS管道通,引脚连Vdd为高电平,输出寄存器里是0,则NMOS导通,引脚连Vss,为电平

开漏模式下,PMOS管直接就是断开的,输出寄存器若为0,则NMOS管导通,引脚连Vss,低电平,输出寄存器为1,则NMOS管也断开,呈现高阻态(b站MOS管视频说阻值可达上亿欧姆,没电流)

b站MOS管简单讲解:Mos管的工作原理_哔哩哔哩_bilibili

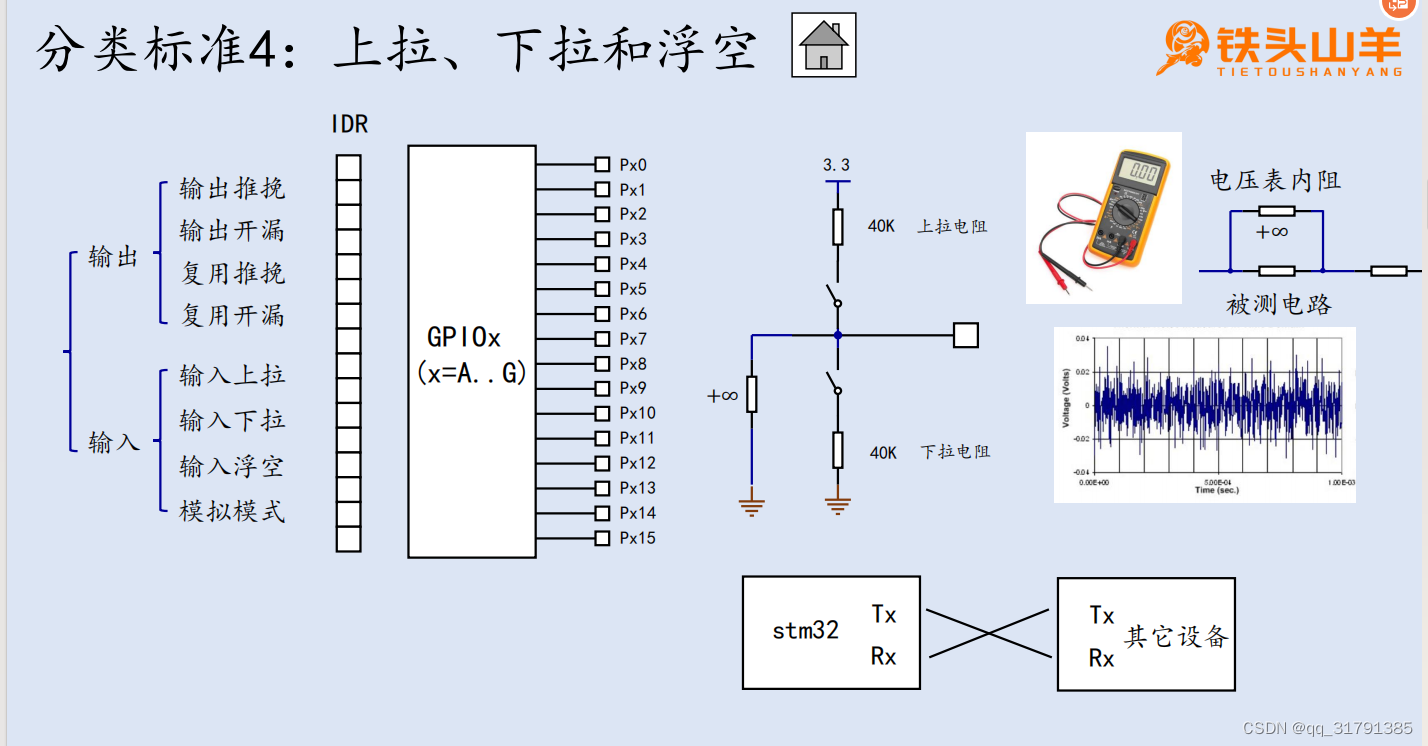

分类标准4:上拉,下拉,浮空

针对输入的.

上拉输入:外界输入低电平则输入数据寄存器为0,否则(输入高电平或者不输入数据)为1

下拉输入:外界输入高电平则输入数据寄存器为1,否则(输入低电平或者不输入数据)为0

浮空输入:外界输入高电平则输入数据寄存器为1,外界输入低电平则输入数据寄存器为0

首先引脚内阻无穷大,类似于电压表测量被测电路的电阻,如果内阻不是无穷大而是一个固定阻值的电阻,被测电路中的电阻会变成内阻与原电阻并联的电阻,比原来小.如果是无穷大,初中的欧姆定律结合一下高中极限知识就知道阻值接近于原阻值

浮空输入缺点:浮空时,如果在输入,那么就是高电平1,低电平0,但如果不输入,会相当于一个天线捕捉空气中的电子波造成明明没输入,但却有电流,并且电流是乱七八糟的,右下角图蓝色波形

上拉输入:在引脚上方加了一个3.3v电源和40K电阻,在没有输入时,电平连3.3v那里,稳定的高电平,不会 空气中的电磁波干扰,输入低电平则引脚电平变为低电平,输入寄存器变为0,这里我是用大学电路分析中的叠加原理理解的:2.6 叠加原理 视频2_哔哩哔哩_bilibili

下拉输入:在引脚上方加了一个地和40K电阻,原理与上拉一样,在没有输入时,电平连地那里,稳定的低电平,不会 空气中的电磁波干扰,输入高电平则引脚电平变为高电平,输入寄存器变为1

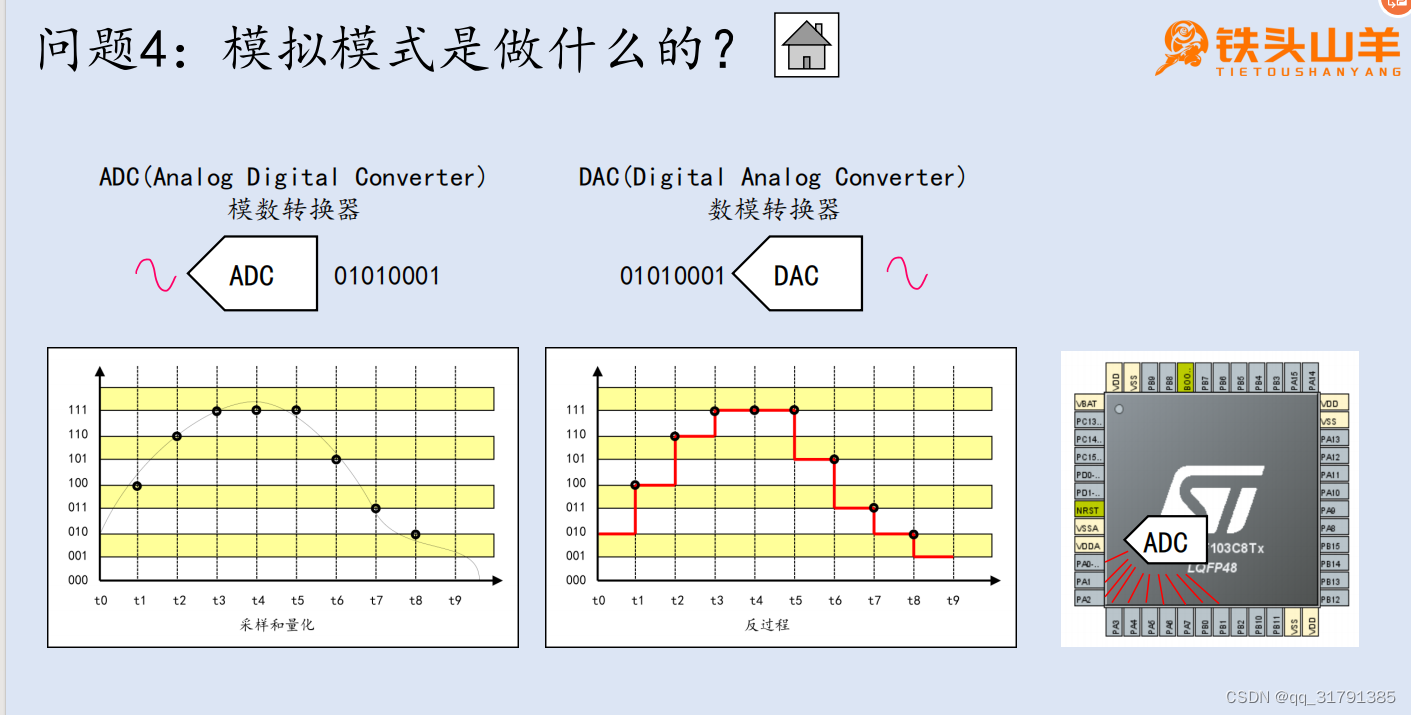

除此以外还有一个模拟输入模式

adc可以对模拟量进行采样转化为数字信号,dac将数字信号转化为模拟信号(个人暂时没见过)

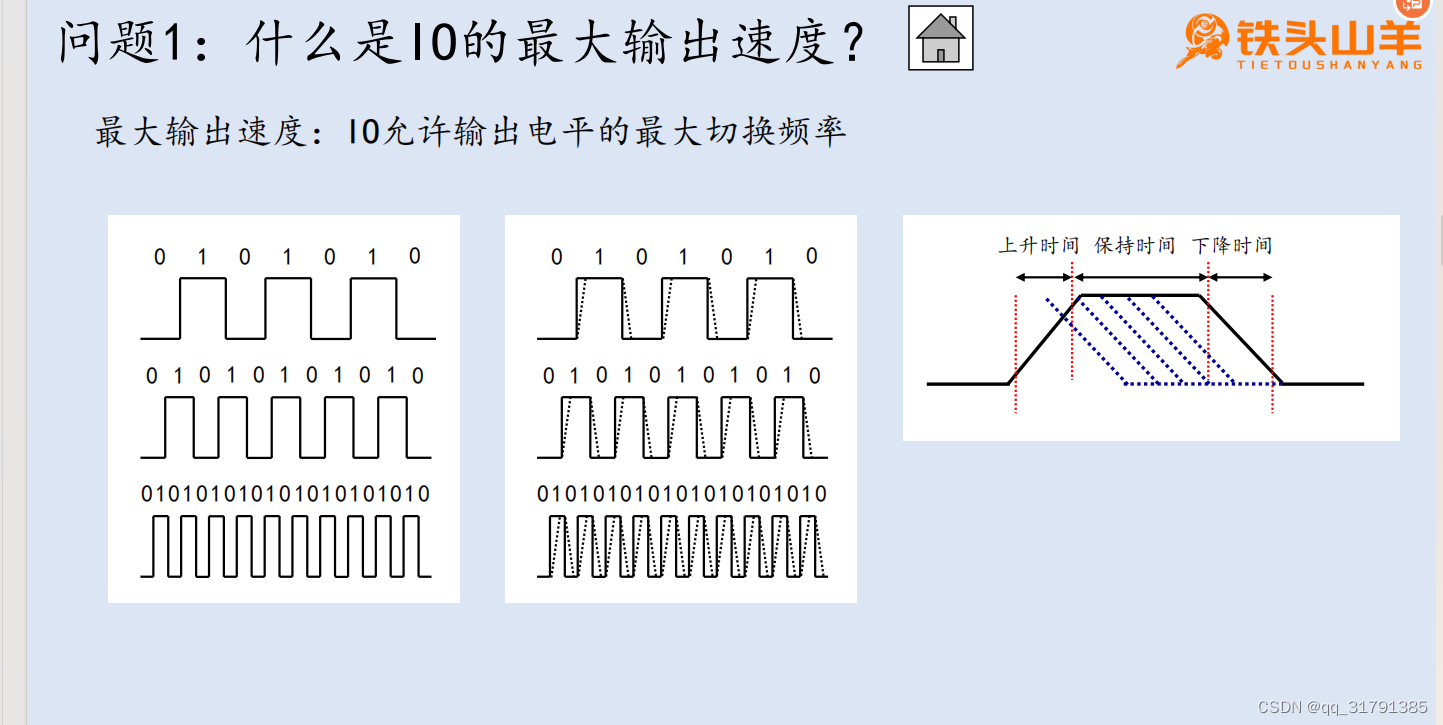

IO最大速度

最大速度限制的是电平反转的速度

有三个档位,2MHZ,10MHZ,50MHZ,不同输出速度的耗电量不同,2MHZ最低,50MHZ最高。这里的最大输出速度指的是一秒内电平可以翻转的最大次数,电平的翻转实际上不是瞬间完成的,而是要经过一段时间才能完成,从低电平到高电平需要一个"上升时间"称之为"上升沿",从高电平到低电平需要一个"下降时间"称之为"下降沿"。最大输出速度为2MHZ情况下,上升沿和下降沿时间为125ns,若中间保持时间为250ns,则正好可以每秒钟翻转2M次,如果想要翻转更多次,例如每秒翻转10M次,每次翻转需要100ns,保持时间为100-(125+125)=-150出现负数,是不可能完成的,所以2MHZ设置下无法完成翻转10M次的任务。

不同的最大输出速度实际上就是上升沿和下降沿的斜率不一样,最大输出速度越大,斜率越大,完成电平更改的时间越短,特定的翻转次数决定每次翻转的时间,这个时间不变,上升沿和下降沿时间越短,保持时间越长,所以在2MHZ情况下保持时间为负时,10MHZ的保持时间可能就不是负数,也就是可以完成这个任务

(这里我有一个疑惑:2MHZ如果上升沿和下降沿都是125ns的话,如果保持时间是150ns,那总时间就是400ns,这样应该可以到每秒2.5M次吧?(这里我觉得应该是保持时间有一个最低要求,数电时序图中保持时间是用来送数据的,要时间够长数据才会"稳定的"送进去,可惜数电太久远了,忘记了)还有就是为什么翻转时间是上升沿+下降沿+保持时间?不应该是一个沿+保持时间吗?)

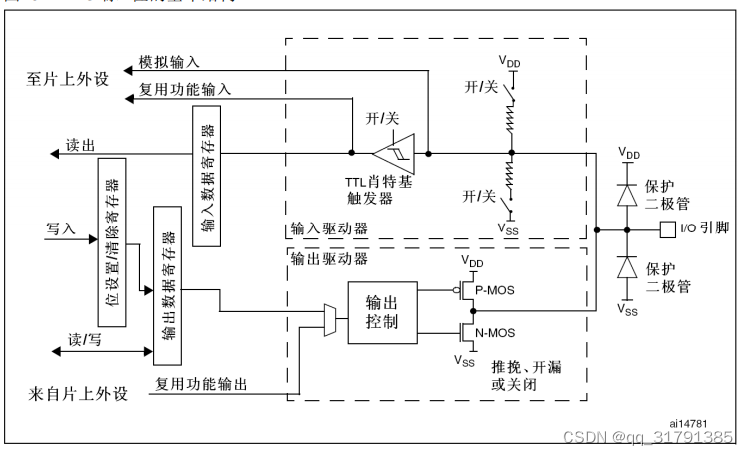

内部结构

分为上下两部分,上面是输入部分,下面是输出部分

输入路线分为

1.外部信号经过施密特触发器后进入输入数据寄存器,CPU直接读取

2.外部信号经过施密特触发器后被复用功能(使用数字信号)读走

3.外部信号经过施密特触发器前被复用功能(使用模拟信号)读走

4.外部信号经过施密特触发器后被exti读走(可以用来触发中断)

输出路线分为

1.CPU向输出数据寄存器中写数据,输出数据寄存器的值控制两个MOS管的导通与关闭,进而控制引脚的电平

2.CPU向位设置/清除寄存器中写数据进而间接控制输出数据寄存器的某一位(不影响输出数据寄存器的其他位),输出数据寄存器的值控制两个MOS管的导通与关闭,进而控制引脚的电平

3.偏上外设(如USART)连接输出控制电路控制两个MOS管的导通与关闭,进而控制引脚的电平

内部结构里的输入寄存器和输出寄存器,每个引脚应该只使用其中一个位,输出数据寄存器要想改引脚的数据需要整体改输出数据寄存器的值(一次性改了16个引脚的位),也可以用位设置/清除寄存器来控制自己的位(这样就不影响其他的引脚了)

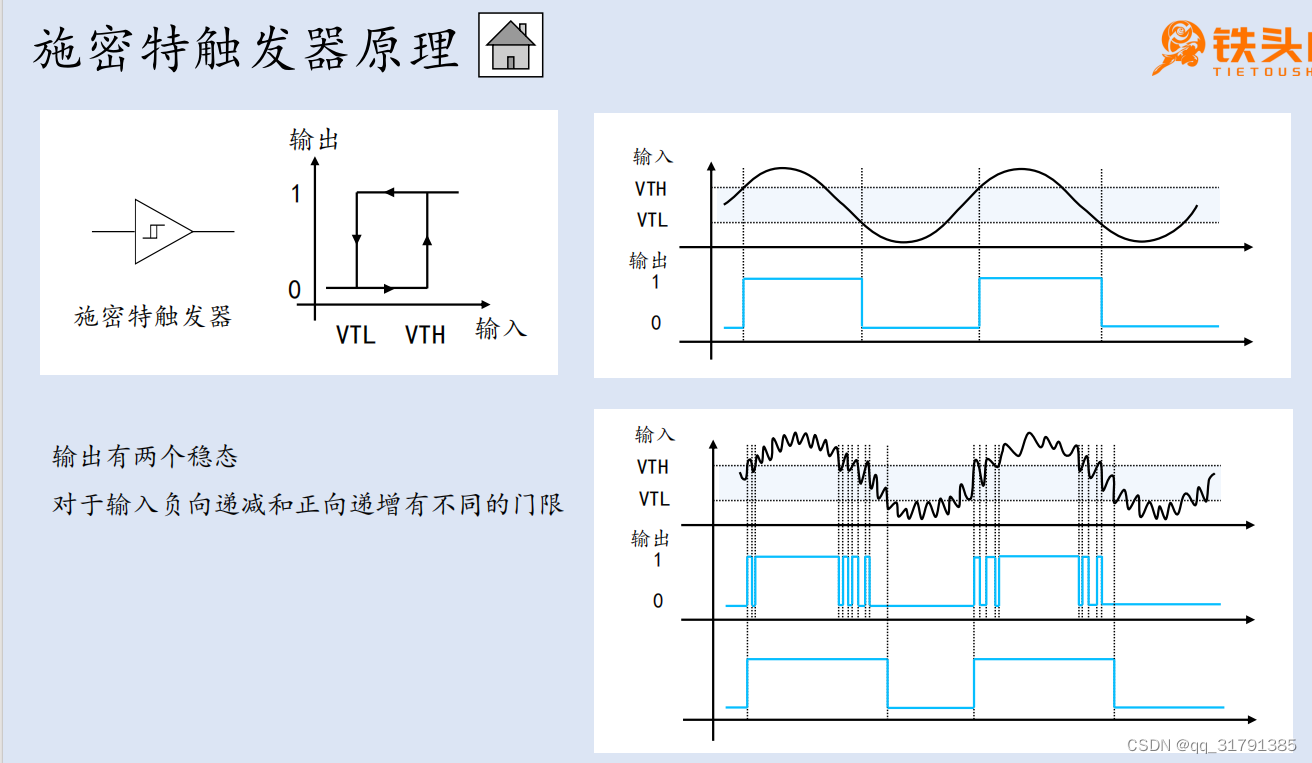

施密特触发器

施密特触发器有两个稳态,在低于下限时是低电平,高于上限时是高电平

好处:外界输入来的信号是模拟信号,一直在抖动,如果只有一个界限,高于就为高电平,低于就为低电平,那么模拟信号在界限周围抖动时,数字信号也是抖动的。而如果有两个界限值,高于上限才为高,低于下限才为低,那么在上限处抖动时:虽然在抖动但最多只会改变一次,超过上限时变为高电平,然后抖动时,因为不会低于下限,所以数字信号一直都是高电平,很稳定;在下限处抖动时:低于下限变为高电平,然后抖动时,因为不会高于上限,所以数字信号一直都是低电平,很稳定

4567

4567

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?