有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。这里是指Mealy型有限状态机。Moore型有限状态机的状态转移只取决于当前状态,与输入值无关。

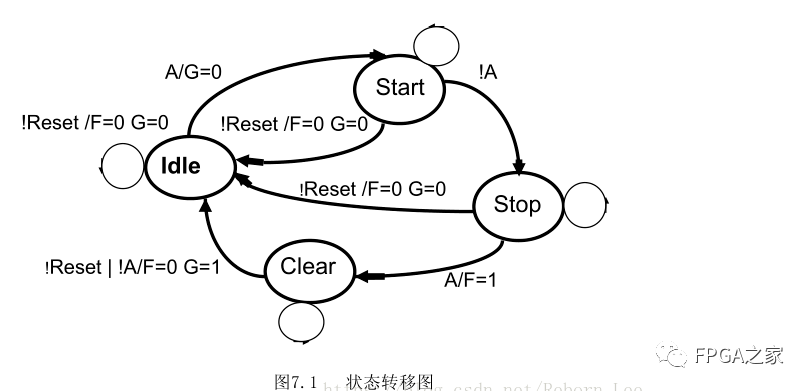

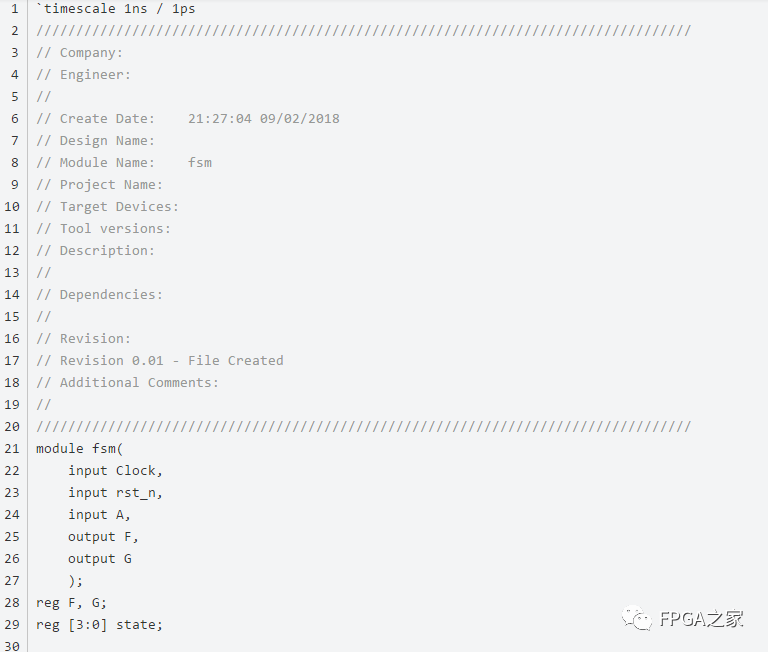

在Verilog HDL中可以用许多种方法来描述有限状态机,最常用的方法是用always语句和case语句。下面的状态转移图表示了一个有限状态机:

上面的状态转移图表示了一个四状态的有限状态机,它的同步时钟是Clock,输入信号是 A 和 rst_n ,输出信号是 F 和 G。状态的转移只能在同步时钟(Clock)的上升沿时发生,往哪个状态的转移则取决于目前所在的状态和输入的信号(Reset 和 A)。

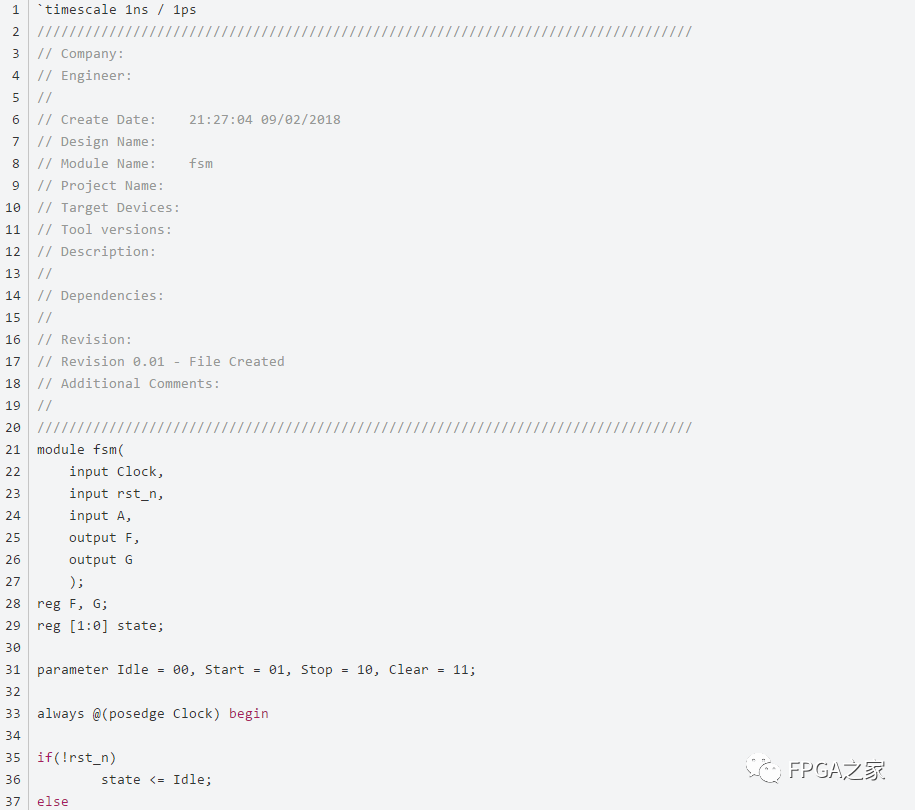

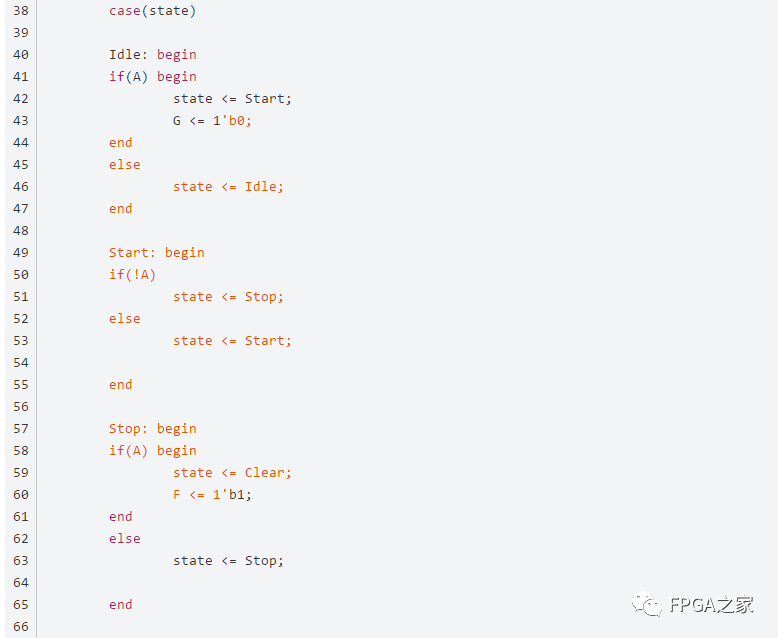

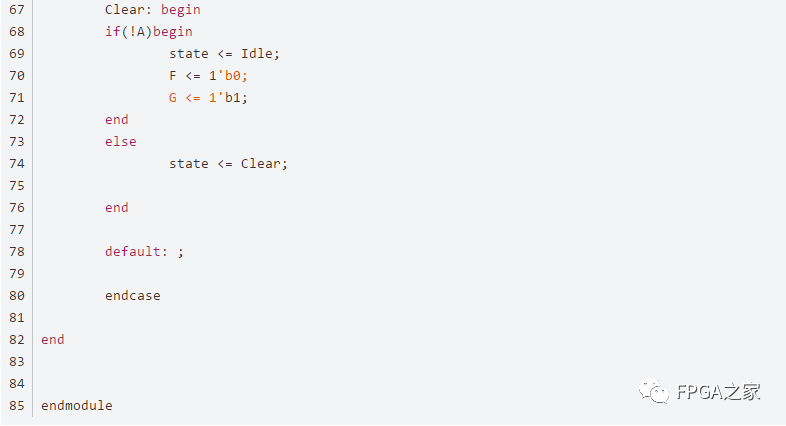

我们采用两种状态编码方式来实现这个有限状态机:

1)采用格雷码:

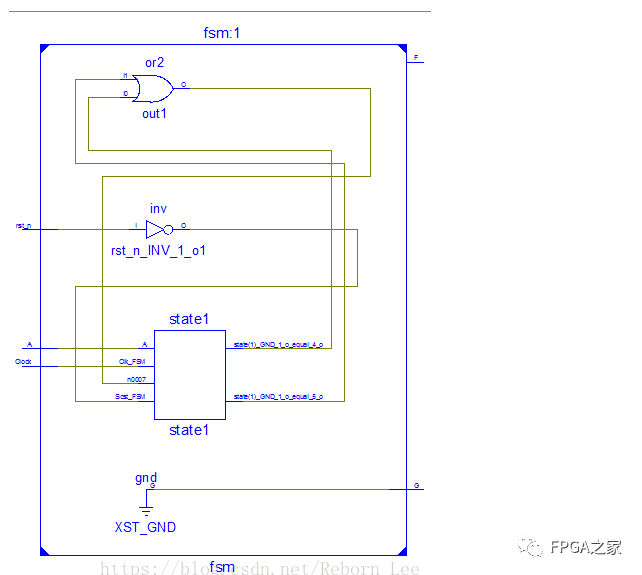

在ISE中,综合后,得到的RTL Schematic:

2)采用独热码:

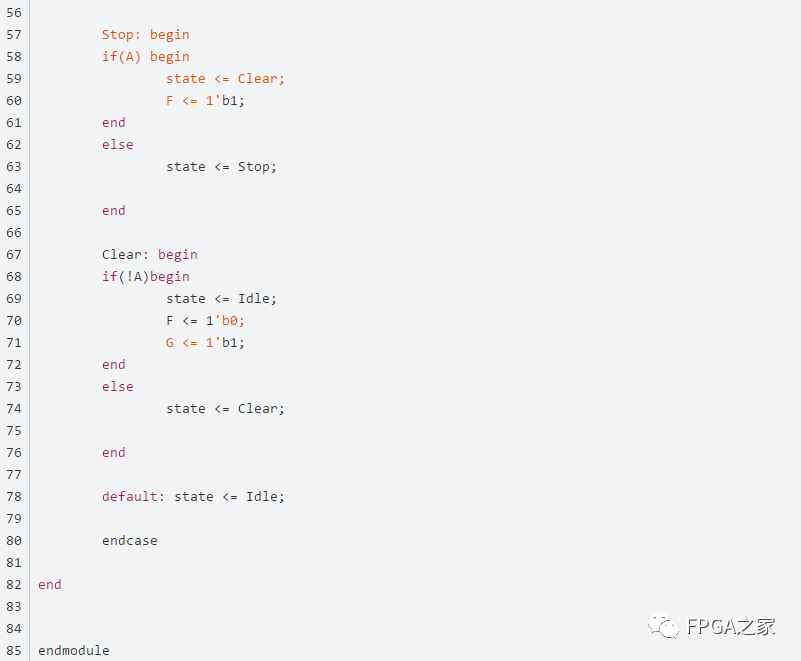

程序和上面的几乎一样,只需要改下,各个状态对应的编码值即可,还有最后的default:state <= Idle;

还是给出程序吧:

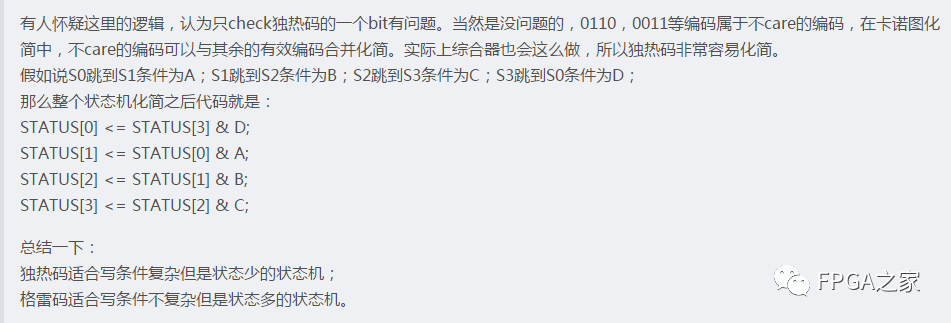

上面两个程序的主要不同点是状态编码,2)采用了独热编码,而1)则采用Gray码,究竟采用哪一种编码好要看具体情况而定。对于用FPGA实现的有限状态机建议采用独热码,因为虽然采用独热编码多用了两个触发器,但所用组合电路可省下许多,因而使电路的速度和可靠性有显著提高,而总的单元数并无显著增加。采用了独热编码后有了多余的状态,就有一些不可到达的状态,为此在CASE语句的最后需要增加default分支项,以确保多余状态能回到Idle状态。

上面所说的多余状态是:4位编码有16种,独热码只列出了4种,剩下了12种,就是多余的状态。

另一位大牛只说了一句话,但很有启发:

因为,独热码实际上相当于已经译码过后的信号。

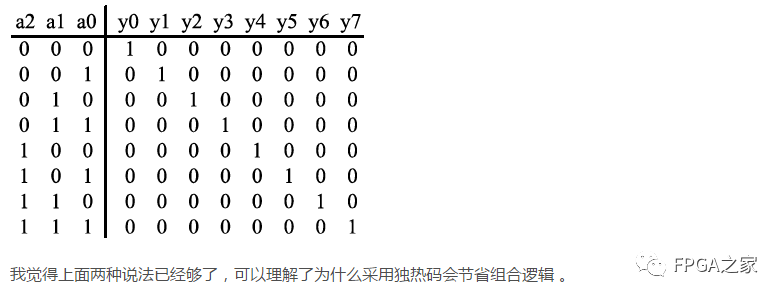

把数电书翻出来看看3-8译码器,看看译码以后的信号长什么样。

那我把3—8译码器的真值表给出来,确实如此。

5592

5592

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?