概述

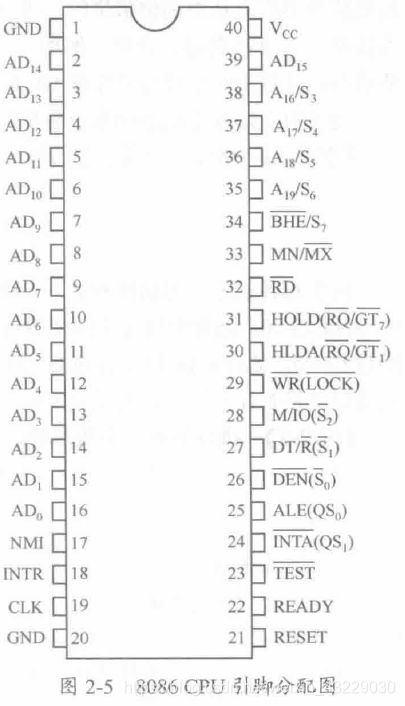

8086 是 16 位 CPU , 采用高性能的 N 沟道、耗尽型负载的硅栅工艺(HMOS) 制造。由于受当时制造工艺的限制,为了解决功能多和引脚少的矛盾,部分引脚采用 分时复用 的方式,构成了 40 条引脚的双列直插式封装。

分时复用: 在同一根传输线上,在不同时间传送不同的信息

这些功能引脚有两种情况:一种是采用了分时复用的地址/数据总线;另一种是根据不同的工作模式定义不同的引脚功能。

引脚介绍

8086 CPU 可以工作在最小模式和最大模式下, 因此有8 条引脚(2 4 〜3 1 ) 在上述两种工作模式中具有不同的功能,括号中所示为最大模式下被重新定义的控制信号。

最小模式: 单处理模式,指系统只有一个8086微处理器,所有的总线控制信号都由8086微处理器直接产生,构成系统所需的总线。控制逻辑部件最少的

最大模式: 系统可以有一个以上的微处理器,除了8086,还可以配置用于数值计算的数值协处理器 8087 和用于 I/O 管理的 I/O 协处理器 8089 。各个处理器发往总线的命令统一送往总线控制器,由它仲裁后发出。

是什么模式由引脚 M N / M X ‾ MN / \overline{MX} MN/MX 决定

引脚介绍1:打头阵

M N / M X ‾ MN / \overline{MX} MN/MX (Minimum / Maximum mode control,模式控制信号,输入)

M N / M X ‾ MN / \overline{MX} MN/MX 为高电平,表示 CPU 工作在最小模式系统中: M N / M X ‾ MN / \overline{MX} MN/MX 为低电平,表示 CPU 工作在最大模式系统中。

引脚介绍2:两种模式共享的引脚信号

两种模式共享的引脚信号

G N D 、 V C C GND 、 VCC GND、VCC (输入)

GND为接地端,VCC为电源端,采用的电源为 5V±10%

A D 15 〜 A D 0 AD_{15}〜AD_0 AD15〜AD0 ( Address Data Bus,地址/数据复用线,双向、三态 )

分时复用的地址数据总线。传送地址时以三态输出,传送数据时可以以双向三态输入/输出。

A 19 / S 6 〜 A 16 / S 3 A19/S6〜A16/S3 A19/S6〜A16/S3 (Address/Status,地址状态复用总线,双向、三态)

分时复用的地址/状态线。作为地址线用时 A D 15 〜 A D 0 AD_{15}〜AD_0 AD15〜AD0和 A 19 〜 A 16 A_{19}〜A_{16} A19〜A16起构成访问存储器的 20 位物理地址当 CPU 访问 I/O 端口时, A 19 〜 A 16 A_{19}〜A_{16} A19〜A16保持为 “0 ”(低电平)。作为状态线用时, S 6 〜 S 3 S_6〜S_3 S6〜S3 用来输出状态信息,其中 S 3 S_3 S3 和 S 4 S_4 S4表示当前使用的段寄存器名。

| S 4 S_4 S4 | S 3 S_3 S3 | 段寄存器 |

|---|---|---|

| 0 | 0 | ES |

| 0 | 1 | SS |

| 1 | 0 | CS或未使用任何段寄存器(I/O、INT) |

| 1 | 1 | DS |

8086是16位CPU,采用HMOS工艺,有40条引脚,其中一些是分时复用的。CPU可以工作在最小模式(单处理)和最大模式(多处理器),模式由MN/MX引脚控制。地址/数据总线、地址/状态线等是复用的,如AD15~AD0、A19/S6~A16/S3。引脚功能包括读写信号、中断请求、时钟、复位等。最小模式下,WR、M/IO和DEN等信号用于控制数据传输,最大模式下有额外的总线控制信号。

8086是16位CPU,采用HMOS工艺,有40条引脚,其中一些是分时复用的。CPU可以工作在最小模式(单处理)和最大模式(多处理器),模式由MN/MX引脚控制。地址/数据总线、地址/状态线等是复用的,如AD15~AD0、A19/S6~A16/S3。引脚功能包括读写信号、中断请求、时钟、复位等。最小模式下,WR、M/IO和DEN等信号用于控制数据传输,最大模式下有额外的总线控制信号。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5415

5415

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?