13.测试仿真结构、测试激励描述方式

对于一个典型的电路测试,一般会有个信号源对它的目标电路进行激励然后通过测试设备,对波形进行观察然后确定电路正确与否

仿真和测试模块只有模块名没有输入和输出信号的列表

激励信号定义为reg型,显示信号定义为wire型

这些激励信号通常公采用 initial或 always语句对它进行产生

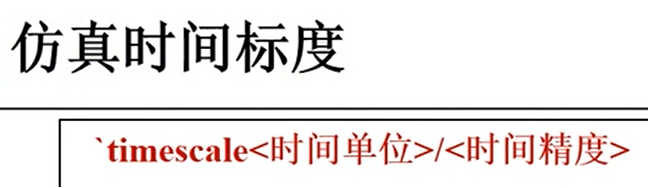

timescale 1ns/1ns:定义了仿真的时间单位以及可以观察到最小信号的时间单位

测试激励描述方式

目前,主要有以下3种产生测试激励的方法:

(1)直接编辑测试激励波形:在测试环境中,用人工的方式去改变信号的电平,产生我们要求的测试向量,但这种方式效率较低

(2)用 Verilog HDL语言的时序控制功能,产生测试激励

(3)利用 Verilog HDL语言的读文件功能,从文本文件中读取数据:第三种方式对于一些大规模电路,以及可靠性要求较高的测试环境中,通常会使用这种方式

所有的信号在上电之前都要进行初始化

1.initia初始化

在大多数情况下,Testbench中信号初始化的工作通过 initia过程块来完成,例如:initial temp=0;

2.定义信号时初始化

Verilog HDL也支持在信号定义时进行初始化,例如:reg[3:0]cnt=4’ b0000

延迟控制

通过INITAL语句或 ALWAYS语句加上延迟控制语句,就可以产生所需要的任意的波形信号

2.事件语句

事件语句实际上就是需要等待这个事件发生的一个过程(eg敏感事件表)

14.串行和并行语句块产生测试信号

VERILOG这门课程中,实际上提供很多的语句类型,这就给工程设计人员提供了产生测试信号的多种方式

并行语句所有的语句顺序是完全并行的,不会因为前一条语句而影响到后一条语句

产生同样一个信号既可以用串行语句相对延迟时间产生,也可以用并行语句绝对延迟时间产生

采用 begin、end串行结构,加上外部延迟控制的阻塞性赋值

采用串行语句的阻塞性赋值方式后,内部延迟控制和外部延迟控制实际上是一致的

15.任务和函数

使用函数可以让工程师在编写程序时,能够以较少的语句将内容描述清楚,可以实现代码的复用,高效率编程

端口的顺序与端口类型说明的顺序应当是严格一致的

任务的方式可以极大地减少程序设计时的代码量

函数的调用方式不能单独存在,它定是调用的过程中会被当作一个返回值去赋给某一个信号

对于函数的调用过程,它一定是当作个数值去返回到程序过程中某一个赋值表达式里,这样才能完成函数的调用

16.典型测试向量产生方法

- 时钟信号在硬件中(尤其在数字电路中)是一个非常重要的信号,它始终是存在的一个情况

使用 forever语句、while语句for语句以及 always语句,都可以产生

在数字电路中,时钟信号并不是50%是0、50%是1一定存在,有可能1的时间会比较长,0的时间会比较短,反之亦然,这就是占空比的概念。

用时钟信号去驱动移位寄存器,循环反复地产生序列测试信号

在目前使用的处理器(cPU、DSP MCU)中,都是采用总线实现中央处理器和外部控制器的相结合

在硬件描述语言中,测试和仿真中会用到很多的语法,合理地使用这些语法会提高测试仿真过程中的编程效率

17 .系统任务和函数的使用

(1)显示任务

(2)文件管理任务

(3)仿真控制任务

(4)时间函数

(5)随机函数

1.显示

这两种方式对于结构性的描述,和硬件描述语言的驱动强度等概念,具有重要意义

display在显示结束之后会有一个换行

write在显示结束之后没有换行

选通监控任务

DISPLAY属于阻塞性串行语句,当执行到这条语句时立即执行,而 STROBE语句在同一时刻所有指令结束之后然后才打印数据

连续监控任务

display和 strobe语句是在信号指令发生变化时,才进行屏幕打印

连续监控任务可以实现,在输出变量表发生变化的时候,就立即打印

输出变量决定了 monitor变化的过程

在 monitor使用过程中,通常会使用initial语句

仿真控制任务

使用FNSH语句时,当任务结束后会结束当前的仿真结果,并跳出仿真环境。而STP语句在执行过程中,只会停在需要停的位置上,并不退出仿真环境

由于硬件仿真时需要耗费的时间和计算机资源较多,因此工程师通常会在仿真开始之前执行一小段程序,判断出所用的 MEMORY和CPU时间以估算整个仿真过程所用的时间

时间函数

t

i

m

e

表

征

的

是

仿

真

在

进

行

的

过

程

中

所

处

的

仿

真

时

刻

由

于

time表征的是仿真在进行的过程中所处的仿真时刻 由于

time表征的是仿真在进行的过程中所处的仿真时刻由于TIME是一个整型的量,它不能表征小数点的实数类型

系统的时间对于仿真过程是一个很重要的数据,它表征了系统中仿真的时刻以及还有多长时间能够用于仿真

随机函数

在硬件描述语言中,随机函数使用的并不多

18.编译预处理语句

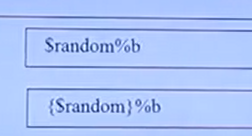

用宏名代替特定字符串

define语句使用区限:从 define定义开始,至 undef出现,取消定义。

define和 parameter是有区别的

(1)作用域不同。parameter作用于声明的那个文件;‘define从编译器读到这条指令开始到编译结束都有效,或者遇到 undef命令使之失效,可以应用于整个工程。

(2)传递功能不同。parameter可以用作模块例化时的参数传递,实现参数化调用;define语句则没有此作用。‘define语句可以定义表达式,而 parameter只能用于定义变量。

define语句面不加分号,直接使用。

在硬件描述语言中,通常采用结构化建模方式,通过模块调用实现不同层次电路代码的集合。

仿真时间标度确定了在仿真过程中的时间单位和仿真精度。

时间单位:仿真过程中,延迟整数部分所表示的时间。

在 timescale命令中,用于说明时间单位和时间精度参量值的数字必须是整数,其有效数字为1、10、100,单位为秒(s)、毫秒(ms)、微秒(us)、纳秒(ns)、 皮秒(ps)、毫皮秒(fs)。

19.路径延迟的参数

设置模块路径延迟需要两步,首先描述模块路径,然后把延迟赋给这些路径

(1)源信号应该是模块的输入或输入输出端口,可以是标量和矢量的任意组合

(2)目的信号应该是模块的输出或输入输出端口,可以是标量和矢量的任意组合。

(3)目的信号应该只能被一个驱动源驱动。

延迟量包括:上升沿延迟,下降沿延迟,不定态延迟和高阻状态延迟

模块路径的延迟赋值原则如下:

(1)左侧是模块路径描述,右侧是一个或多个延迟值。

(2)延迟值可以放在一个括号内

(3)延迟值可以是常数,也可以是 specparam参数:可以是一个数值,也可以是表示

“min:typ max”的三元组

(4)路径延迟与信号转换的关系,可以指定1、2、3、6或12个延迟值

全连接方式可以更加有效的表征端口到端口的延迟

20.时序检查

在数字集成电路中对于时序的要求非常严格,包括建立时间、保持时间等。

时序检查是包含在 specify和 endspecify语句中间的一个过程

limit表示的是最小允许的间隙是多大

3664

3664

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?