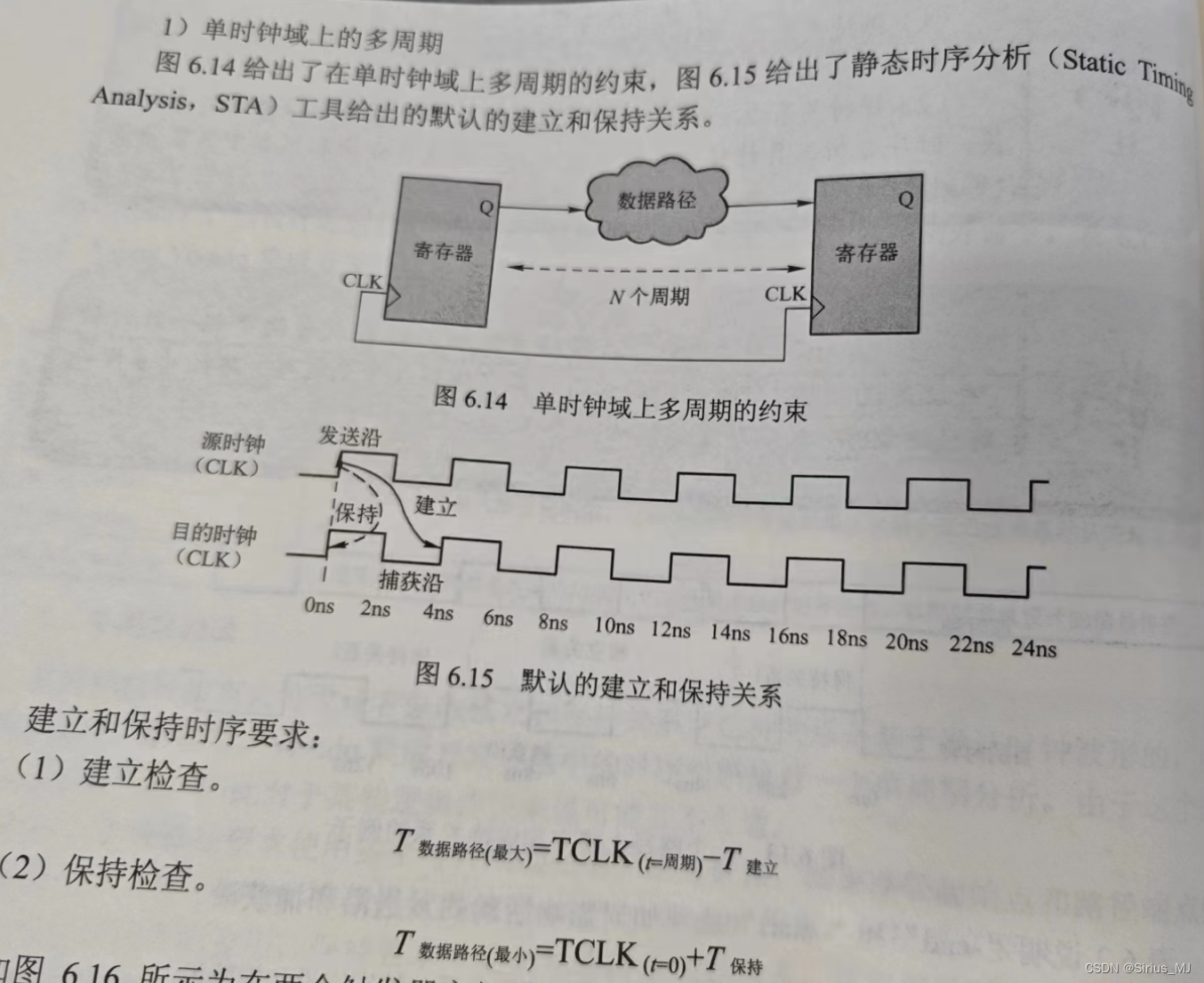

建立检查

Tmax = TCLK - Tsetup

保持检查

Tmin = TCLK + Thold

当静态时序分析产生时序违规时,就需要用到时序例外

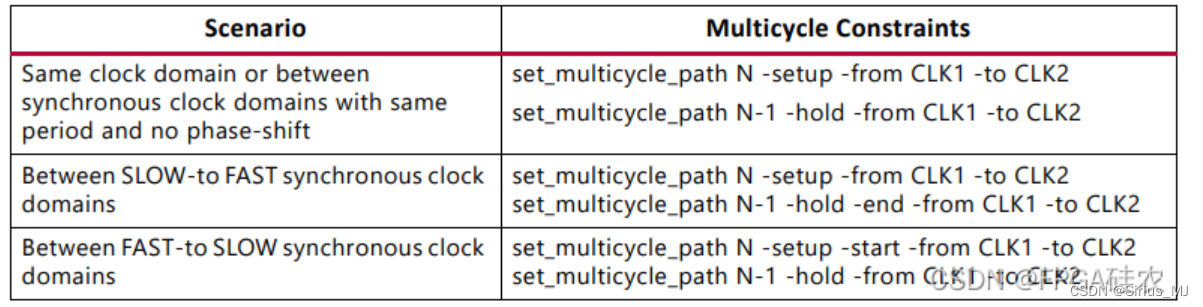

1.多周期路径设置

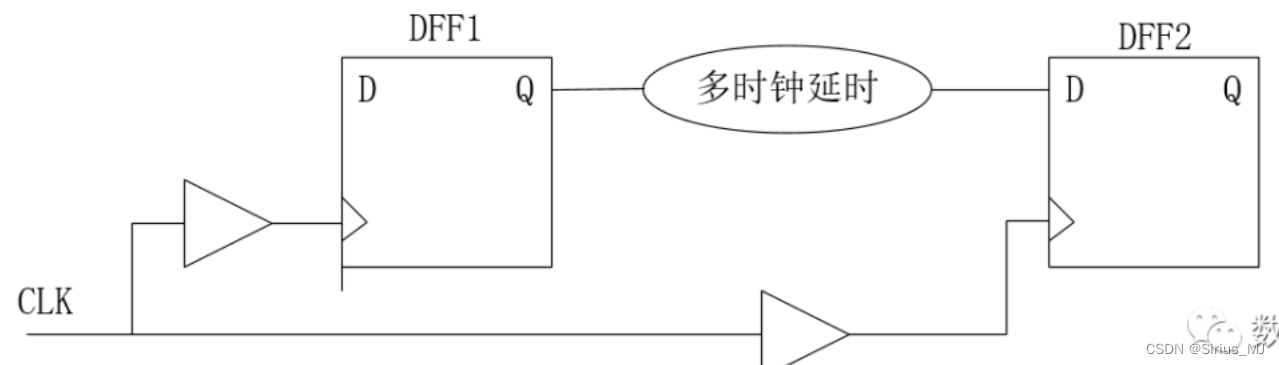

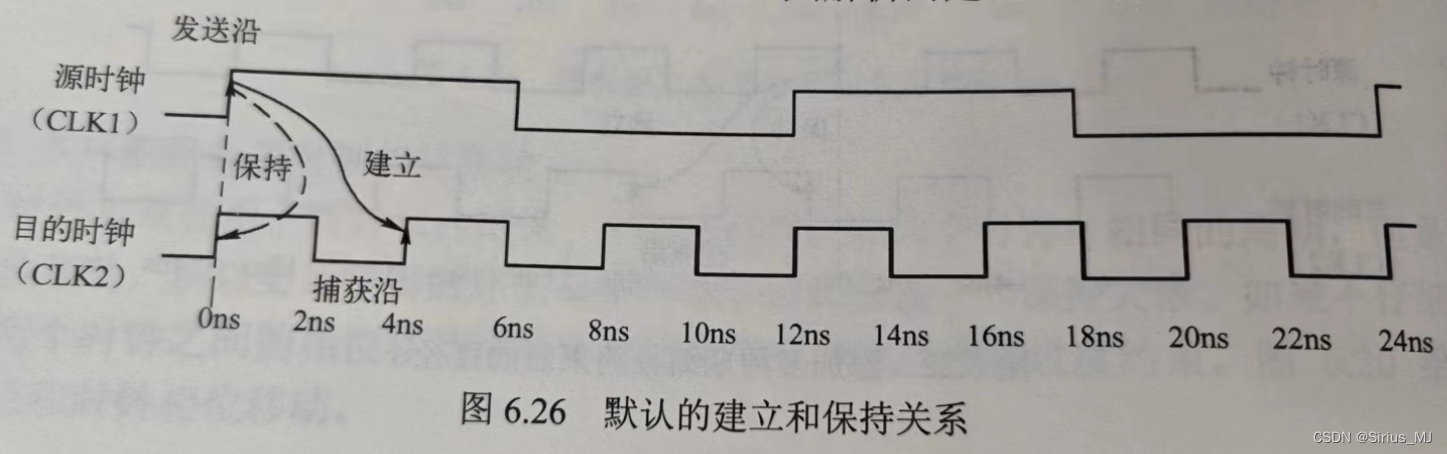

设计中存在时序路径延时比较长,并且设计允许信号在这类时序路径下的延时等于几个周期的时间,如下图所示。

由于发射时序单元和捕获时序单元中的逻辑电路延时有多个时钟,故需要设置几个时钟的建立时间,定义的命令如下。

set_multicycle_path <num cycles> -from <startpoints> -to <endpoints> //setup

set_multicycle_path -hold <num cycles> -from <startpoints> -to <endpoints> //hold

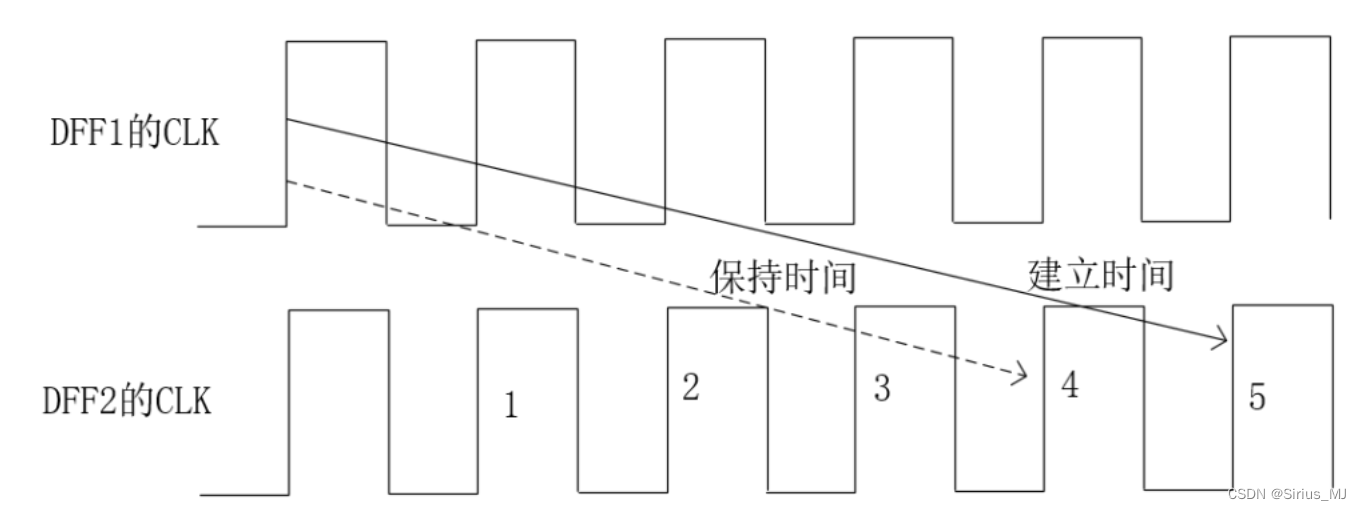

set_multicycle_path 5 -from [get_pins DFF1/Q] -to [get_pins DFF2/D]

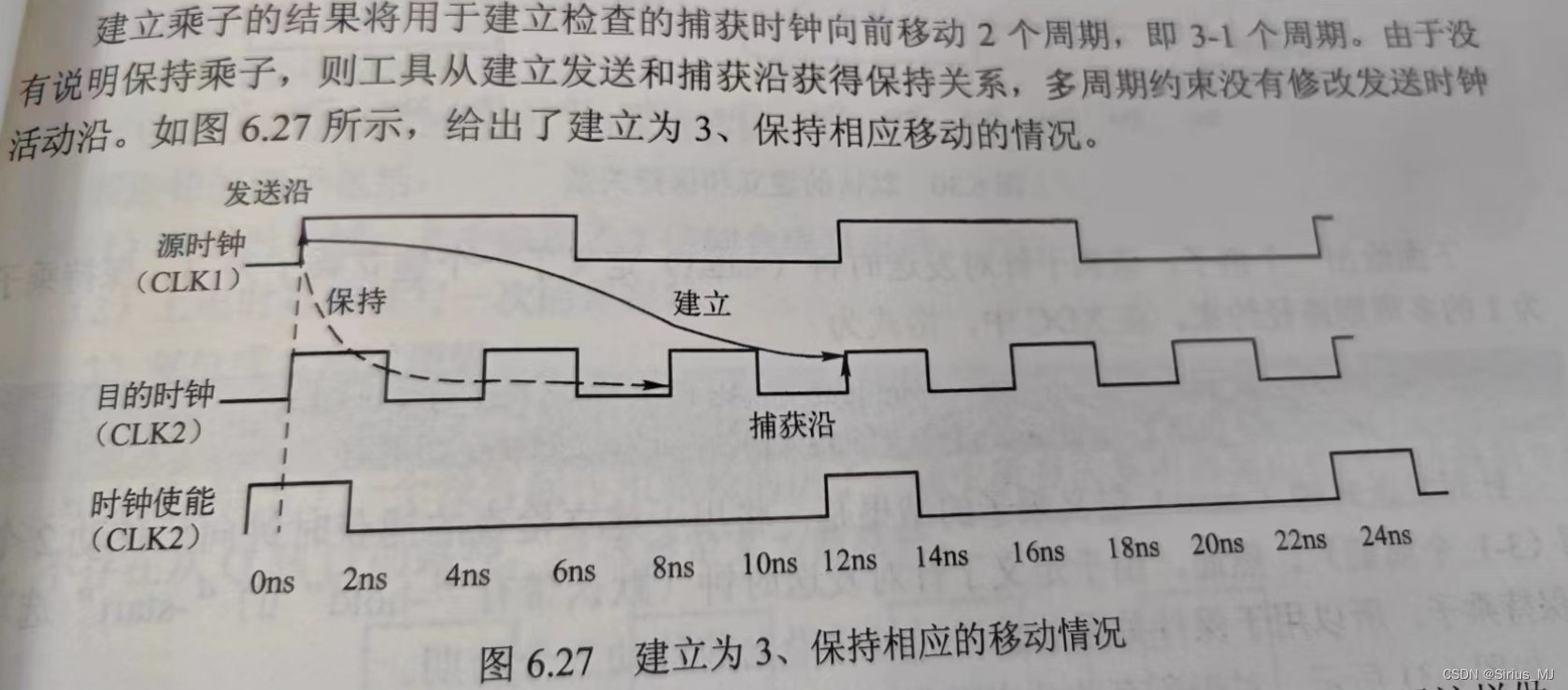

set_multicycle_path 4 -hold -from [get_pins DFF1/Q] -to [get_pins DFF2/D] 以上命令定义触发器DFF1与DFF2之间时序路径建立时间的延时为第5个时钟周期检查,保持时间的延时为第4个周期检查,其延时波形如下图所示。

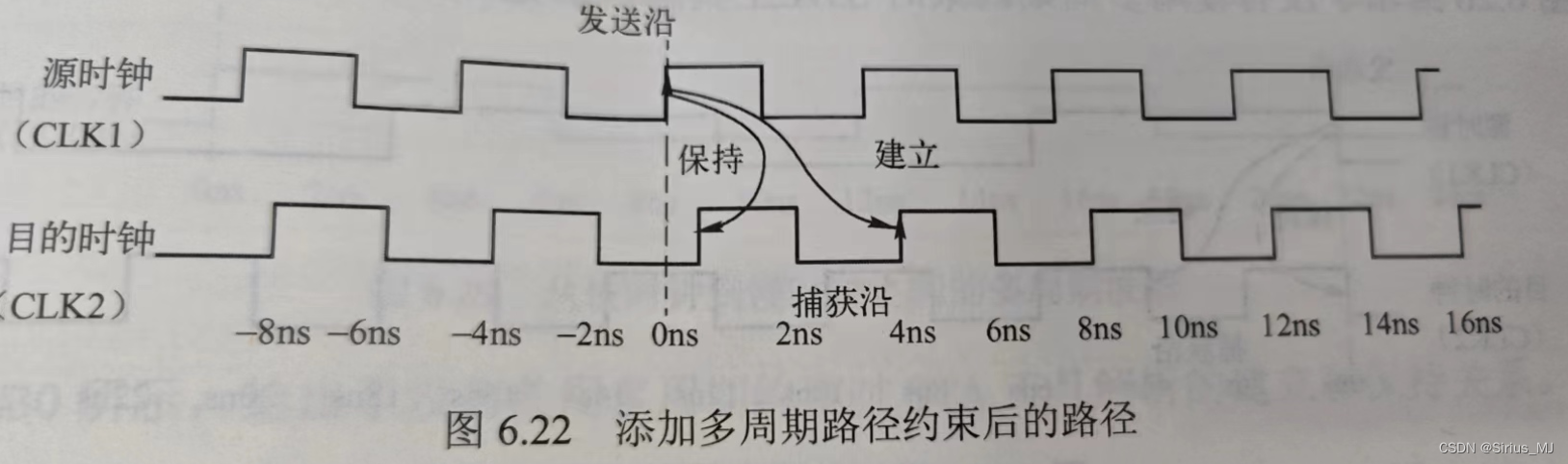

*若clk1和clk2相差0.3ns延迟则可能在时序检查时出现保持检查为-3.7ns的情况

对此应该添加多周期时钟约束

set_multicycle_path 2 -from [get_clocks CLK1] -to [get_clocks CLK2]

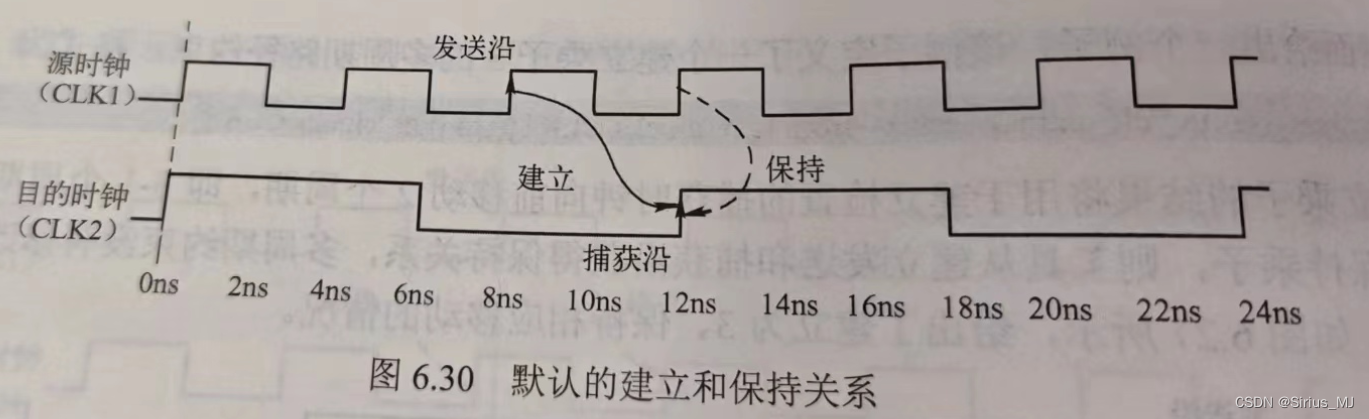

*从慢时钟到快时钟的多周期,假设CLK2频率是CLK1的3倍

此时应该建立一个乘3的多周期路径约束

set_multicycle_path 3 -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path 2 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2]

*从快时钟到慢时钟的多周期,假设CLK1频率是CLK2的3倍

set_multicycle_path 3 -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path -hold 2 -from [get_clocks CLK1] -to [get_clocks CLK2]

1543

1543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?