目录

1)主从触发器采样过程

首先,建立/保持时间,亚稳态都是为了描述触发器工作状态而产生的概念。所以要先了解触发器的工作原理。

Q:为什么要使用触发器?

在数字系统中,可以分为组合逻辑,时序逻辑两大类。

组合逻辑主要实现计算等数据处理,但是无法存储计算结果,之前的计算结果无法再次调用,最直观的就是无法实现经典负反馈电路,计数器等功能。

所以我们需要时序逻辑,主要负责数据调度,存储组合逻辑计算结果,在需要时再取出使用。

在数字系统中,有很多种触发器,例如SR触发器,D触发器,JK触发器等,由于D触发器结构简单,性能稳定,面积小,是最常用的触发器。

参考主从结构的D触发器。

采样过程

分析时钟由低变高期间,数据传输过程。(假设触发器是上升沿采样数据。)

CP低电平期间,主锁存器锁存D,这时主从锁存间的传输门TG3断开,数据变化不影响从锁存器。

CP高电平期间TG1断开,D变化不影响触发。TG3导通,数据能够传到从锁存器中,通过G3后从Q输出。

2)建立时间

3)保持时间

4)亚稳态原因分析

亚稳态定义:触发器违反了建立/保持时间的话,时钟有效边沿采样的数据就是不确定值,向后传输的结果是不可预知的,即亚稳态。

在CP低电平期间,允许数据D变化,主锁存器一直在锁存数据。CP从低变高前最后锁存到的数据才是有效数据。

数据在主锁存期间,假设数据D锁存一次需要的时间为T1,我们就定义T1为触发器的建立时间,在此期间数据不能发生变化。如果D在T1/2时刻变化,正在被锁存的数据被刷新,而剩下的T1/2时间不能完成数据D传输到G1的输出端。可能在通过G1时,G1的输入不是一个绝对的高电平,也不是绝对的低电平,一个中间电平可能导致反相器中N,P管都有一定程度的导通,所以G1的输出也不确定。这个不可预知的数据传输下去就可能导致亚稳态的发生。

亚稳态不是一定会发生:个人猜测,是因为数字电路中输入输入噪声容限?采样的中间电平如果落到Coms的输入噪声容限范围内,也能输出一个确定的高或低。

在同步电路中,所有的数据都是在同一个时钟的有效边沿变化的,没有亚稳态问题。

但是在多时钟系统中,接受到其他时钟域数据时,就很容易发生亚稳态问题了。

如图,a时钟域产生的a_dat传输到b时钟域,在b时钟域上升沿采样时数据发生变化,输出的b_dat就可能产生亚稳态(meta stable)问题。

Q:区分不同时钟的是特性是什么?

A:1)时钟频率、2)占空比、3)时钟相位

5)亚稳态处理方法

1)单bit同步策略

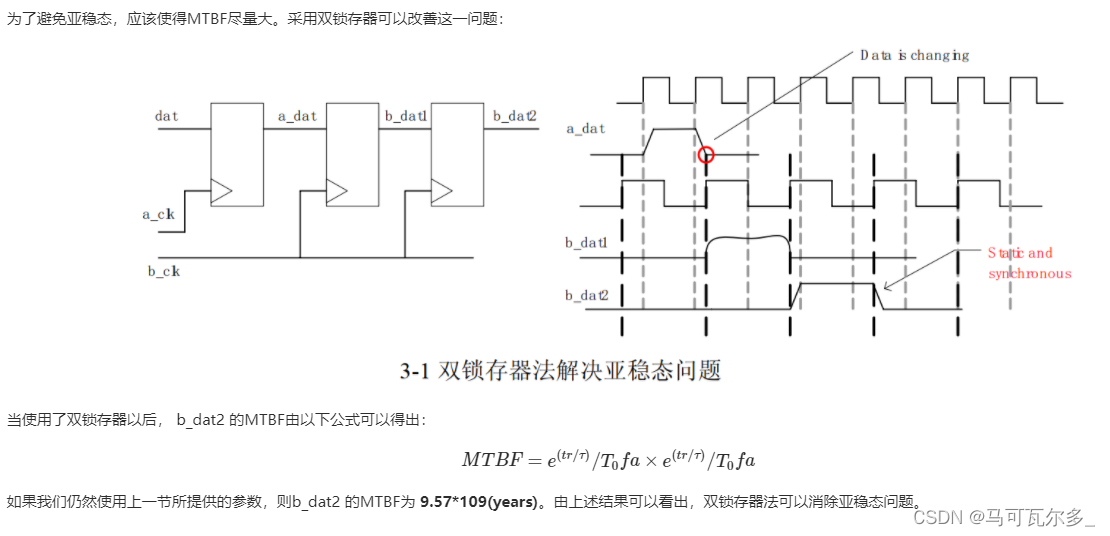

对于单Bit的跨时钟域信号,一般采用2级FF同步的方式避免亚稳态问题。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

Q1:为什么两级FF可以避免亚稳态?

A1:首先,亚稳态不会一直持续的状态,在跨时钟域传输时,亚稳态的发生是不可避免的,2FF避免的是亚稳态向后传播,导致在后级组合逻辑上产生随机性结果。

在第一段触发器FF1的有效边沿采样到变化值产生亚稳态,信号可能产生震荡变成不稳定状态,在第二个触发器采样时,可能采到0,也可能采到1。但是我们认为经过一个时钟周期后,亚稳态已经能够趋于稳定,在FF2采样时,不会产生不确定信号,能够输出稳定信号。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

Q2:如果跨时钟域信号值为1,如果经过FF1后输出0,那么虽然通过两段FF的同步,避免了亚稳态传播的问题,但是数据可能会出错?

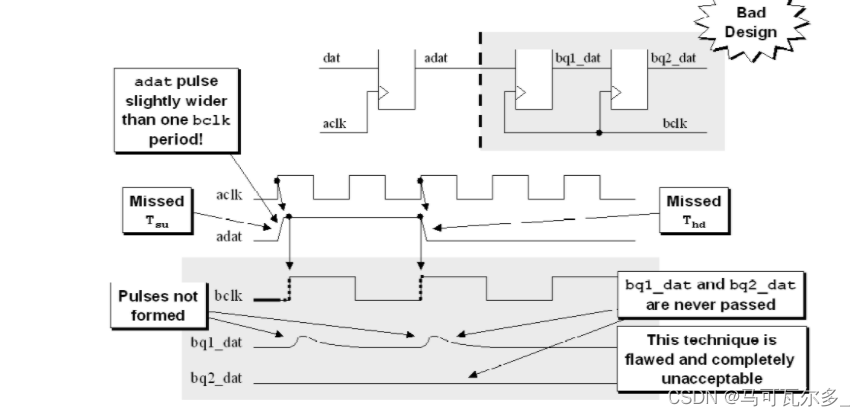

A2:确实会出现上述问题,所以在使用2FF处理异步信号时,要保证跨时钟域信号的有效脉冲宽度是目标时钟域的时钟周期长度的1.5倍或更多。

满足这个条件后,假设上升边沿在目标时钟域FF1触发了亚稳态,FF1的输入为1,但是输出端得到0值也没关系,因为在目标时钟域的下一个上升沿采样到的值一定是1。在两个时钟周期内输入数据保持为1,输出数据是01。满足1.5倍时钟周期条件下,数值1的状态一定会来,只是可能在第一拍就来了,可能在第二拍才来。

那为啥是1.5倍勒?刚好和目标时钟周期长度相同行不行?

不行,因为如果刚好在数据上升沿时触发了亚稳态,经过一个cycle后,在第二个上上升沿,可能还是要触发亚稳态,为了在第二个上升沿时保证数据时稳定状态,也就是不会再建立&保持时间周期内变化,我们期望有效脉冲宽度是目标时钟域周期的1.5倍。

那怎么才能让跨时钟域信号的脉冲宽度能够满足1.5倍周期长勒?

1)开环控制,设计电路时,开发人员就应该知道系统各个时钟的关系,输出跨时钟域信号时,就考虑清楚信号的有效宽度应该设定为多少。

2)握手

不知道目标时钟域的具体信息,A域输出的任意长度的data_a。在A域中通过一个FF,检测到data_a=1后,拉高data_a1,一直等到B域同步后信号反馈到A域经过2FF的同步后,在拉低data_a1。以此来保证跨时钟域信号的有效宽度。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

3111

3111

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?