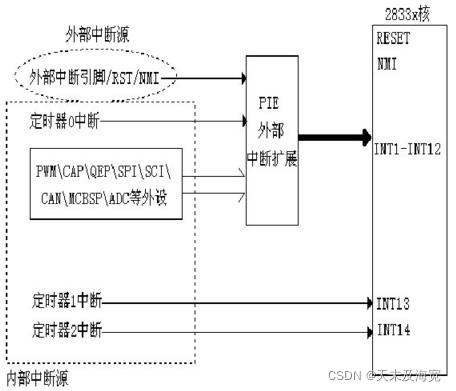

1. 中断线内部分配情况

(1) F28335内部有16个中短线,其中包括2个不可屏蔽中断(RESET和NMI)与14个可屏蔽中断;

(2) 可屏蔽中断中,TIM1和TIM2产生的中断请求通过INT13和INT14中断线到达CPU;这两个中断已经预留给实时操作系统了;

(3) 剩余的12个可屏蔽中断可供外部中断和处理器内部单元使用;

但是 F28335外设中断源总共有58个;

矛盾点:外设中断源58个,内部可操作的中断线只有12个;故引出PIE模块,用于中断线复用;

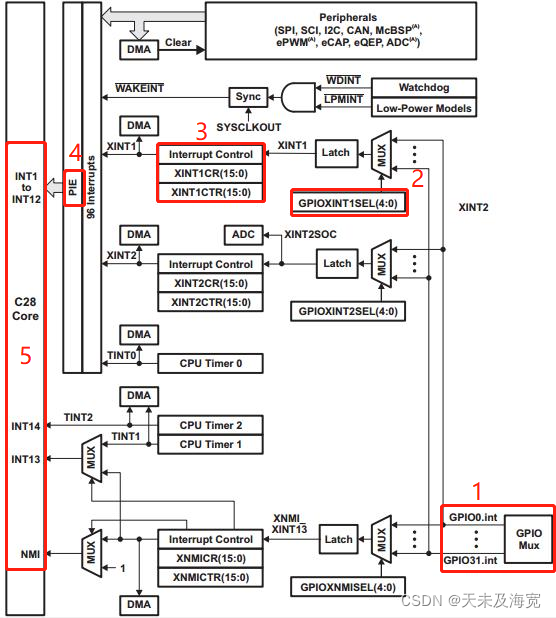

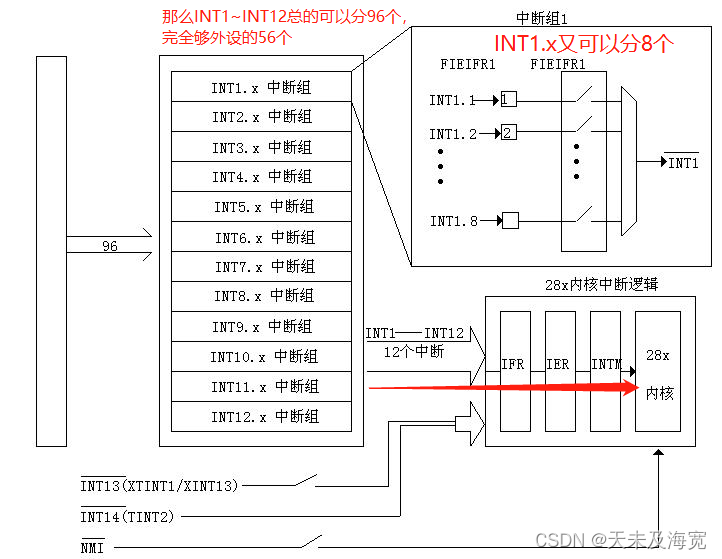

中断源与IO复用结构图:

2. F28335中断机制

F28335中断采用的是3级中断机制,分别是外设级中断,PIE级中断和CPU级中断;

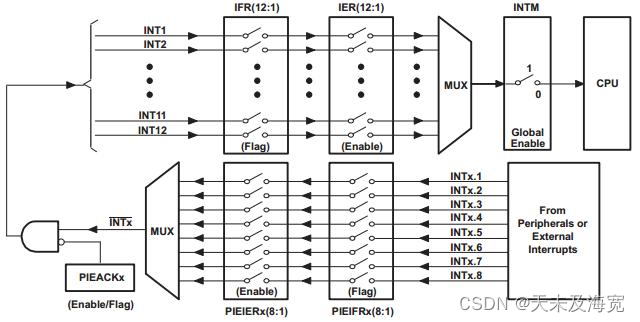

上图中下部分为PIE小组响应外设中断的过程,上半部份为CPU响应12组PIE中断的过程;

(1) 外设级中断

外设产生了中断事件,该外设对应的标志寄存器(IF)响应的位将被自动置位;若外设对应的中断使能寄存器(IE)中断响应的使能位正好置位(软件控),则外设产生的中断将向PIE控制器发出中断申请;若对应的外设级中断没有被使能,就相当于该中断被屏蔽,不会像PIE提出中断申请;此时的中断标志寄存器将保存不变,一直处在中断置位状态,要使该中断信号消失,中断标志寄存器需要复位;若没有复位,一旦中断使能位被使能,同样会向PIE申请中断;

当进入中断服务后,有部分硬件外设会自动复位中断标志寄存器,多数外设需要在中断服务中复位手动复位中断标志寄存器;

(2) PIE级中断

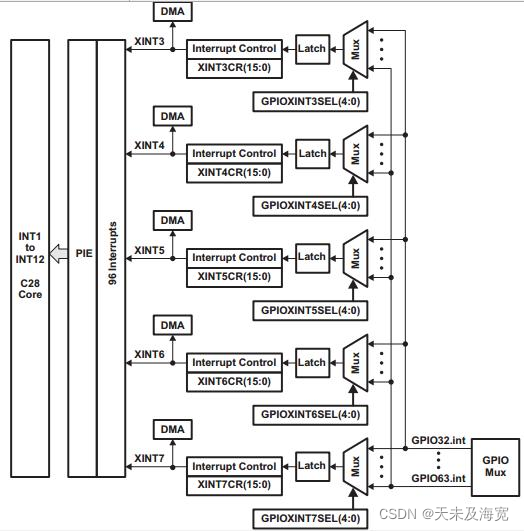

由于CPU没有能力处理所有外设级的中断请求,所有cpu让出12个中断线交给PIE模块进行复用管理;

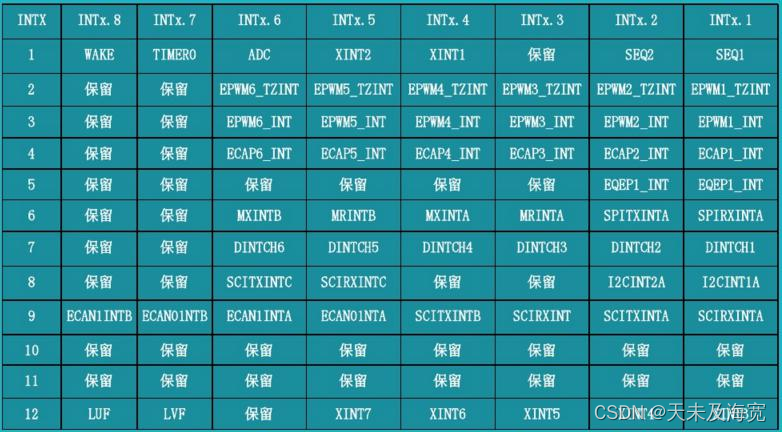

上图说明:PIE将外设中断分成了12个组,分别对应着CPU的12个可屏蔽中断线,每一组由8个外设级中断组成,这8个外设中断分别对应相应外设接口的中断引脚;PIE通过8选1选择器将这8个外设中断组成1组;

与外设级中断类似,在PIE模块内有中断标志位(PIEIFRx)和使能位(PIEIERx.y);而且每组PIE中断(INT1~INT12)有一个响应标志位(PIEACK);

一旦PIE控制有中断产生,相应的中断标志位(PIEIFRx.y)将置1;

若相应的PIE中断使能位也置1,则PIE将检查相应的PIEACKx以确定CPU是否准备响应该中断; 若相应的PIEACKx位清零,PIE向CPU申请中断;若PIEACKx置1,PIE将等待相应的PIEACKx清零才向CPU申请中断;

一旦响应后,需要将PIEACKx相应位清零,以让它能够响应该组后边过来的中断;

(3) CPU级中断

一旦CPU申请中断,CPU级中断标志位(IFR)将置1;中断标志锁存到标志寄存器后,只有CPU中断使能寄存器(IER)或中断调试使能寄存器(DBGIER)响应位使能和全局中断屏蔽位(INTM)被使能才会响应中断申请;

3. 中断向量

cpu响应中断,就是cpu要指向相应的中断服务程序;中断服务程序的人口地址就是中断向量;入口地址使22位的,需要2个16位(共32位)的寄存器存放,地址的低16位保存该该向量的低16位,地址的高6位保存到另一寄存器的高6位,更高的10位保留;

(1) 中断向量分配

PIE最多可支持96个中断,每个中断都有自己对应的中断向量,即每个中断源都对应着自己的中断服务入口地址,这些中断向量均连续存放在RAM中,这就构成了整个中断向量表;

在响应中断时,cpu自动从中断向量表中获取相应的中断向量;

cpu获取中断向量和保存重要寄存器所需9个cpu时钟周期;

cpu响应中断是通过中断线的,而且只能1次响应其中1条中断线,有可能同一时刻16条中断线上的请求同时到达cpu,这就要对各个中断请求进行优先级定义;

(2) 中断向量表

中断向量表友256x16B(4k)的SRAM内连续存放,如果这部分空间不作为PIE模块时,可用作数据RAM;复位时PIE向量表内容没有定义;

CPU的中断优先级从高低为: INT1~INT12; 每组PIE控制的8个中断优先级依次是:INTx.1-INTx.8;

| INTx.1~INTx.8地址范围 | |

|---|---|

| INT1.1~INT1.8地址范围 | 0x0D40~0x0D4E |

| INT2.1~INT2.8地址范围 | 0x0D50~0x0D5E |

| INT3.1~INT3.8地址范围 | 0x0D60 ~0x0D6E |

| INT4.1~INT4.8地址范围 | 0x0D70 ~0x0D7E |

| INT5.1~INT5.8地址范围 | 0x0D80 ~0x0D8E |

| INT6.1~INT6.8地址范围 | 0x0D90 ~0x0D9E |

| INT7.1~INT7.8地址范围 | 0x0DA0 ~0x0DAE |

| INT8.1~INT8.8地址范围 | 0x0DB0 ~0x0DBE |

| INT9.1~INT9.8地址范围 | 0x0DC0 ~0x0DCE |

| INT10.1~INT10.8地址范围 | 0x0DD0 ~0x0DDE |

| INT11.1~INT11.8地址范围 | 0x0DE0 ~0x0DEE |

| INT12.1~INT12.8地址范围 | 0x0DF0 ~0x0DFE |

4. 中断向量映射方式

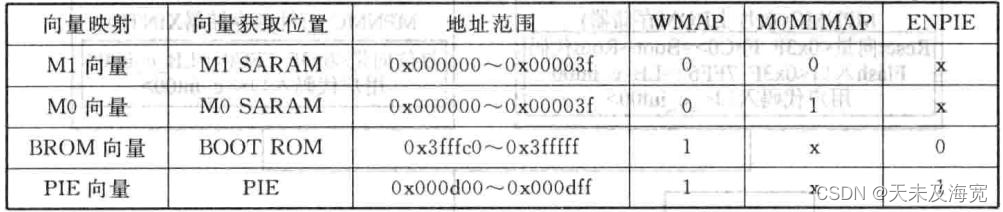

中断向量表可以被映射到4个不同的存储区域,实际应用中,只能使用PIE中断向量表映射区域;

其中:M1和M0供TI公司测试使用;M0和M1映射区域可作为SARAM使用,可以随意使用,没有任何限制;

复位后器件默认的中断向量表为BROM向量;VMAP和MOM1MAP模式均被设置为1;而ENPIE模式强制为0; 复位向量始终从boot ROM获取;

复位程序引导(BOOT)完成后,用户需要重新初始化PIE中断向量表,应用程序使能PIE中断向量表,并从PIE向量表中获取中断向量;

5. 复位中断的操作过程

在清除PIEIFR和PIEIER时,需要遵循以下3个规则:

1. 不要用软件编程清除 PIEIFR 的位:清除 PIEIFR 寄存器的位时,有可能会使产生的中断丢失;要清除 PIEIFR 位时,还未被执行的中断必须被执行,如果用户希望在执行正常的服务程序之前就要清除 PIEIFR 位时,需要遵循以下步骤:

(1) 设置 EALLOW 位为 1,允许修改 PIE 向量表。

(2) 修改 PIE 向量表,使外设服务程序指针向量指向一个临时的 ISR,这个临时的 ISR 只执行一个中断返回(IRET)操作;

(3) 使能中断,使中断执行临时中断服务程序;

(4) 在执行完中断服务程序之后,PIEIFR 位将被清除;

(5) 修改 PIE 向量表,重新映射外设服务程序到正确的中断服务程序;

(6) 清除 EALLOW 位

2. 软件设置中断优先级

3. 使用 PIEIER 禁止中断;

6. 外设复用中断向CPU申请中断的过程

1. 任何一个PIE中断组的外设或外设中断产生中断.若外设模块内的中断被使能,中断请求将被送到PIE模块;

2. PIE模块将识别出PIE中断组x内的y中断(INTx.y)申请,然后相应的PIE中断标志位被锁存:PIEIFRx.y=1;

3.PIE的中断如要送到CPU需满足下面两个条件:

(a) 相应的使能位必须被设置(PIEIFRx.y=1);

(b) 相应的PIEACKx位必须被清除;

4. 若满足3的两个条件,中断请求将被送到CPU并且相应的寄存器被置1(PIEACKx=1);PIEACKx位将保持不变,除非为了使本组的其他中断向CPU发出申请而清除该位;

5. CPU中断标志位被置位(CPU IFRx=1),表明产生一个CPU级的挂起中断;

6. 如果CPU中断被使能(CPU IERx=1或DBGIERx=1),并且全局中断使能(INTM=0),CPU将处理中断INTx;

7.CPU从PIE中获取相应的中断向量;

8. 对于复用中断,PIE模块用PIEIERx和PIEIFRx寄存器中的值确定响应的中断向量地址;

CPU进入中断服务程序后,将清除PIEIFRx.y位;

7. 可屏蔽中断处理

本质即使操作PIEIFR,PIEIER,IFR,IER,INTM相应寄存器;

8. 不可屏蔽中断处理

以 XNMI_XINT13 引脚外部中断设置为例; 只要配置好相应的引脚配置寄存器就可以了,因为NMI优先级最高,CPU必须响应,不需要配置CPU;

1363

1363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?