SignalTap II使用技巧_2

这篇文章主要是对上一篇文章的一些补充,链接: SignalTap II使用技巧_1.

如何观察被Quartus优化掉的reg或者wire型变量

这里需要注意的是,如果我们发现添加的信号变成了红色,或者有些reg与wire定义的信号可以观察,有些不可以,这是因为reg与wire被Quartus软件优化掉了,导致无法使用SignalTap观察。这里有两种方法解决这个问题,第一种就是将reg与wire信号改成输出端口信号,但这种方式较为繁琐;第二种方法就是在待观察的wire信号旁边加上/synthesis keep/;对于reg信号则加/synthesis noprune/,如下所示:

wire [23: :0] counter/*synthesis keep*/;

reg [23: :0] counter/*synthesis noprune*/;

SignalTap II文件的使能和失能

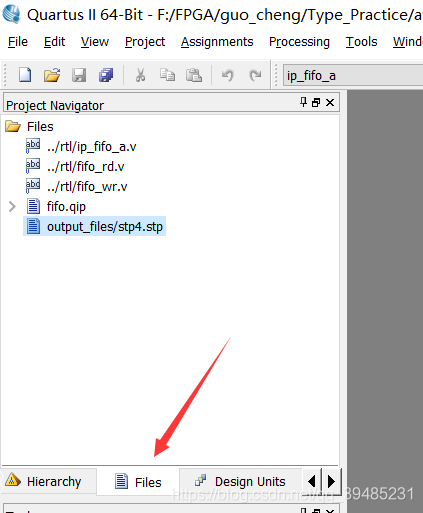

有时候我们在设计时需要用SignalTap II来验证,但是验证成功之后,我们又不需要SignalTap II了,因为如果我们的过程中有SignalTap 文件。他会占用我们的FPGA资源,关于这点,可以参考上一篇文章。其中一种办法是在这里把它从工程中去掉。

但是这种操作的麻烦之处是,万一以后我们要修改工程,又需要仿真,这个时候我们又要新建一个SignalTap,所以这里就出现了第二种操作方法。

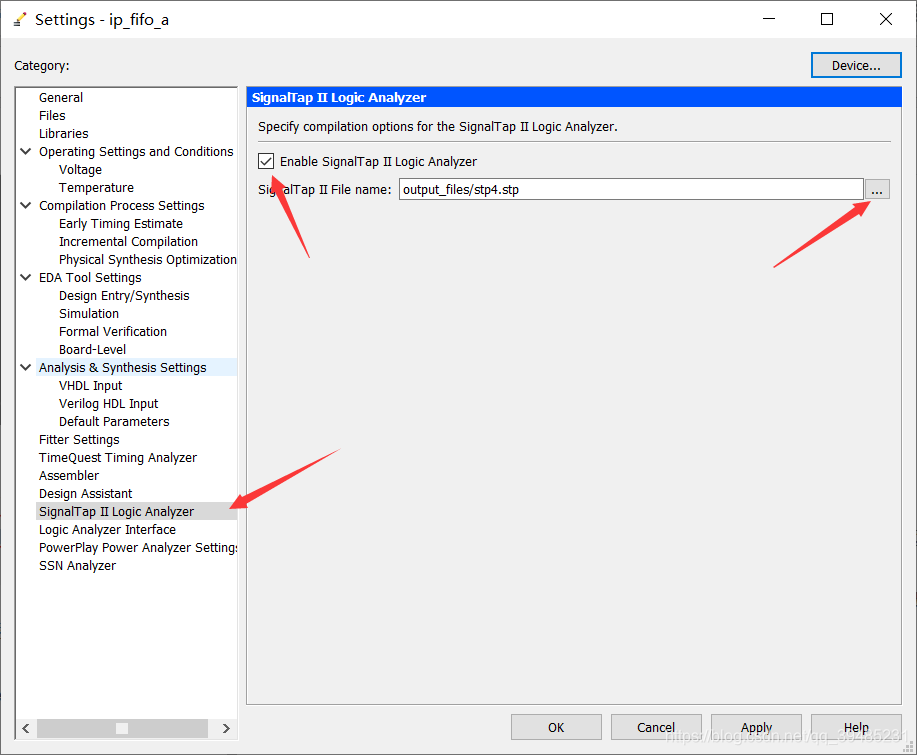

在Assignments→settings→SignalTap II logic analyzer中修改或者使能我们的stp文件。

这种方法主要是出于长远的考虑,对于工程以后的维护会省去很多麻烦。

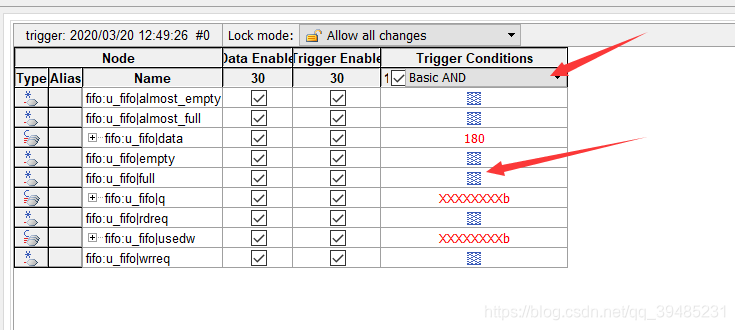

Trigger Condition的设置

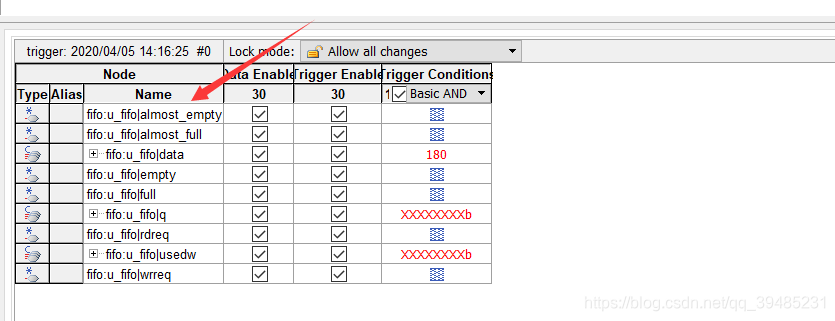

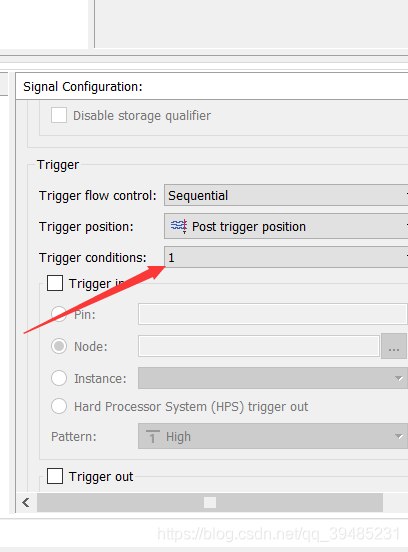

1.Trigger Condition个数的设置

可以在SignalTap的右边框的Signal Configuration中的Trigger→Trigger Condition中修改触发条件的级数

多级触发的意思就是依次地满足触发条件才可以,满足了第一级以后,再满足第二级,第三极……然后才开始采集数据。

2.触发条件的设置

在Basic AND那栏可以选择同一列的触发条件的逻辑关系,当为Basic AND时,表示触发条件要同时满足才能开始记录信号;当为Basic OR时,表示触发条件只要其中一个条件满足就能开始记录信号;有时候我们的触发条件不能用简单的高低电平或者上升沿、下降沿,可能是多个信号的逻辑电路,这时候需要使用高级触发条件Advanced,这种模式可以编辑触发条件的逻辑关系,具体的操作方法可以参照这篇文章 https://www.cnblogs.com/aikimi7/p/3511337.html

先更到这里,以后有遇到其他有意思的操作再继续更新

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?