一、SignalTap II简介

SignalTap II借用了传统逻辑分析仪的理念以及大部分的功能,使用SignalTap II无需额外的逻辑分析设备;

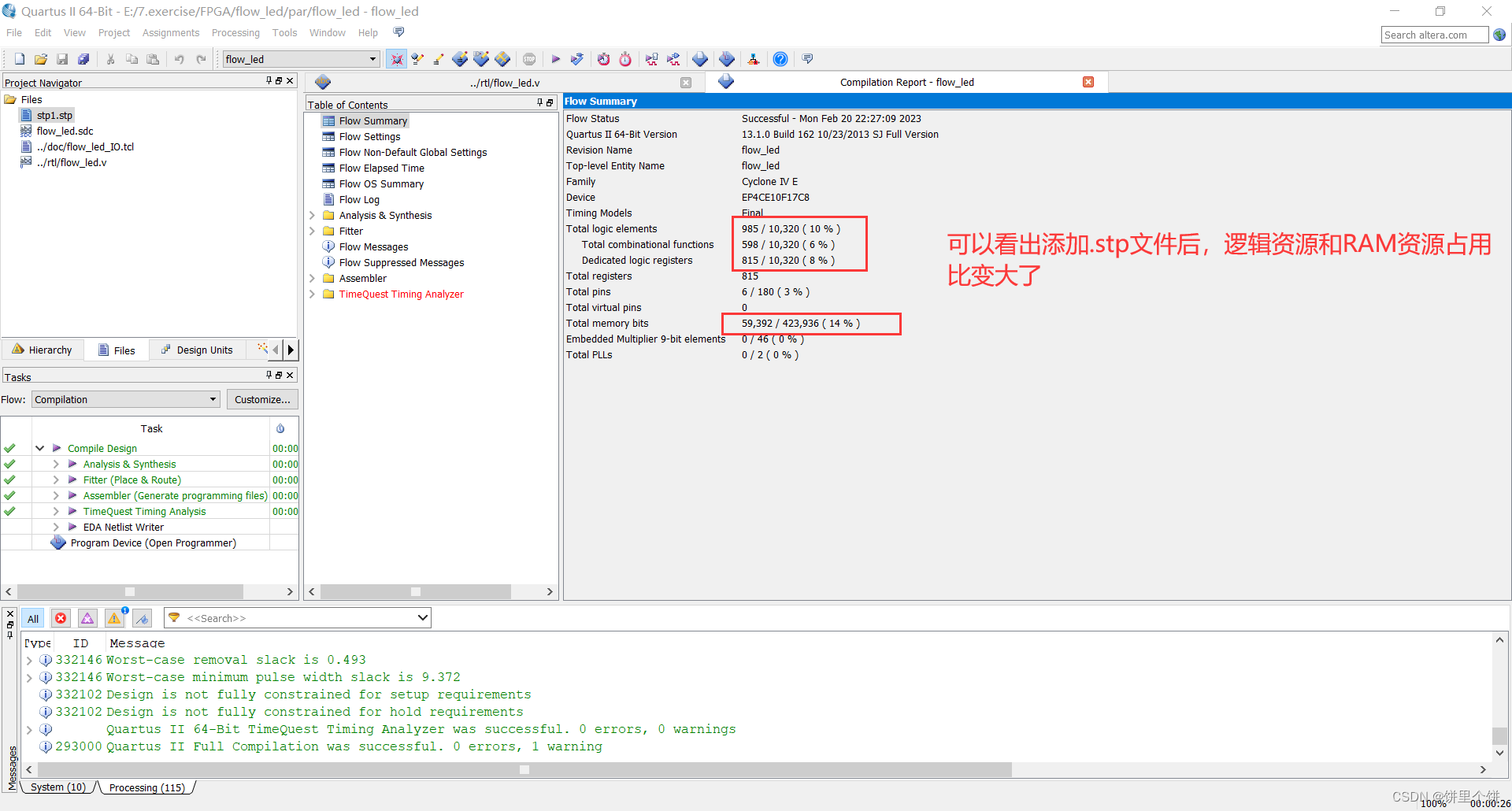

SignalTap II在工程中额外加入了模块来采集信号,所以使用SignalTap II需要消耗FPGA的逻辑资源和RAM资源。

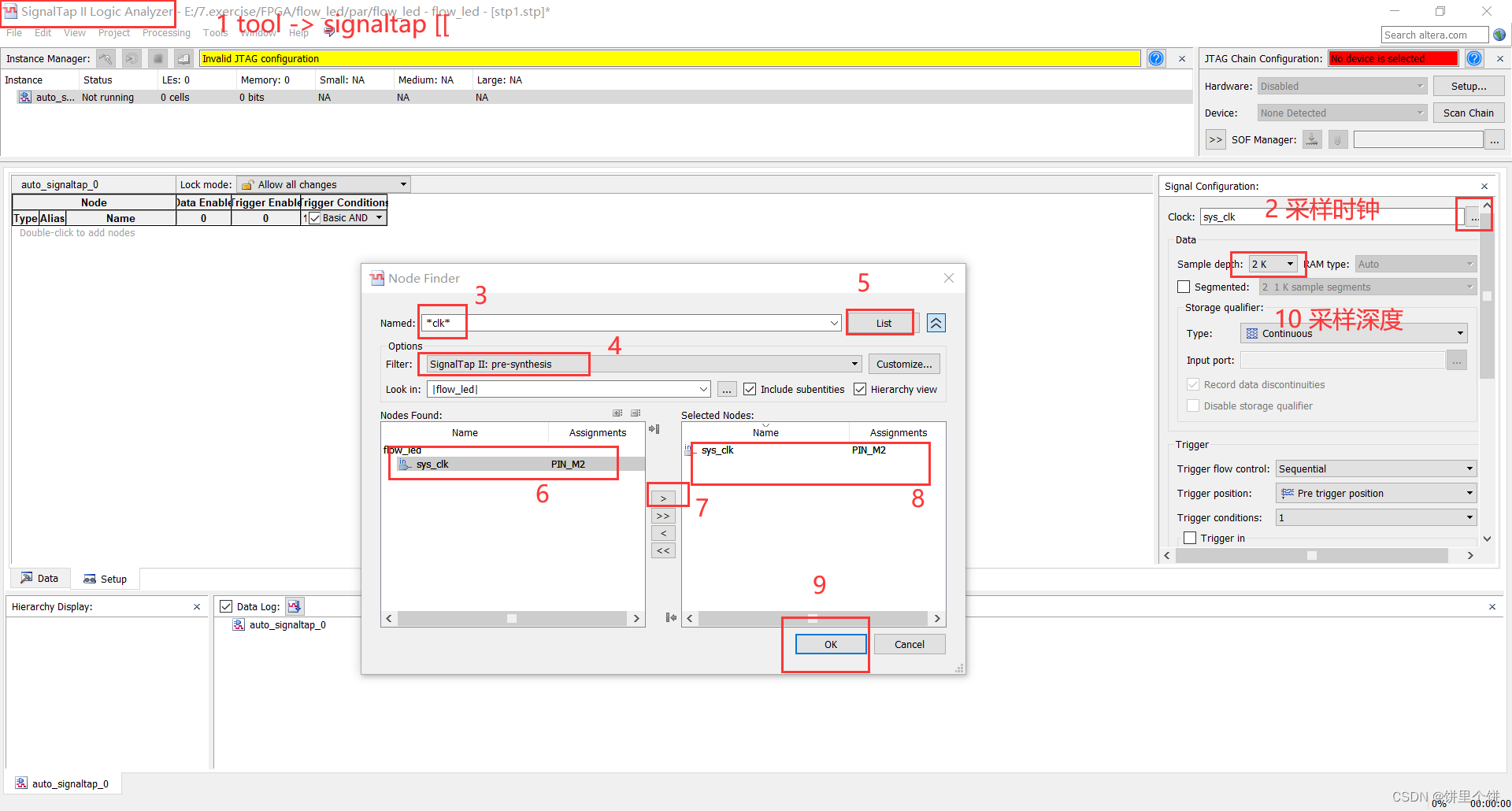

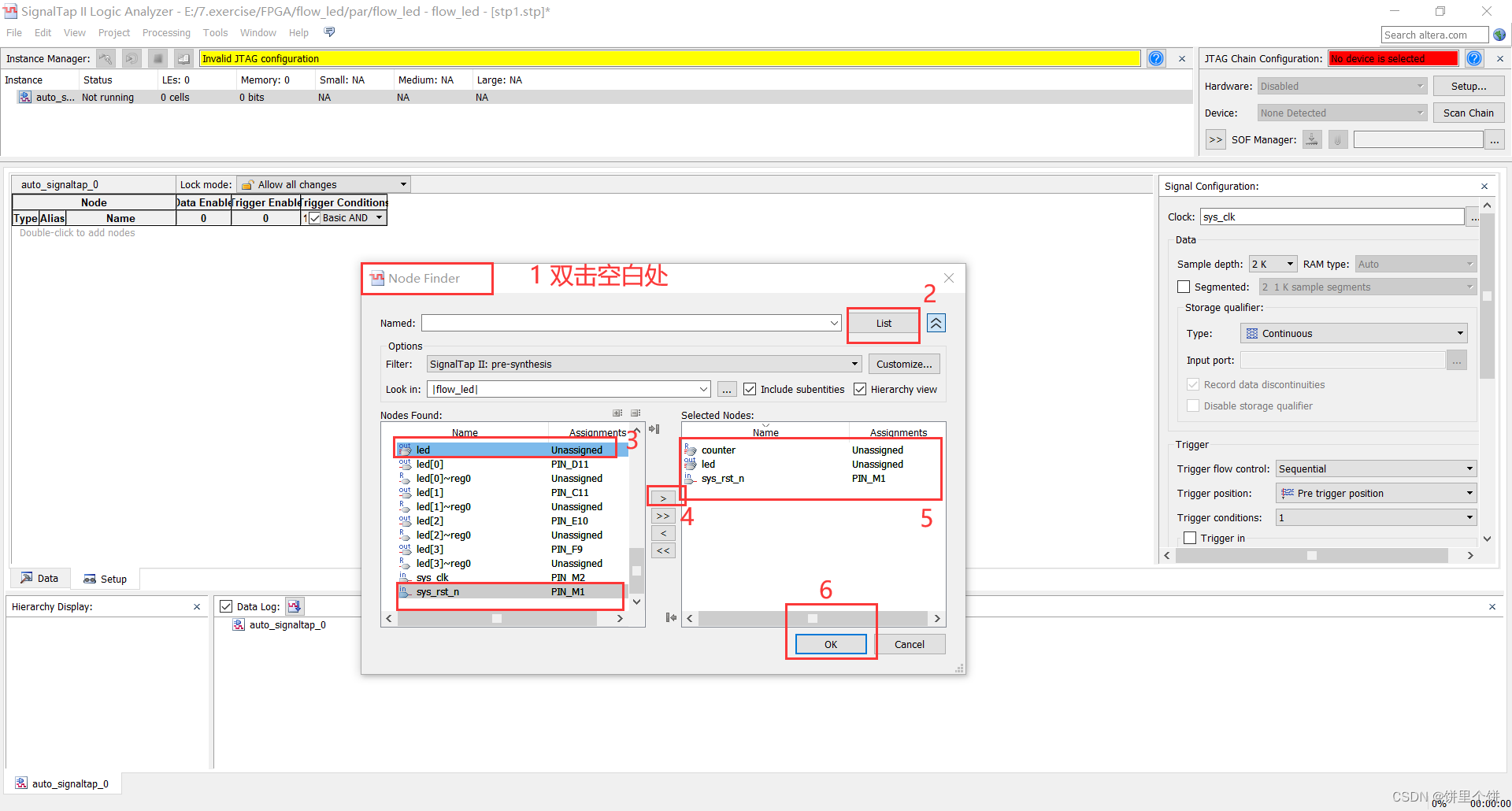

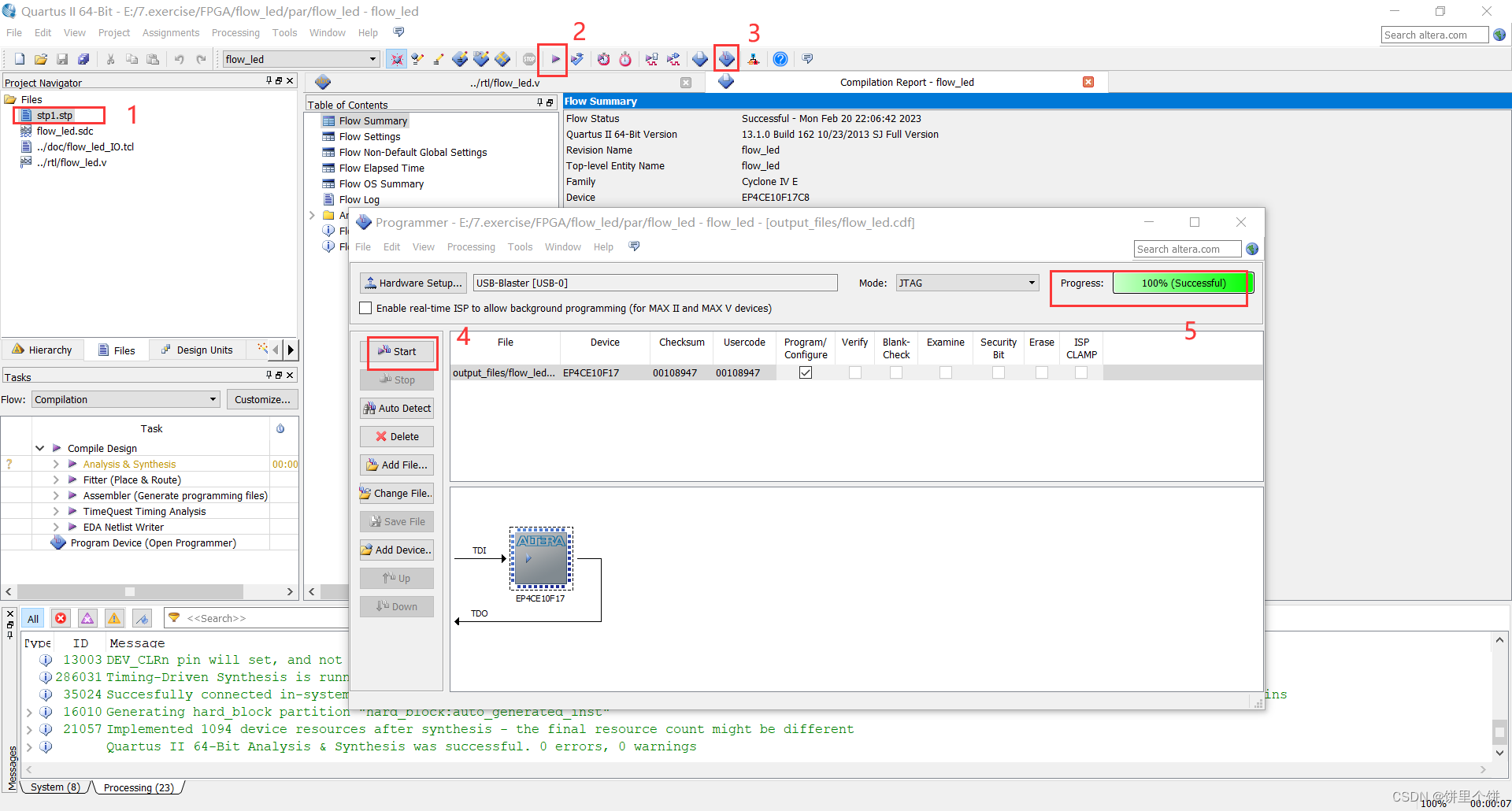

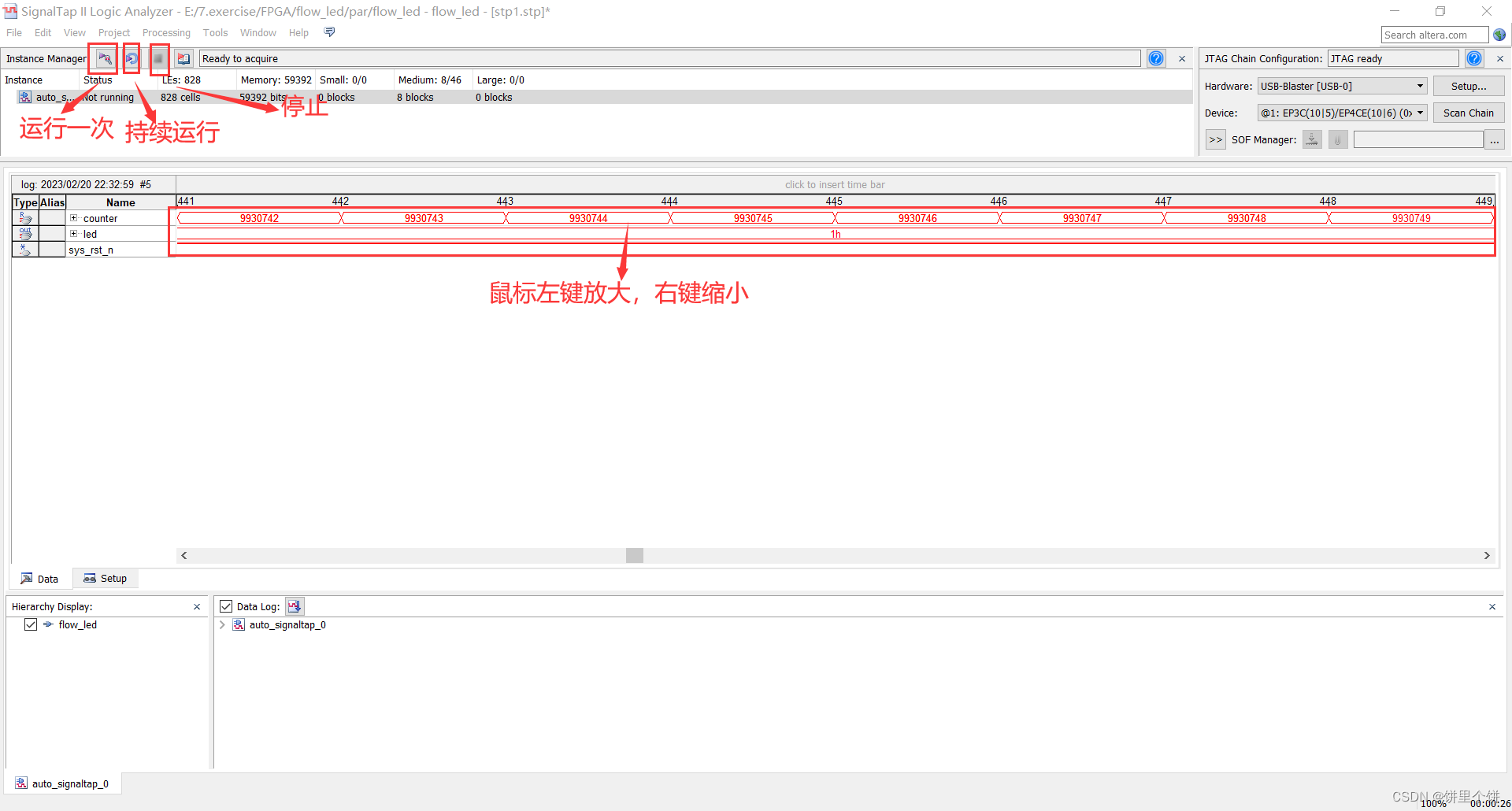

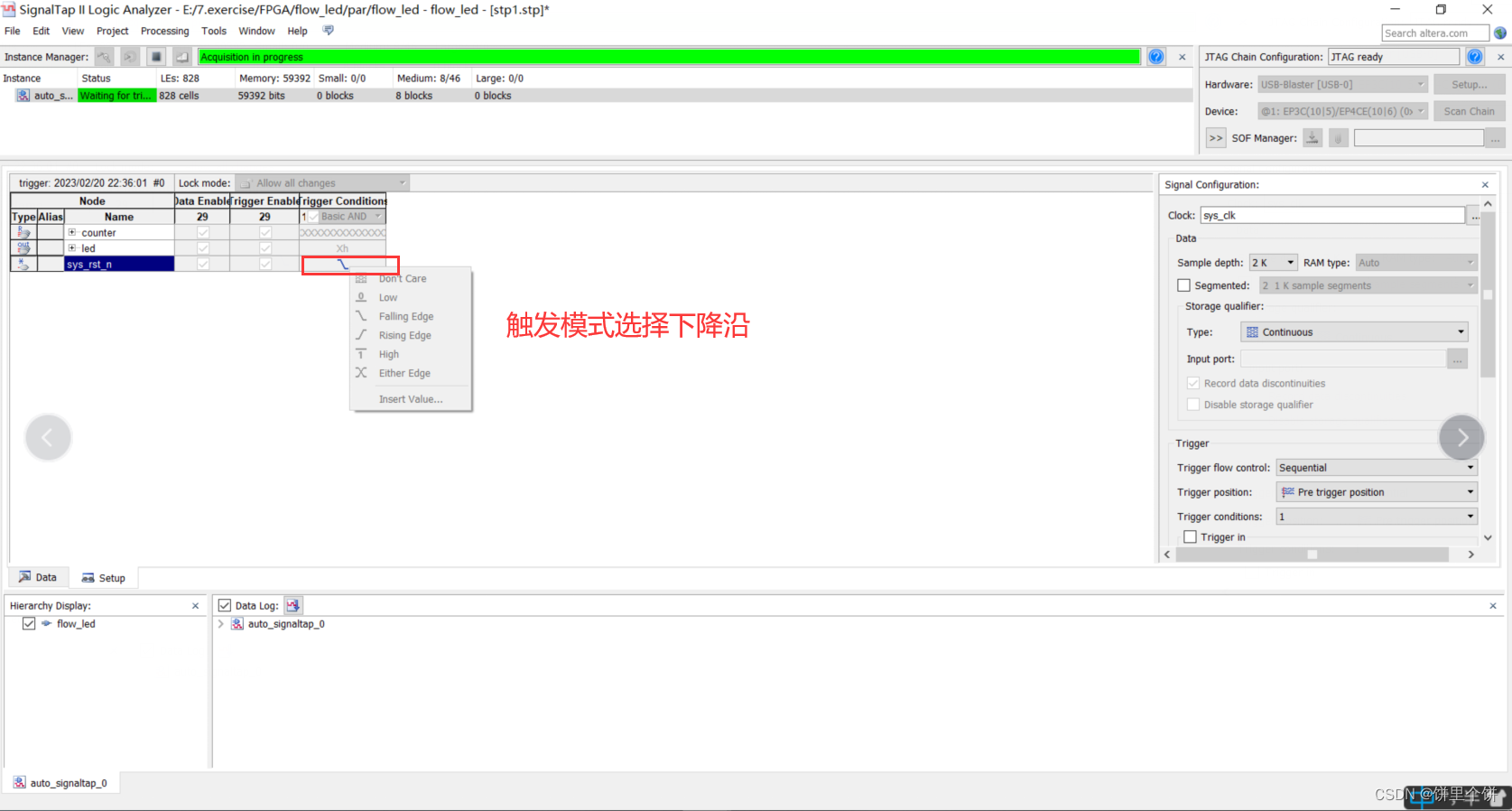

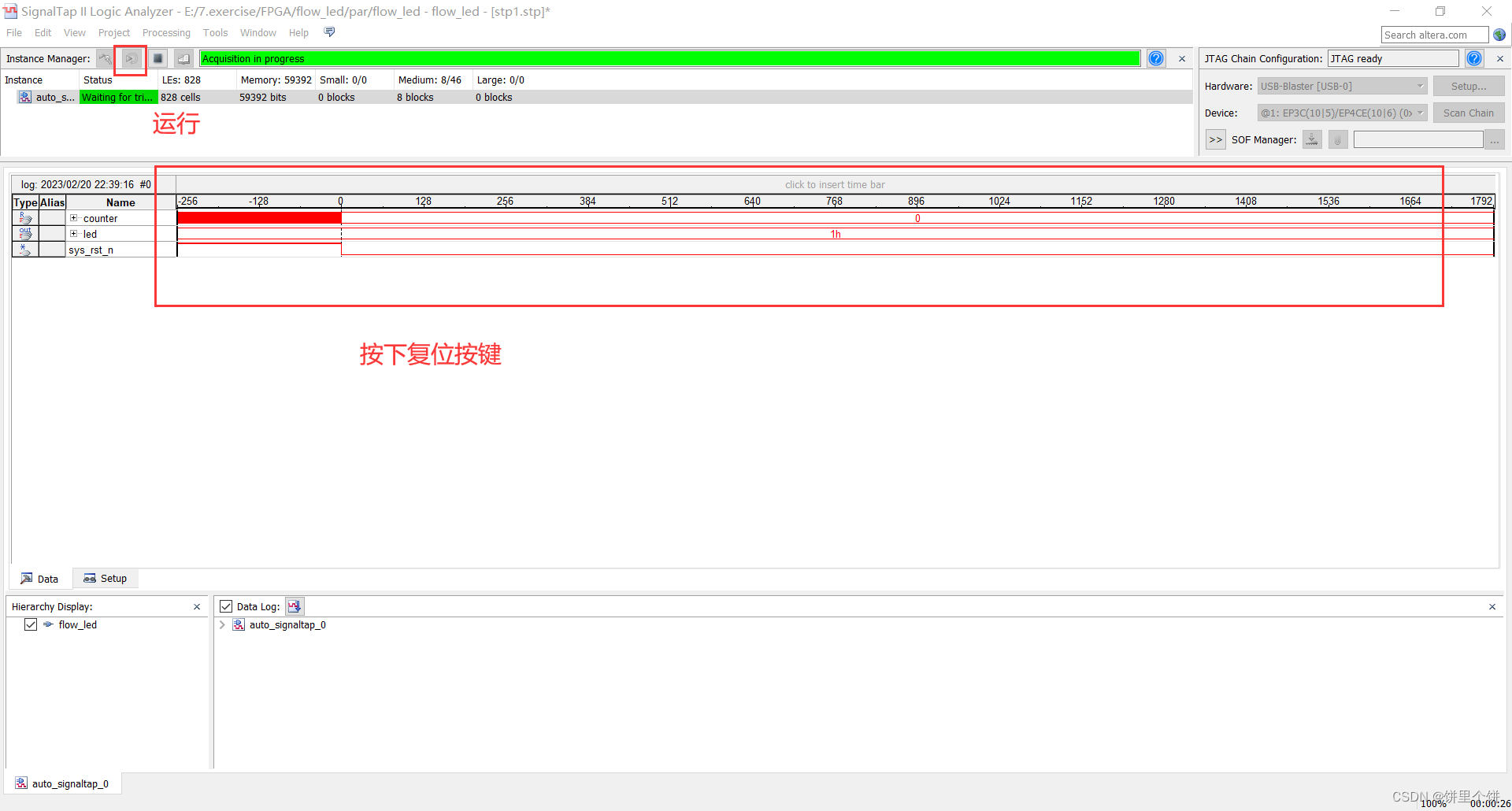

二、软件的使用

三、防优化语句

在程序中为了方便调试会添加一些测试信号,这些信号对输出结果没有用,就会被优化掉,为了观察这些信号就需要添加防优化语句。

/*优化前*/

reg [1:0] reg_test;

wire [1:0] wire_test;

/*优化后*/

reg [1:0] reg_test/*synthesis noprune*/;

wire [1:0] wire_test/*synthesis keep*/;

四、流水灯程序

//流水灯模块

module flow_led(

input sys_clk,

input sys_rst_n,

output reg [3:0] led

);

reg [23:0] counter;

//计数到1000_000 - 1 = 0.2s

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

counter <= 24'd0;

else if(counter < 24'd1000_0000 - 1'b1)

counter <= counter + 1'b1;

else

counter <= 24'd0;

end

//0001 → 0010 → 0100 → 1000 → ...

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

led <= 4'b0001;

else if(counter == 24'd1000_0000 - 1'b1)

led <= {led[2:0],led[3]};

else

led <= led;

end

/*

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

counter <= 24'd0;

else if(counter == 24'd1000_0000 - 1'b1)

counter <= 24'd0;

else

counter <= counter + 1'b1;

end

*/

endmodule

226

226

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?