一、E906移植----项目介绍、开发环境与实验平台搭建

0.前言

时间来到2022年6月,最近参加比赛,做RISCV的FPGA移植相关内容,选用的是平头哥的玄铁E906开源项目。目前玄铁E906的fpga移植教程基本没有,所以这个专栏打算介绍自己移植过程中遇到了一些问题。后续会涉及到基本仿真平台搭建、项目代码在FPGA的移植与搭建、在FPGA上实现uart串口输出、以及E906上的printf函数重映射到串口,视情况可能会涉及jtag(程序调试下载)、flash控制(程序固化)、memory控制(调用外部ddr3内存)等构建一个soc的基本模块。

默认FPGA平台:zynq7020

本文则主要简单介绍一下选用的riscv项目基本情况、开发环境的获取、官方开源项目仿真平台搭建。

1.项目简介

1.1 简介

目前一些开源的riscv项目包括像国科大的致力于高端的香山riscv项目,中高端的平头哥的玄铁C910(已成功移植andriod),还有弱一点的玄铁C906(全志D1芯片),上述基本上都成功流片,目标频率超过1Ghz,对标的是arm A系列的MPU。

适合一些低复杂度应用场景的项目出名的有芯来科技的蜂鸟E203项目以及平头哥的玄铁E902(wujian100平台使用的riscv核心)。这两个riscv核都是采用的2级流水线,对标的是arm cortex-m0+,强调所谓的低功耗、实时性。

玄铁E902我没具体移植过,但蜂鸟e203的整个项目是比较完整的,覆盖从硬件RTL、软件c历程代码、平台仿真、fpga工程创建、程序jtag在线下载全流程,使用官方的工具链,做少量修改就可以完成fpga的移植,包括各种命令Makefile、约束tcl脚本都有写官方好的参考。详细靠谱的E203移植教程强烈推荐参看“芯王国”的相关博客:https://blog.csdn.net/weixin_40377195/category_10730490.html?spm=1001.2014.3001.5482

1.2为什么用玄铁E906?

先说一下蜂鸟E203,在zynq7020上进行基本的移植后,资源占用20%左右(fpga共约53k逻辑资源)。但是其最高逻辑层级来到45级左右,这正是2级流水最大的硬伤,最终的结果就是zynq7020-2的平台下,频率最高勉强只能到40-50Mhz。要知道该fpga在只有4、5个逻辑层级下时序最高是能跑到500Mhz的。

平头哥这边,E902也是两级流水,估计和E203也差不了多少。所以要提高频率与性能,5级流水线的cpu核是一个很好的过渡。

C906和E906都是5级流水,但是C906的性能更强,64bit ,外设总线使用的AMBA4.0的AXI4.0总线,其整个soc集成了分支预测、cache、MMU等,性能上感觉对标ARM A9/A7 核,全志的D1芯片便是基于c906核心,可以运行linux。

E906则主要面向嵌入式,32bit ,外设soc总线基于AMBA3.0 的AHB-lite和APB总线。对应平头哥的asic产品ch2601,最高能跑到200+Mhz,性能比stm32f4强,应该对标stm32f7。

总之,2级的e203和e902性能不太够,想试试5级流水的cpu,而c906比较复杂了不利于上手,E906介于两者间。另外,其实在后面完成基本移植后可以发现,E906在zynq7020移植后,主要逻辑的lut占用30k左右,来到65%,是一个资源占用率比较合适的区间,关键路径逻辑层级25左右。此时频率最高也只能跑到50Mhz,但这是由于资源占用较高造成的,如果换成同系列但资源更多的的z7045,则时序能跑80Mhz。

所以,E906目前其难度,资源占用、逻辑层级都比较适合我手里的FPGA硬件。

2.开发环境

开发环境在linux上进行,VMw中开的虚拟机。

用到的工具包括:RTL仿真工具-- vcs或iverilog;波形查看-- verdi或gtkwave; fpga 工具-- vivado 2019.1;另外最好把QuestaSim(win下叫modelsim)也装上。最后最重要的是要把这些装好的工具设置好全局路径。

这里我用的,也非常推荐这位老哥 “芯王国” 的全套虚拟机IC开发学习工具(免费的!!仅供学习!!他csdn号、微信号、b站都有介绍),不想费时间去捣腾工具安装的话,他的完整版拿来基本就能直接用,也有教程。

3.项目实验平台搭建

首先要做的就是把平头哥官方的开源项目和工具链资源下载下来,然后跑通官方hello_world例程.

3.1 项目资料包准备

1.源码包:https://github.com/T-head-Semi

下载其中的 opene906整个项目包。

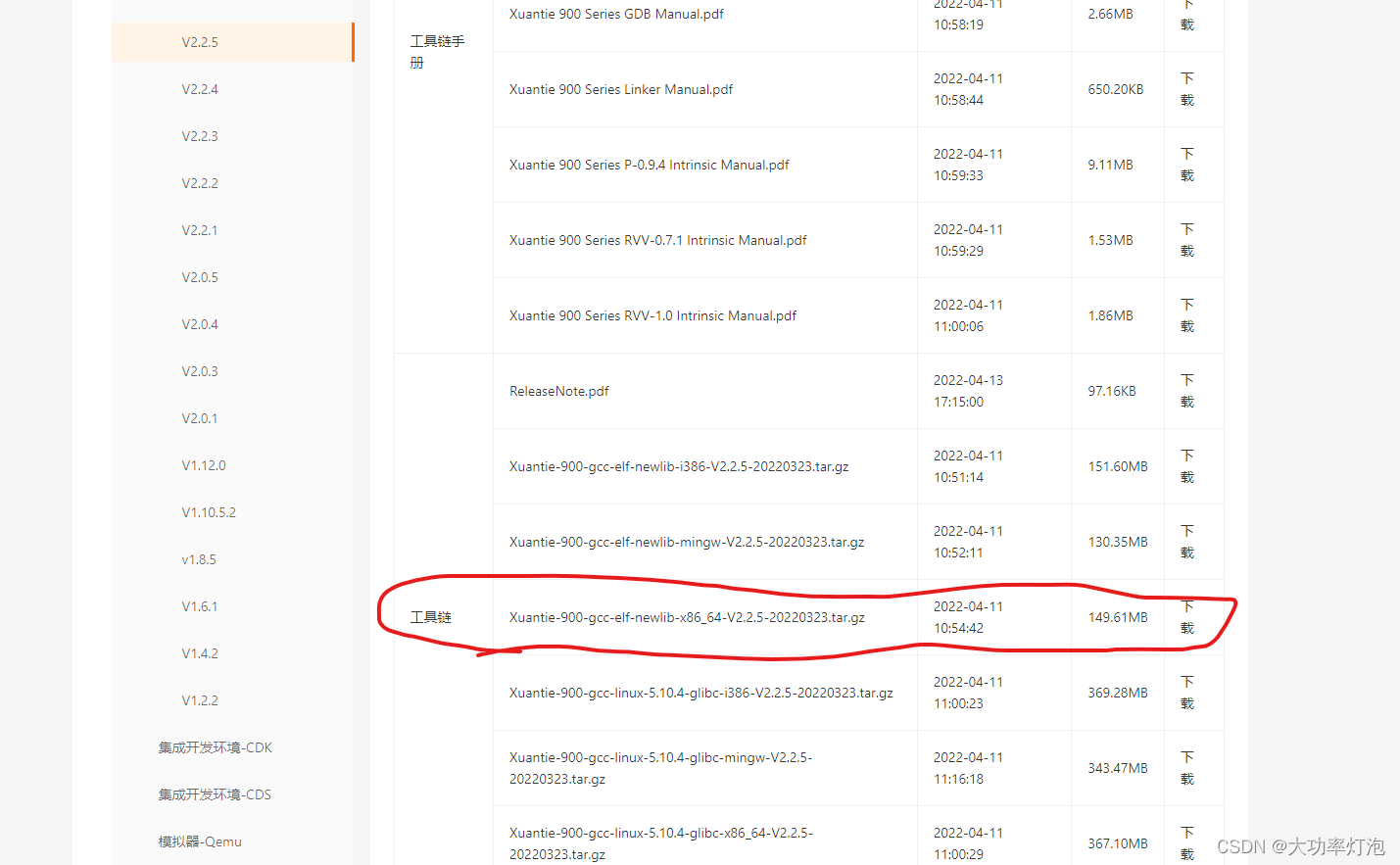

2.平头哥编译工具链:https://occ.t-head.cn/community/download?id=4049193882418745344

下载最新的裸机版(Xuantie-900-gcc-elf-newlib-x86_64-V2.2.5-20220323.tar.gz)

3. 将这两个包放进linux中。

3.2 设置shell与环境变量

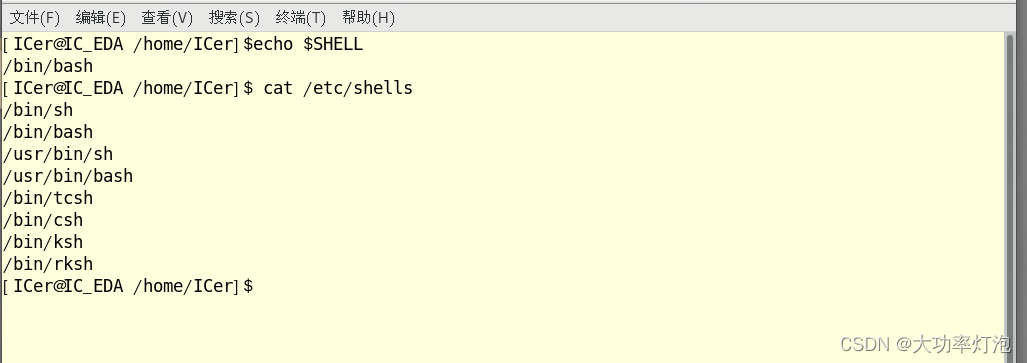

1.检查shell工具

一般linux下默认的shell工具是bash,但是E906的仿真工具链需要跳转到csh下来执行, 可以打开shell 使用 echo $SHELL查看当前工具,也可以用 cat /etc/shells 来查看当前环境是否以已经安装了csh,没有的需要自行装上。

2. 设置RTL路径和工具链路径为环境变量

环境变量就类似于一个宏定义,目的就是让环境下的工具都能检索到。值得注意的是,这里是给csh设置而不是给bash。

① 解压E906的项目资源包和工具链包,建议把 opene906-main 和 Xuantie-900-gcc-elf-newlib-x86_64-V2.2.5-20220323移动到 ‘/home/用户名/ ’的自行创建的子目录下。

② 在/home/用户名/ 目录下找到.cshrc 文件(需要打开隐藏文件显示,或者shell下ls -a命令),没有就新建一个, 功能和.bashrc类似,用于csh工具的全局环境变量设置。

③ 编辑.cshrc,添加两个环境变量:

setenv CODE_BASE_PATH /home/ICer/ic_prjs/opene906-main/E906_RTL_FACTORY

setenv TOOL_EXTENSION /home/ICer/Xuantie_tools/Xuantie-900-gcc-elf-newlib-x86_64-V2.2.5/bin

注意,上述后面的具体路径取决于实际两个文件解压的路径。

④ 查看csh的环境变量是否设置成功

linux桌面下打开终端shell, 输入csh ,回车,打开csh工具, 用echo $XXXX 命令查看XXXX环境变量,没有设置则返回空。

[ICer@IC_EDA /home/ICer]$csh

[ICer@IC_EDA ~]$ echo $CODE_BASE_PATH/

/home/ICer/ic_prjs/opene906-main/E906_RTL_FACTORY/

[ICer@IC_EDA ~]$ echo $TOOL_EXTENSION/

/home/ICer/Xuantie_tools/Xuantie-900-gcc-elf-newlib-x86_64-V2.2.5/bin/

[ICer@IC_EDA ~]$

至此,基本环境搭建完成。

补充:

后面做c906仿真时发现说漏了一步,还需要给 /smart_run/tests 目录给权限,smart_run下打开终端,命令 sudo chmod -R 777 ./tests 。

3.3 编译运行hello_world

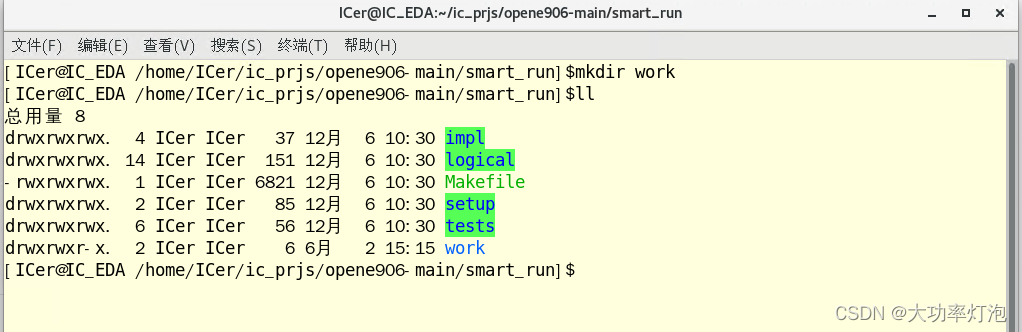

1 . shell进入 /xxxx/opene906-main/smart_run/ 目录下,新建一个work目录,并运行csh。

2 . make help 查看命令的介绍与使用

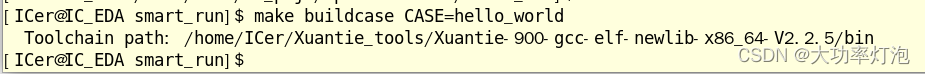

3 . 编译程序 make buildcase CASE=hello_world ,如果路径报错一定记得先运行csh,或者检查环境变量设置。

编译的一个主要目的是生成case.pat的文件,这个文件可以理解为机器码文件,会被RTL代码读入ram中运行。

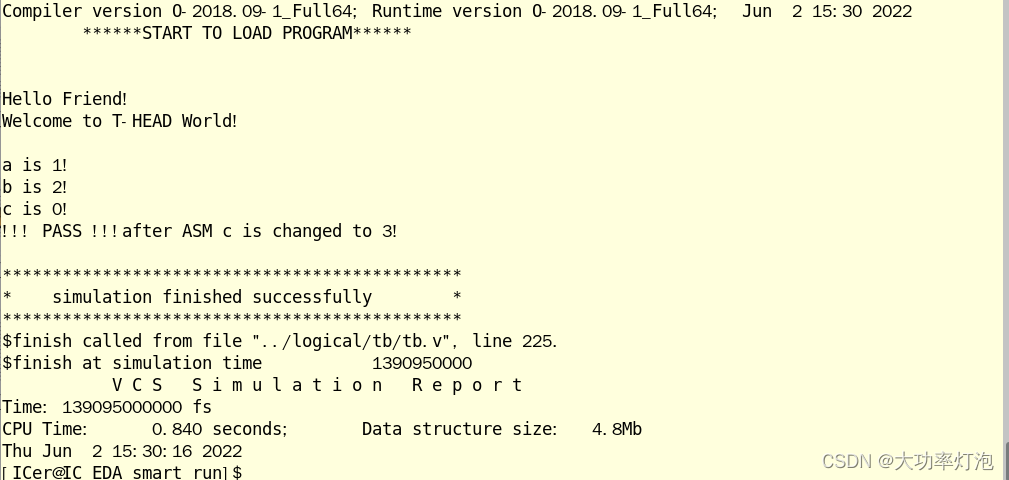

4 . 跑仿真例程 make runcase CASE=hello_world

这里根据make help下的提示也可以选择打开 SIM DUMP 关键字

仿真工具如果要用vcs, 可以使用make runcase CASE=hello_world SIM=vcs, 不加SIM=vcs 默认是iverilog。

其实根据makefile的描述,runcase命令也调用了buildcase,所以只需要这个就能有输出。但是在后面移植中可以看到会存在只需要buildcase而不需要runcase命令的场景,buildcase并不多余。

runcase 其实是掉用了vcs/iverilog ,对基于verilog的RTL的testbench进行仿真编译,熟悉vcs的朋友应该知道RTL代码经过vcs编译后,会生成一个simv的可执行文件,这个文件就在work路径下!

我们可以通过work路径下的命令 ./simv 来运行上面的仿真输出。

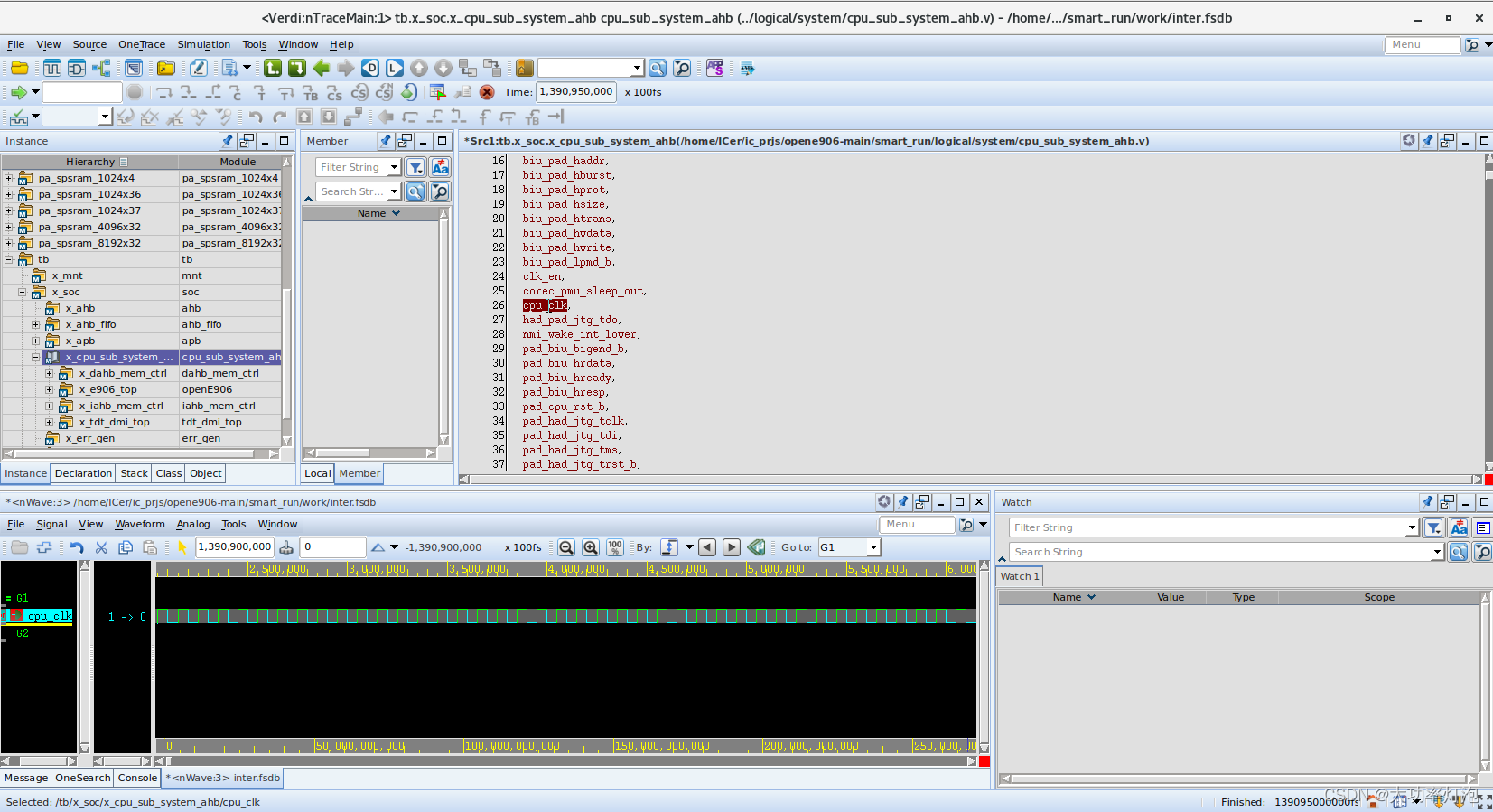

5 . 查看RTL仿真波形

运行

① make runcase CASE=hello_world SIM=vcs DUMP=on

使用vcs ,开启波形dump。

② cd work

③ ./simv -verdi 用verdi查看波形

4.总结

至此,E906基本的开发环境已经搭建起来了。

另外,官方提供的也就这么多了,并没有像蜂鸟E203这样提供FPGA移植的相关命令, 代码拷贝、约束文件编写、时钟IP添加、代码修改等都将在后面自行操作。

写得比较匆忙,难免有一些错误欢迎指正。最后,开源分享的意义在于获得别人的认可与互动。

1503

1503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?