RCC :reset clock control 复位和时钟控制器。

1、RCC主要作用—时钟部分

- 设置系统时钟SYSCLK

- 设置AHB分频因子(决定HCLK等于多少)

- 设置APB2分频因子(决定PCLK2等于多少)

- 设置APB1分频因子(决定PCLK1等于多少)

- 设置各个外设的分频因子

控制AHB、APB2和APB1这三条总线时钟的开启、控制每个外设的时钟的开启。

对于SYSCLK、HCLK、PCLK2、 PCLK1这四个时钟的配置一般是:HCLK = SYSCLK=PLLCLK = 168M,PCLK1=HCLK/2 = 84M,PCLK1=HCLK/4 = 42M。这个时钟配置也是库函数的标准配置。

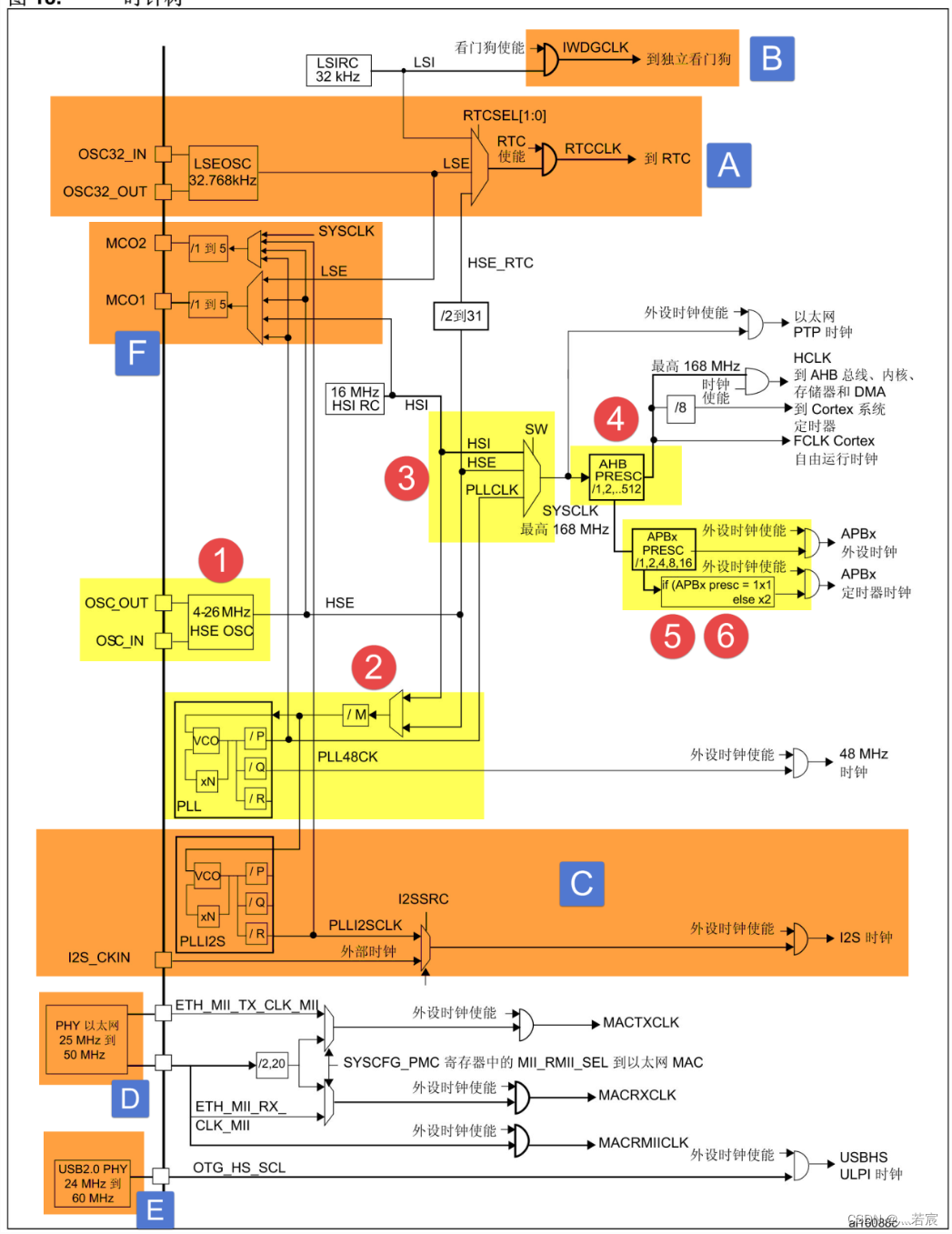

2、RCC框图剖析—时钟树

SetSysClock()该函数的功能是利用HSE把时钟设置为:HCLK = SYSCLK=PLLCLK = 168M,PCLK2=HCLK/2 = 84M,PCLK1=HCLK/4 = 42M。

2.1、HSE高速外部时钟信号

HSE是高速的外部时钟信号,可以由有源晶振或者无源晶振提供,频率从4-26MHZ不等。

当使用有源晶振时,时钟从OSC_IN引脚进入, OSC_OUT引脚悬空,当选用无源晶振时,时钟从OSC_IN和OSC_OUT进入,并且要配谐振电容。HSE在该开发板上的使用的是无源晶振25M。

使用HSE或者HSE经过PLL倍频之后的时钟作为系统时钟SYSCLK,当HSE故障时候,不仅HSE会被关闭,PLL也会被关闭, 此时高速的内部时钟时钟信号HSI会作为备用的系统时钟,直到HSE恢复正常,HSI=16M。

2.2、锁相环时钟PLL

PLL的主要作用是对时钟进行倍频,然后把时钟输出到各个功能部件。PLL有两个,一个是主PLL,另外一个是专用的PLLI2S,他们均由HSE或者HSI提供时钟输入信号。

主PLL有两路的时钟输出,第一个输出时钟PLLCLK用于系统时钟,F407里面最高是168M,第二个输出用于USB OTG FS的时钟(48M)、 RNG和SDIO时钟(<=48M)。专用的PLLI2S用于生成精确时钟,给I2S提供时钟。

HSE或者HSI经过PLL时钟输入分频因子M(2~63)分频后,成为VCO的时钟输入,VCO的时钟必须在1~2M之间, 我们选择HSE=25M作为PLL的时钟输入,M设置为25,那么VCO输入时钟就等于1M。

VCO输入时钟经过VCO倍频因子N倍频之后,成为VCO时钟输出,VCO时钟必须在192~432M之间。我们配置N为336,则VCO的输出时钟等于336M。 如果要把系统时钟超频,就得在VCO倍频系数N这里做手脚。PLLCLK_OUTMAX = VCOCLK_OUTMAX/P_MIN =432/2=216M,即F407最高可超频到216M。

VCO输出时钟之后有三个分频因子:

- PLLCLK分频因子p

- USB OTG FS/RNG/SDIO时钟分频因子Q

- 分频因子R(F446才有,F407没有)

p可以取值2、4、6、8,我们配置为2,则得到PLLCLK=168M。

Q可以取值4~15,但是USB OTGFS必须使用48M,Q=VCO输出时钟336/48=7。

PLL的配置有一个专门的RCC PLL配置寄存器RCC_PLLCFGR。

PLL的时钟配置经过,稍微整理下可由如下公式表达:

- VCOCLK_IN = PLLCLK_IN / M = HSE / 25 = 1M

- VCOCLK_OUT = VCOCLK_IN * N = 1M * 336 = 336M

- PLLCLK_OUT=VCOCLK_OUT/P=336/2=168M

- USBCLK = VCOCLK_OUT/Q=336/7=48

2.3、系统时钟SYSCLK

系统时钟来源可以是:HSI、PLLCLK、HSE,具体的由时钟配置寄存器RCC_CFGR的SW位配置。

设置系统时钟:SYSCLK = PLLCLK =168M。如果系统时钟是由HSE经过PLL倍频之后的PLLCLK得到, 当HSE出现故障的时候,系统时钟会切换为HSI=16M,直到HSE恢复正常为止。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1007

1007

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?