sync_fifo

sync_fifo.v

`timescale 1ns/1ps

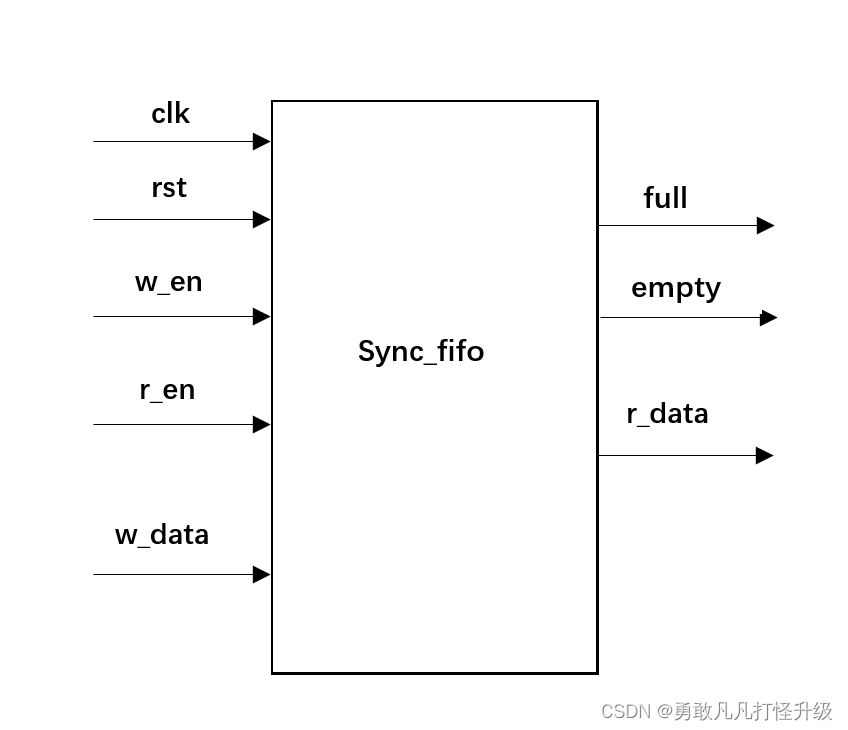

module sync_fifo(clk,rst,w_en,r_en,w_data,r_data,empty,full);

input clk,rst,w_en,r_en;

input [7:0]w_data;

output reg [7:0]r_data;

output empty,full;

reg [7:0]mem[15:0];//8*16RAM,depth is 16,addr is 4bits

wire [3:0]w_addr_a,r_addr_a;

reg [4:0]w_addr_e,r_addr_e;//扩展位去判断空满

assign w_addr_a = w_addr_e[3:0];

assign r_addr_a = r_addr_e[3:0];

//方便理解,可以简化

//read operation,非空且读使能有效则读

always@(posedge clk or negedge rst)begin

if(!rst)begin

r_addr_e <= 5'b0;

end

else begin

if(empty == 0 && r_en == 1)begin

r_data <= mem[r_addr_a]; //read data

r_addr_e <= r_addr_e + 1;

end

end

end

//write operation,非满且写使能有效则写

always@(posedge clk or negedge rst)begin

if(!rst)begin

w_addr_e <= 5'b0;

end

else begin

if(full == 0 && w_en == 1)begin

mem[w_addr_a] <= w_data; //write data

w_addr_e <= w_addr_e +1;

end

end

end

//empty and full signal

assign empty=(r_addr_e == w_addr_e)?1:0;

assign full =(r_addr_e[4] != w_addr_e[4] && r_addr_e[3:0] == w_addr_e[3:0])?1:0;

//full = r_addr_e == {w_addr_e[4],w_addr_e[3:0]};

endmodule

sync_fifo_tb.v

`timescale 1ns / 1ps

module testfifo;

reg rst,clk,r_en,w_en;

reg [7:0]data_in;

wire[7:0]data_out; //ouput define wire

wire full,empty;

sync_fifo ins(clk,rst,w_en,r_en,data_in,data_out,empty,full);

initial begin

rst=1;

clk=0;

#2 rst=0;

#5 rst=1;

end

always #20 clk=~clk;

initial begin

w_en=0;

#1 w_en=1;

end

initial begin

r_en=0;

#650 r_en=1;

w_en=0;

end

initial begin

data_in=8'h0;

#40 data_in=8'h1;

#40 data_in=8'h2;

#40 data_in=8'h3;

#40 data_in=8'h4;

#40 data_in=8'h5;

#40 data_in=8'h6;

#40 data_in=8'h7;

#40 data_in=8'h8;

#40 data_in=8'h9;

#40 data_in=8'ha;

#40 data_in=8'hb;

#40 data_in=8'hc;

#40 data_in=8'hd;

#40 data_in=8'he;

#40 data_in=8'hf;

#1000 $finish;

end

initial begin

$fsdbDumpfile("tb.fsdb");//这个是产生名为tb.fsdb的文件

$fsdbDumpvars;

end

endmodule

仿真Makefile脚本:

#-------------------------------------------------------------------------------------------------------

vcs :

vcs \

-f filelist.f \

-timescale=1ns/1ps \

-full64 -R +vc +v2k -sverilog -debug_access+all\

| tee vcs.log

#-------------------------------------------------------------------------------------------------------

verdi :

verdi -f filelist.f -ssf tb.fsdb &

verdi图形:

792

792

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?