property:

- property: “流程”

assert:

并发断言 (concurrent assertion)

- 并发断言基于时钟周期,用于描述一个跨时钟周期的行为

- 并发断言使用关键字 property…endproperty描述事件,如下

// "流程"

property

......

endproperty

// assert关键字启动断言检查

AssertName:assert property(PropertyName); // assert:检查是否符合该流程

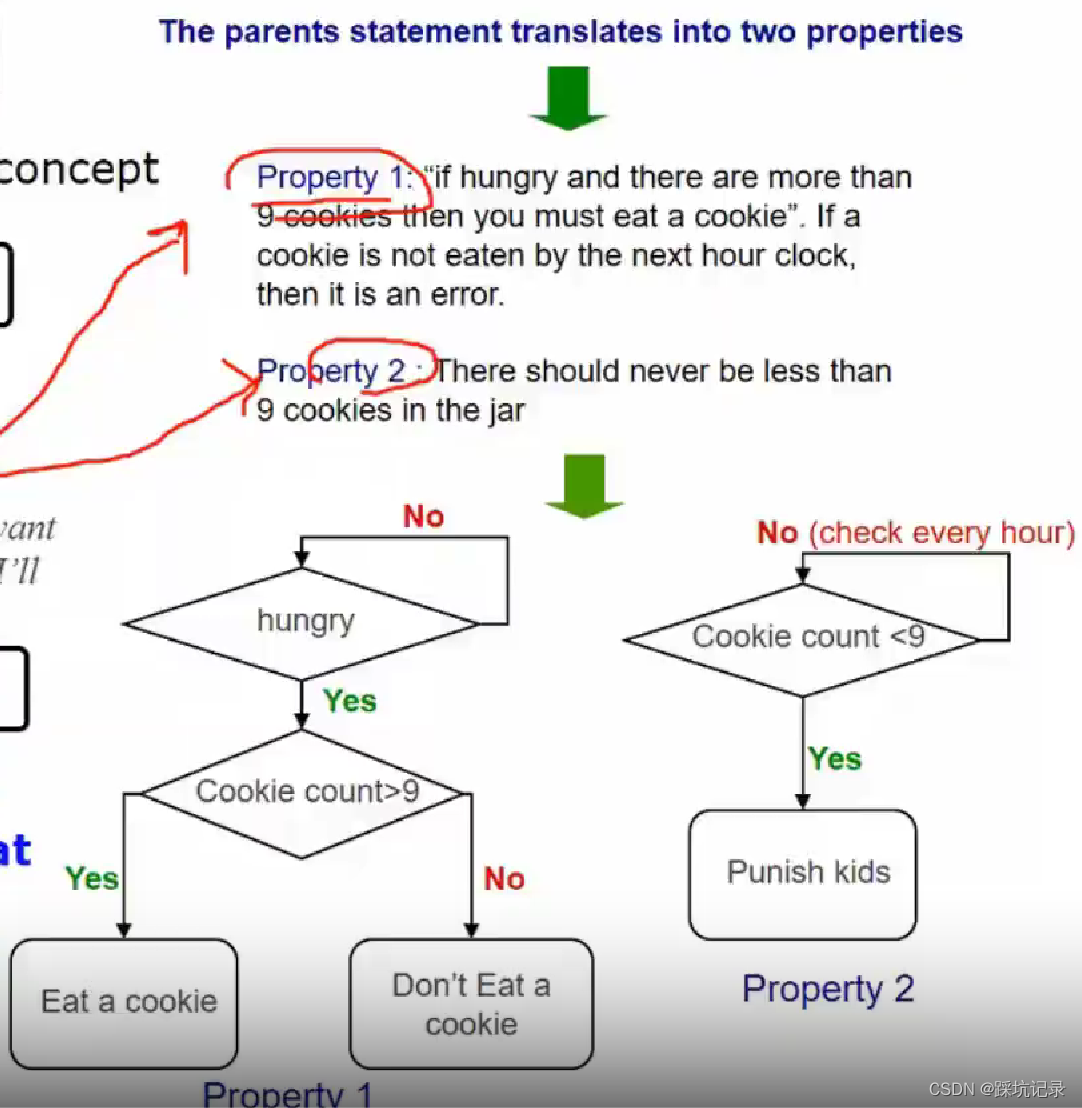

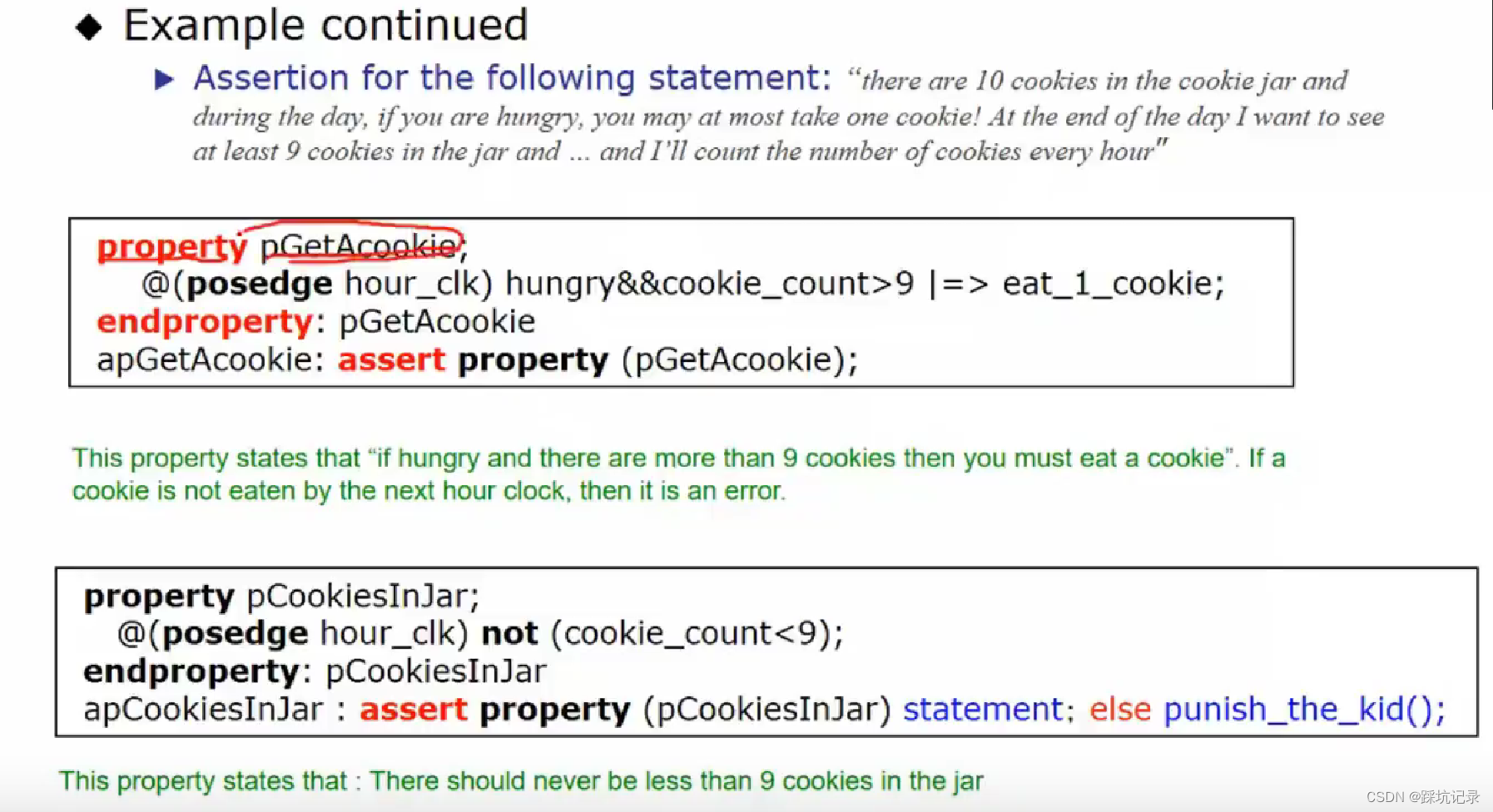

property pCookiesInJar:

@(posedge hour_clk) not (cookie_count<9); // cookie_count<9 则流程错误

endproperty:pCookiesInJar

// assert:检查是否符合该流程

apCookiesInJar:assert property(pCookiesInJar) statement: else punish_the_kid(); // 符合打印预设statement,不符合执行punish_the_kid()

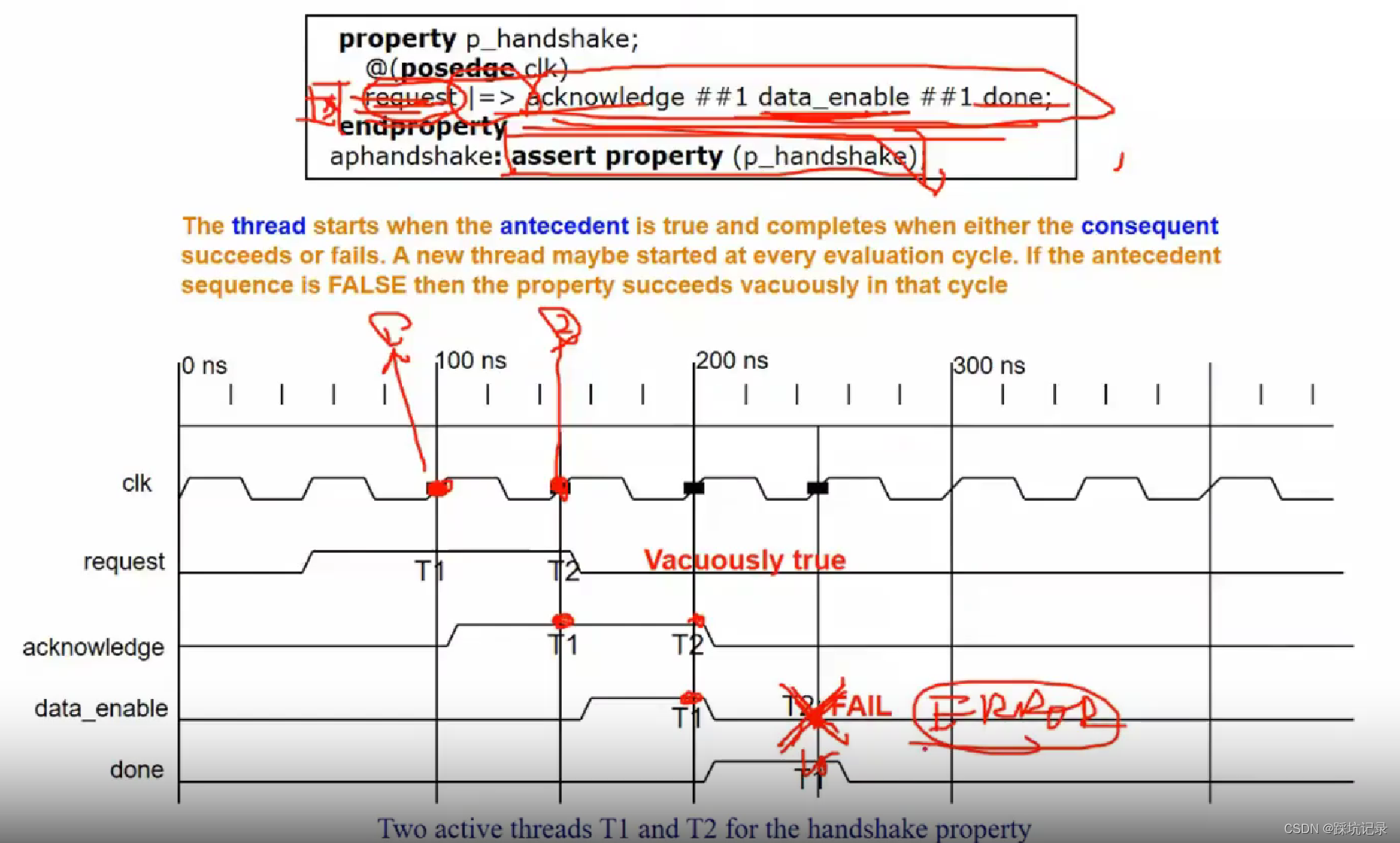

clk 时钟上升沿到来之后,request = 1,启动线程序列检查:在下个时钟周期,先拉高 acknowlege,再等待一个时钟周期,拉高 data_enable, 再等待一个时钟周期,拉高 done

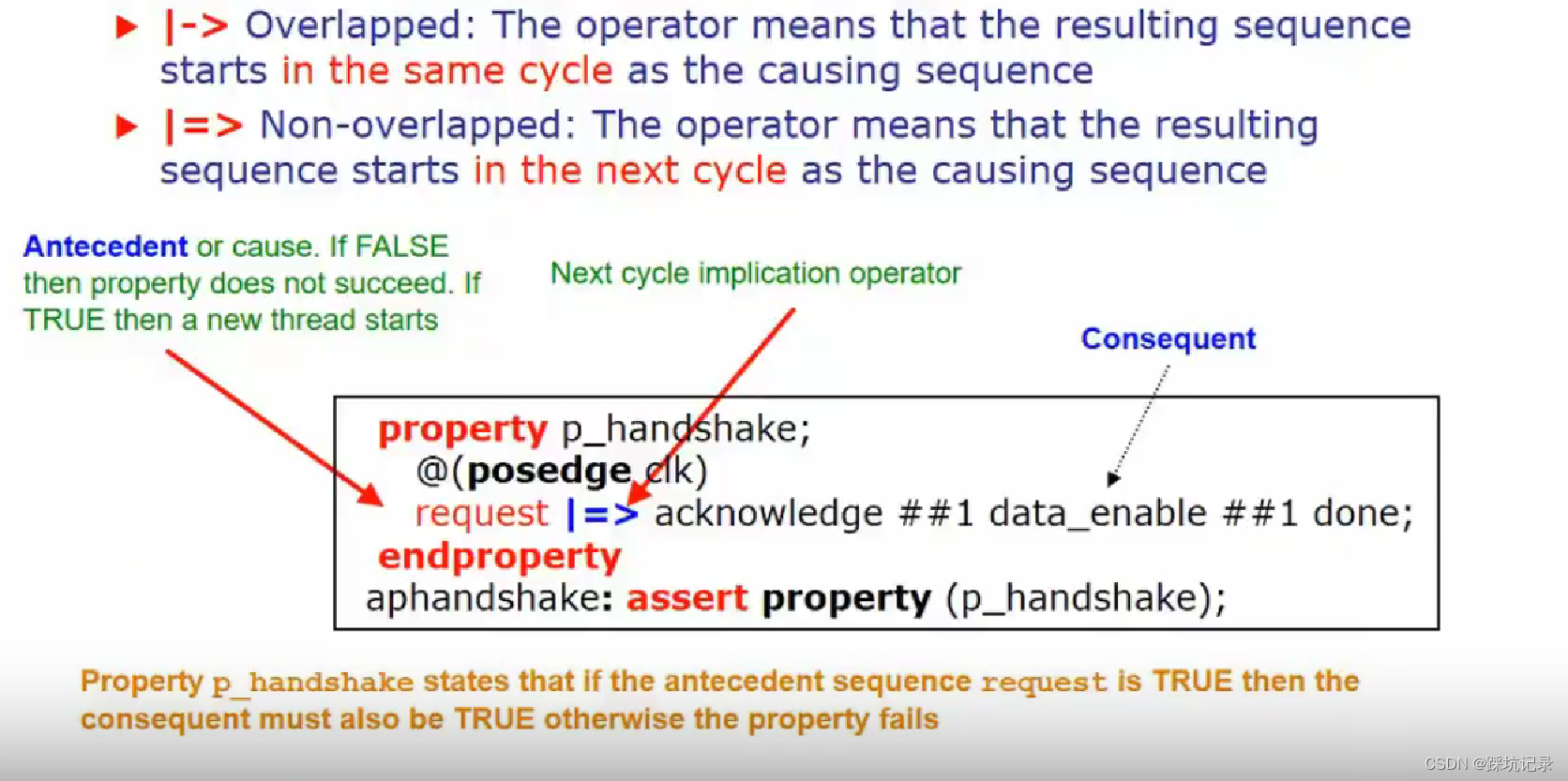

- 蕴涵操作符 (类似if语句)

连接原因序列与结果序列

// 蕴涵操作符 符号“|=>” “|->”左侧的为原因序列,右侧为结果序列

|=> // 结果序列处于起因序列的下一个时钟周期;等效于##1

|-> // 起因序列与结果序列处于同一个时钟周期

// |-> 起因序列与结果序列处于同一个时钟周期

@(posedge clk0) s0 |-> @(posedge clk1) s1 // 语法序列不合法,存在不同的时钟

@(posedge clk0) s0 |-> @(posedge clk0) s1 // 正确

// |=> 结果序列处于起因序列的下一个时钟周期;等效于##1

@(posedge clk0) sig0 |=> @(posedge clk1) sig1 //操作符"|=>"用于同步clk0与clk1的上升沿,等效于##1

每次时钟上升沿到来,只有 request = 1,assert 才会开始检测这个流程( |=> acknowlege ##1 data_enable ##1 done ),request = 0,assert 不检测。所谓 “vacuously true”

每次时钟上升沿到来,只有 request = 1,assert 才会开始检测这个流程( |=> acknowlege ##1 data_enable ##1 done ),request = 0,assert 不检测。所谓 “vacuously true”

- 将序列 (结果序列)封装

// 封装单个序列 a ##1 b ##1 c 为 s1

sequence s1; // sequence主要描述信号与信号之间的时序关系

a ##1 b ##1 c; // a为高,下一拍b为高,在下一拍c为高

endsequence

// 多个序列封装进property

property p1; // property主要将各种sequence进行封装

s1;

endproperty

// 关键字assert启动断言

a1:assert property(@(posedge clk) a |-> p1 ); // 在每个时钟上升沿检查, |-> :表示起因序列和结果序列在同一个周期

cover property(a1) else `uvm_error("ASSERT","...."); // 断言覆盖率

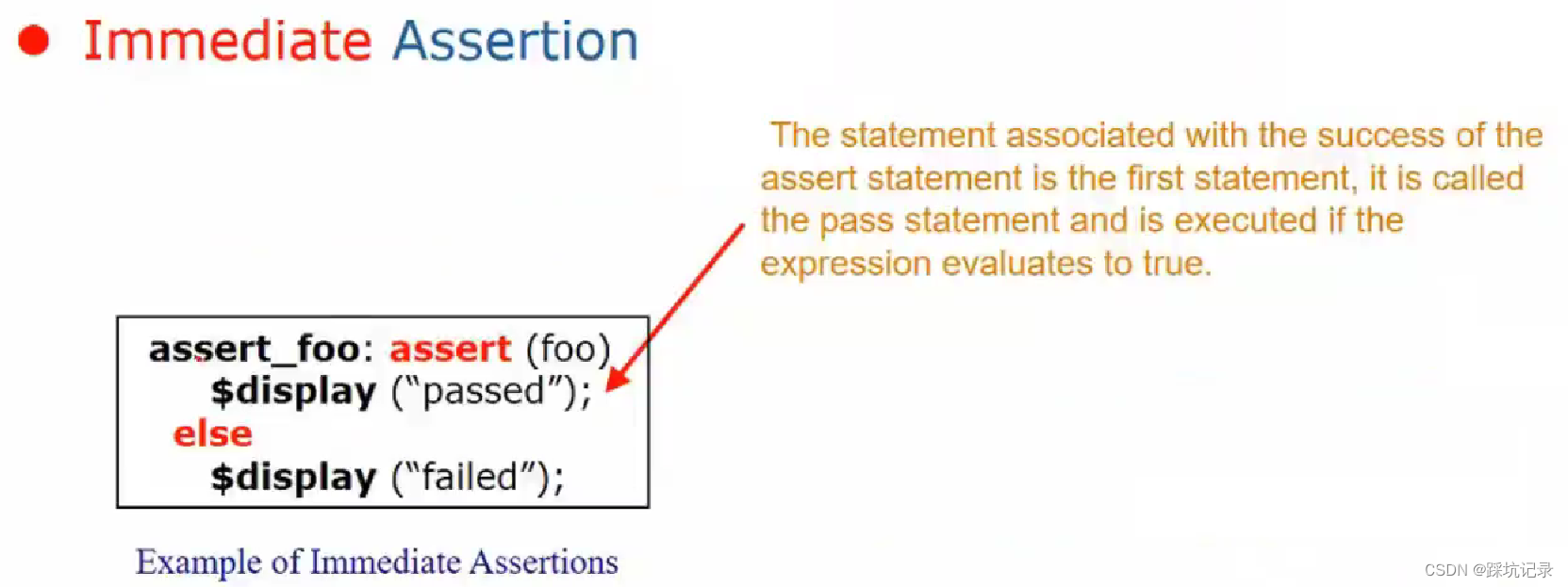

即时断言 (immediate assertion)

- 不跨越时间

检测 foo (expression表达式)

assert_name:assert(expression) // assert_info为该断言的名字

$display("passed"); //expression为真时,执行语句

else

$display("failed"); //expression为假时,执行语句

//如果状态为REQ,但是req1或者req2均不为1时,断言将失败

always @ (posedge clk) begin

if(state == REQ)

assert(req1||req2) //立即断言

else begin

t = $time;

#5$error("assert failed at time %0t", t);

end

end

always @ (state)

assert (state == $onehot) else $fatal;

disable iff 与 not

- disable iff (expression):当expression为真时,关闭property的序列检查,否则进行检查

- not: 表示not后的序列不能出现

property abc(a, b ,c); // 参数化

disable iff(a==1); // 当a为1时,关闭属性检查

not @clk (b ##1 c); // not后的序列不能出现

endproperty

//statement语句是可选的,当属性为真,执行pass_statement,否则执行fail_statement

env_property:assert property(abc(rst, in, out)) pass_statement; else fail_statement; // not后的序列不出现,则属性为真

3534

3534

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?