1、实验内容

上一节实验里面介绍的Memory存储器通道比较适合在PS端和PL端之间传递数组或者向量等数据,也就是多个相同类型的元素,如果要传递像ADC采集这样的连续数据流,Memory存储器通道就不是很合适了。

本节实验我们向大家讲解如何借助FIFO队列通道在PS(ARM)端Linux RT和PL端FPGA之间传递连续的ADC采集点或者AWG任意波形数据。比如最常见的应用之一就是设计一个DAQ数据采集卡或者AWG任意波形发生器。

我们可以将PS端Linux RT里面的任意波形或者记事本里面的不定长数据通过PS2PL下行FIFO通道传递给PL端FPGA,然后通过DAC生成模拟电压波形输出去。

又或者PL端FPGA将ADC采集到的连续数据流通过PL2PS上行FIFO通道发送给PS端Linux RT做处理,因为很多算法在FPGA里面做起来很麻烦,但是在PS端直接拖拽一下LabVIEW里面现成的算法VI就搞定了,比如多项式拟合、高斯拟合、不限点数的FFT变化、互相关、波形寻峰寻谷算法等。

为了方便用户使用,我们提前将8位、16位、32位的无符号和有符号类型的PS2PL下行和PL2PS上行FIFO通道封装到ZYNQ PS端和PL端,大家只需要有一点LabVIEW基础,简单拖拽和连线就能实现ZYNQ芯片内部ARM端跟FPGA端之间的FIFO交互了。

提醒:对于FXP定点数传输也很简单,那就是先把FXP定点数先通过“数值至布尔数组”函数去除符号特性,然后再利用“布尔数组至数值”函数转换成U8、U16、U32或者字节数组再发送出去。

2、实验目标

本节实验需要利用LabVIEW同时开发ZYNQ PS端Linux RT程序和PL端FPGA程序。 先编写一个PL端FPGA VI,将FPGA函数选板里面所有数据类型的FIFO通道VI函数拖拽到FPGA VI里面,再在前面板上创建一维输入和显示数组控件,借助LabVIEW FPGA在线前面板交互式运行功能,动态修改数组元素并观察PS端的数组元素是否一致。

然后编写一个PS端Linux RT程序,调用PS端FIFO函数选板里面的读写VI,读取PL端FPGA发送过来的各种类型的数组元素并显示在前面板上,同时将Linux RT程序里面的数据实时发送给PL端FPGA VI,从而实现双向通信和交互。

最后把写好的PL端FPGA程序框图编译成bit文件,再将Linux RT程序编译部署下载到ZYNQ芯片的PS端ARM里面去运行,利用LabVIEW Linux RT动态加载前面编译好的PL端FPGA bit文件,然后接上Xilinx JTAG下载器和千兆网线或者WiFi模块,就可以同时在线观察到PL端FPGA VI前面板和Linux RT前面板上的控件运行效果了。对于初学者着重复习并熟练掌握ZYNQ芯片PS(ARM)端LabVIEW Linux RT程序开发和PL端FPGA程序开发的过程和原理。

为了方便讲解,我们设计了4个FIFO通道读写交互实验程序,分别是:

- PS端Linux RT发送数据给PL端FPGA(PS2PL下行)

- PL端FPGA发送数据给PS端Linux RT(PL2PS上行)

- PS端发送数据给PL端同时读取回来(PS2PL回环)

- PS端与PL端FIFO通道吞吐率测试(PL2PS测速)

3、硬件介绍

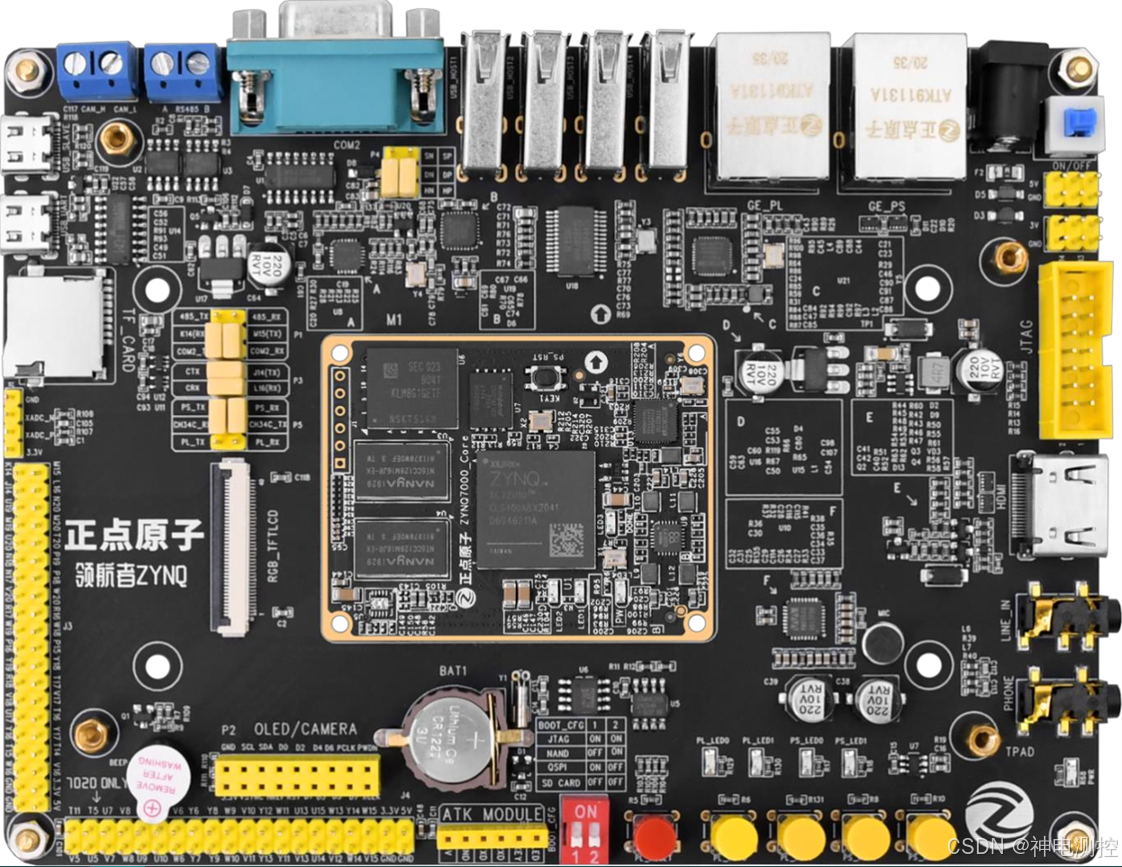

本节实验没有用到其他外设,只需要正点原子领航者ZYNQ开发板,Xilinx JTAG下载器和一根千兆网线即可。

其中,Xilinx JTAG下载器可以用来在线观察ZYNQ芯片PL端的FPGA VI前面板实际运行效果也可以动态修改前面板上的控件数值,减少因频繁编译而浪费的时间。

网线是用来将上位机编写好的ZYNQ PS(ARM)端Linux RT程序通过网络方式部署下载到ZYNQ PS端ARM里面去运行。提醒:这里的Xilinx JTAG下载器不需要下载PL端FPGA bit文件,因为PS端可以动态加载编译好的FPGA bit文件,所以如果大家不准备观察FPGA VI前面板上的控件状态,实际上这个Xilinx JTAG下载器也可以不用接。

图8-1显示的是正点原子领航者ZYNQ开发板实物图。

图8-1:正点原子领航者ZYNQ开发板上实物图

4、原理图介绍

由于本节实验没有用到ZYNQ开发板上的任何外设,只需要在ZYNQ芯片内部的PS端ARM和PL端FPGA之间进行内部通信和交互,所以,理论上只要ZYNQ芯片没坏,Linux RT系统能正常启动运行就可以了,故此,本节实验不需要原理图。

5、驱动VI函数讲解

5.1:PL端FPGA FIFO通道

对于ZYNQ PL端FPGA来说,要想把不定长度的数据发给PS端ARM或者从PS端读取传递过来的连续点,那么可以借助FIFO通道。为了方便客户调用FIFO通道,我们将PL侧的FIFO通道直接以Socket CLIP的方式封装到FPGA终端下面,如图8-2所示。按照传输方向分为PS2PL和PL2PS,其中,PS2PL指的是PS端Linux RT发送数据给PL端FPGA,那么FPGA VI直接读取这个通道即可,相当于下行;PL2PS则是PL端FPGA将数据通过FIFO发送到PS端ARM里面,相当于上行。

图8-2:ZYNQ FPGA终端下的FIFO端口信号(最原始的)

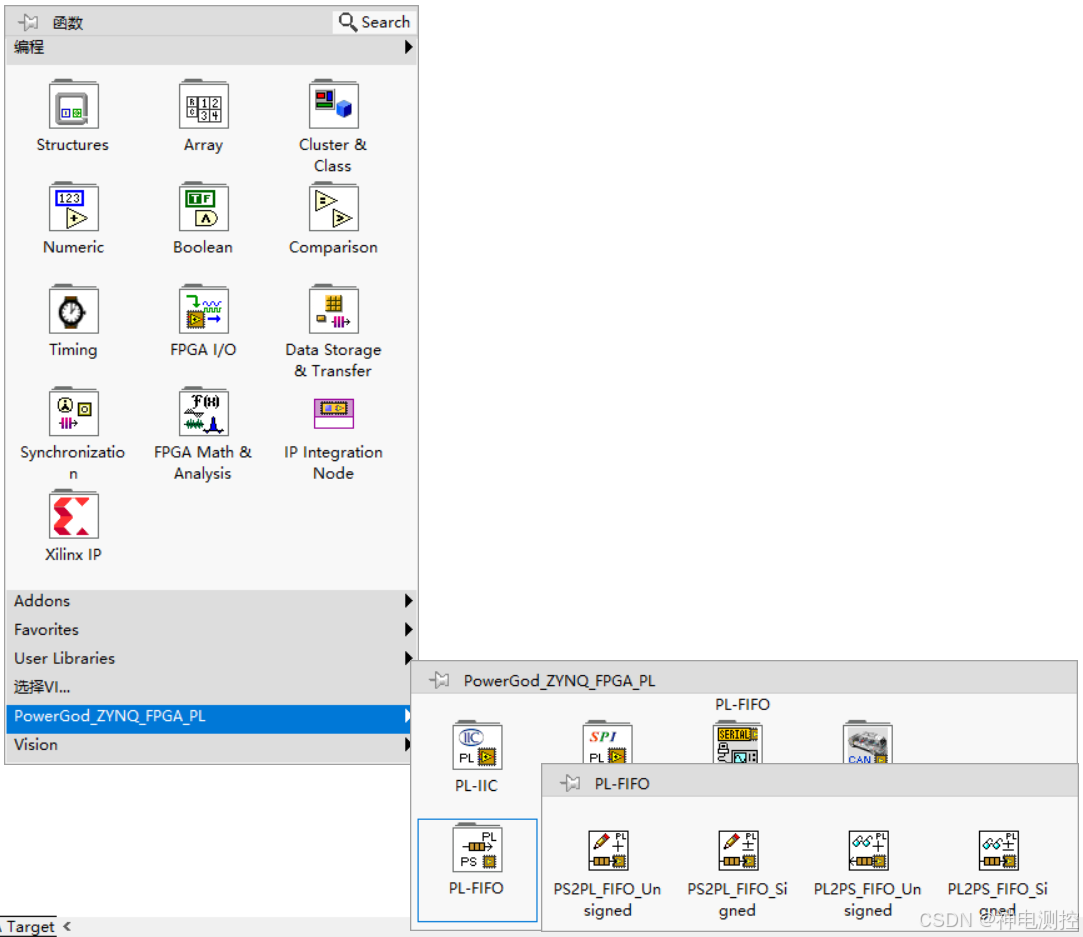

上面这些FIFO队列CLIP端口是最原始的,操作起来不直观,为了方便用户调用,我们将8位、16位和32位的FIFO读写操作直接封装成VI,放在了“PL-FIFO”函数选板里面了,如图8-3所示。其中,无符号和有符号单独分开,并且不同数据类型利用多态VI的方式组合在一起,这样用户只需要记住FIFO读写这两个VI函数就可以了,省时省力。

图8-3:ZYNQ PL端FPGA终端里面的FIFO通道读写VI函数

5.2:PS(ARM)端Linux RT驱动函数选板

正式开始采用LabVIEW编写ZYNQ PS端Linux RT 访问和更新PL端FPGA里面的FIFO通道数据之前,我们先来了解一下本节实验需要用到的PS端Linux RT环境下的FIFO驱动VI函数功能。

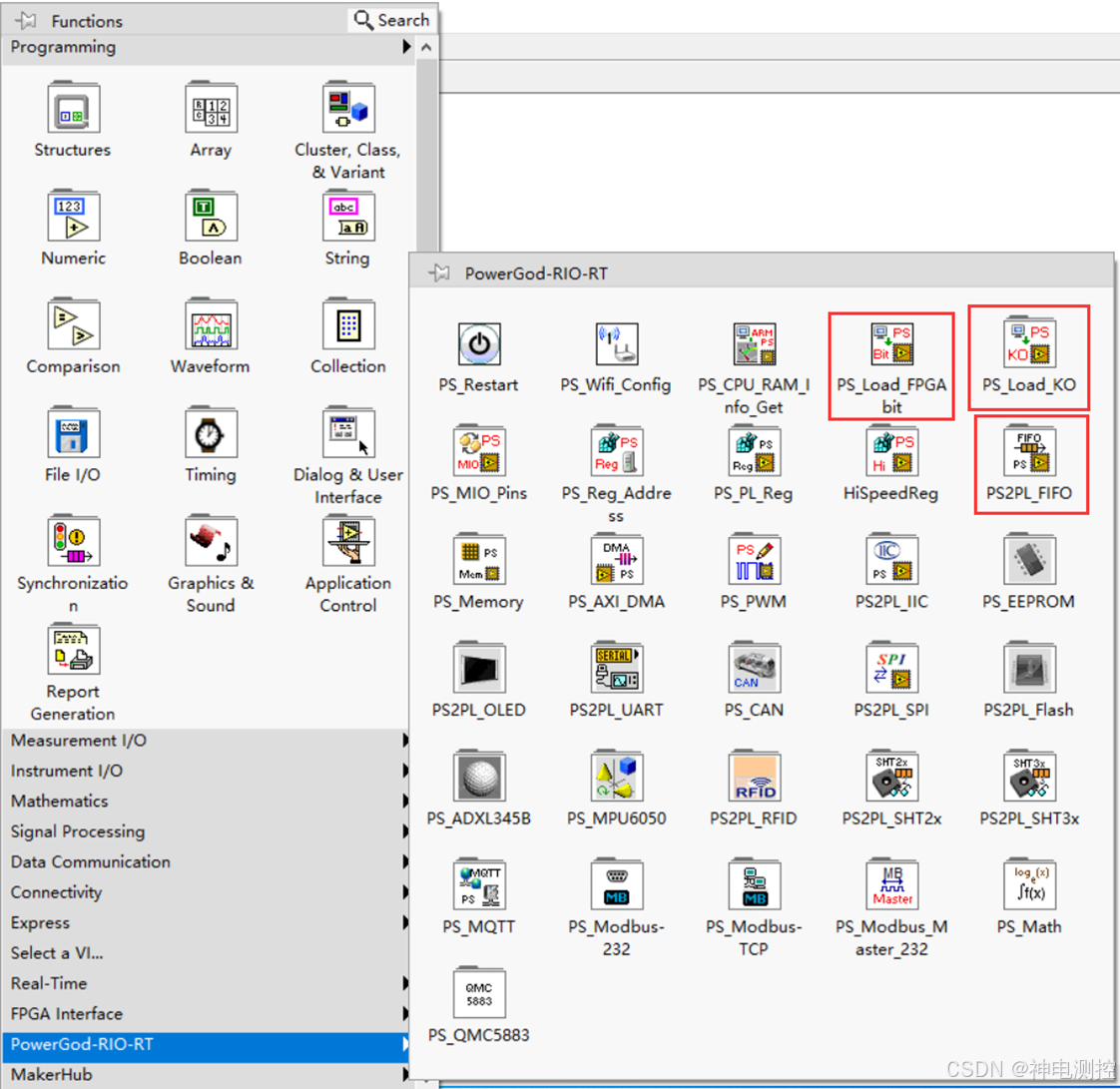

为了方便用户调用,我们提前将底层负责PS端与PL端沟通的FIFO通道函数封装到LabVIEW Linux RT环境下的“PowerGod-RIO-RT”选板里面,变成一个个小图标,一目了然。

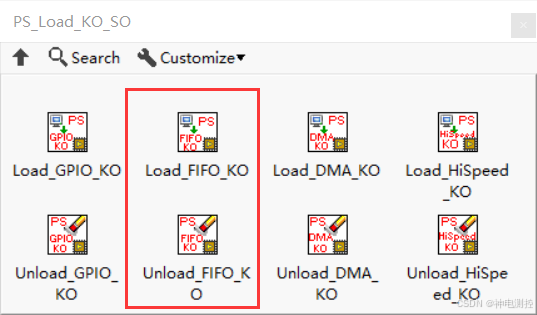

要完成本节实验,我们需要用到3个函数选板,分别是“PS_Load_FPGA_bit”、“PS_Load_KO”和“PS2PL_FIFO”,如图8-4所示。

图8-4:本节实验要用到的神电测控“PowerGod-RIO-RT”里面的3个函数选板

下面,我们分别介绍一下这3个选板里面的VI功能和应用场合。

1)由于本节实验展示ZYNQ PL端FPGA跟PS端相互通信,所以需要编写FPGA VI编译生成bit文件,然后由PS端Linux RT程序动态加载到ZYNQ芯片里面运行,所以Linux RT程序运行时的第一个VI就是“PS_Load_FPGA_bit.vi”这个函数。凡是需要调用ZYNQ芯片里面PL端FPGA参与的程序,都需要调用这个FPGA bit文件动态加载函数,切记!

2)为了提高ZYNQ芯片PS端的内存使用率,我们将很多外设KO驱动做成了动态加载和卸载。比如本节实验,我们需要读取PL端FPGA里面的FIFO数据或者将PS端发送过来的数据写入PL端FIFO,所以在Linux RT程序初始化之前,我们需要利用下面图8-5里面的FIFO动态加载“Load_FIFO_KO”函数(PSLoadFIFOKO(SubVI).vi)加载FIFO驱动,等到Linux RT程序停止退出之前,再调用“Unload_FIFO_KO”卸载函数(PSUnloadFIFOKO(SubVI).vi)卸载FIFO驱动以便释放FIFO类占用的内存和资源。

图8-5:FIFO类外设驱动动态加载和卸载函数

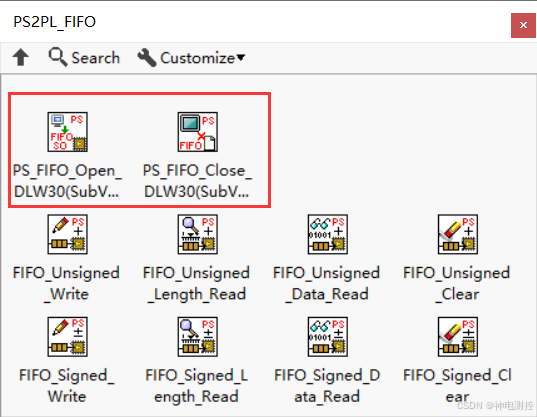

注意:只要是对PS端FIFO进行操作的场合,都需要调用上面“PS_FIFO”函数选板里面的第1个和第2个VI,也就是“PS_FIFO_Open”和“PS_FIFO_Close”,相当于对FIFO通道的初始化和程序退出前的FIFO关闭。

3)本节实验的重点就是要学会使用PS端和PL端之间的FIFO通道,因此,PS端少不了要对FIFO通道初始化打开,等到Linux RT程序退出的时候,再关闭FIFO通道,这两个VI函数就位于下图8-6所示的“PS2PL _FIFO”函数选板里面。

图8-6:ZYNQ芯片PS端FIFO打开和关闭函数

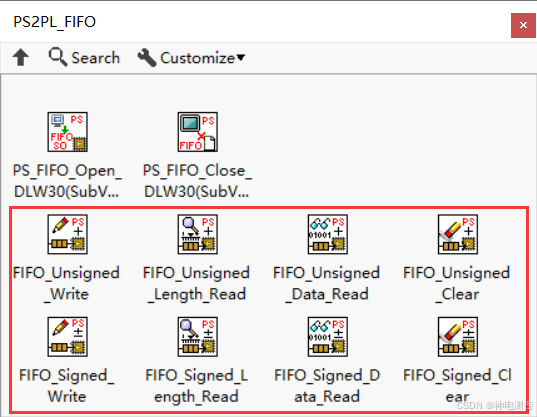

4)为了让ZYNQ PS(ARM)端Linux RT能够访问和操作PL端FPGA里面的FIFO,我们特地在PS端Linux RT下封装了4类函数(多态VI),位于“PS2PL_FIFO”函数选板里面,如图8-7所示。

图8-7:负责PS端与PL端二者之间通信的FIFO通道读写VI函数

这4类函数分别是:

1-第1列PS2PL FIFO写入函数:无符号和有符号8位、16位、32位数据类型的“FIFO_Unsigned_Write_Poly.vi”和“FIFO_Signed_Write_Poly.vi”,也就是Linux RT程序可以通过这个VI将PS端的数据写入PL端FPGA的FIFO里面去;并且每种数据类型的FIFO多态VI都有4个通道。所以一共有24个FIFO通道写入或者称之为发送子VI子函数。

2-第2列PS2PL FIFO缓冲区字节长度函数:无符号和有符号8位、16位、32位数据类型的“FIFO_Unsigned_Length_Read_Poly.vi”和“FIFO_Signed_ Length_Read_Poly.vi”,这两个VI很重要,类似大家所熟知的NI-VISA里面的“串口缓冲区Buffer字节数”这个属性。其实,不管是串口、USB总线、CAN总线、PCIe,本质上都是FIFO队列机制,因为上位机不可能实时读取下位机发送过来的数据,当上位机或者ZYNQ PS端忙于其他任务时,那么就需要一段FIFO队列缓冲区用来缓冲ZYNQ PL端FPGA发送过来的数据,当PS端需要读取缓冲区里面的数据时,需要提前知道这个FIFO通道里面有多少数据,这样可以平衡主机端的读取速度和读取块大小,以优化ZYNQ PS端ARM处理器性能。

3-第3列PS2PL FIFO读取函数:无符号和有符号8位、16位、32位数据类型的“FIFO_Unsigned_Data_Read_Poly.vi”和“FIFO_Signed_Data_Read_Poly.vi”,PS端可以通过这个多态VI读取PL端FPGA通过FIFO通道发送过来的数据。读取之前可以先调用上面第2列里面的Length_Read获取一下当前FIFO接收缓冲区里面的数据个数,然后再执行读取,这样可以有效减少不必要的读取浪费。

4-第4列PS2PL FIFO清除缓冲区函数:无符号和有符号8位、16位、32位数据类型的“FIFO_Unsigned_Clear_Poly.vi”和“FIFO_Signed_ Clear _Poly.vi”,这个类似NI-VISA里面的清除FIFO队列缓冲区VI,当采集中断后,需要重新开始采集PL端FPGA发送过来的数据,先把PS端Linux RT里面的FIFO缓冲区清空一下,这样接收到的数据就是最新的,并且解析的时候不会出错。

提醒1:为了降低用户记忆困难,我们将相同功能的VI组合在一起,封装成多态VI,这样用户只需要点击下拉列表就可以切换不同功能的VI,比如不同位宽的数据,本质上都是数据,所以合并在一起,方便使用。

提醒2:为了更好的区分ZYNQ芯片里面PS端和PL端的VI函数,我们特地在每个子VI图标里面加入了PS或者PL字样,如图8-8所示。如果这个子VI有PS字样,那么这个VI就可以被Linux RT主机端也就是PS端调用,反之如果是PL端字样,那就是被FPGA VI调用。比如,下图中上方就是PS端Linux RT程序可以调用的FIFO通道函数,下方则是PL端FPGA里面可以调用的FIFO操作函数。

图8-8:子VI图标上有PS和PL字样(用于区分该VI是运行在PS端Linux RT里面还是在PL端FPGA里面)

6、ZYNQ程序开发讲解(PL(FPGA)+PS(ARM))

6.1:ZYNQ PL端FPGA程序开发过程

6.1.1:新建或者打开已有的LabVIEW ZYNQ PL FPGA终端

1)前面第五章里面我们已经新建过了一个LabVIEW ZYNQ FPGA终端了,这里不再重复创建了,不记得的用户可以回顾一下前面第五章5.3.1节里面的相关内容。

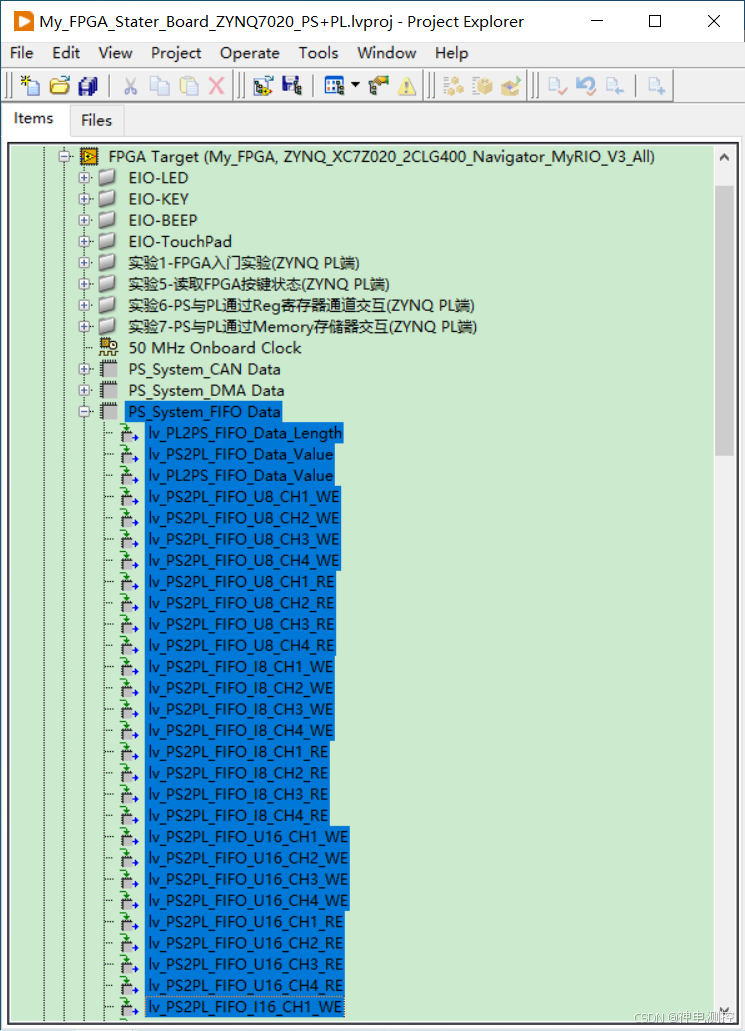

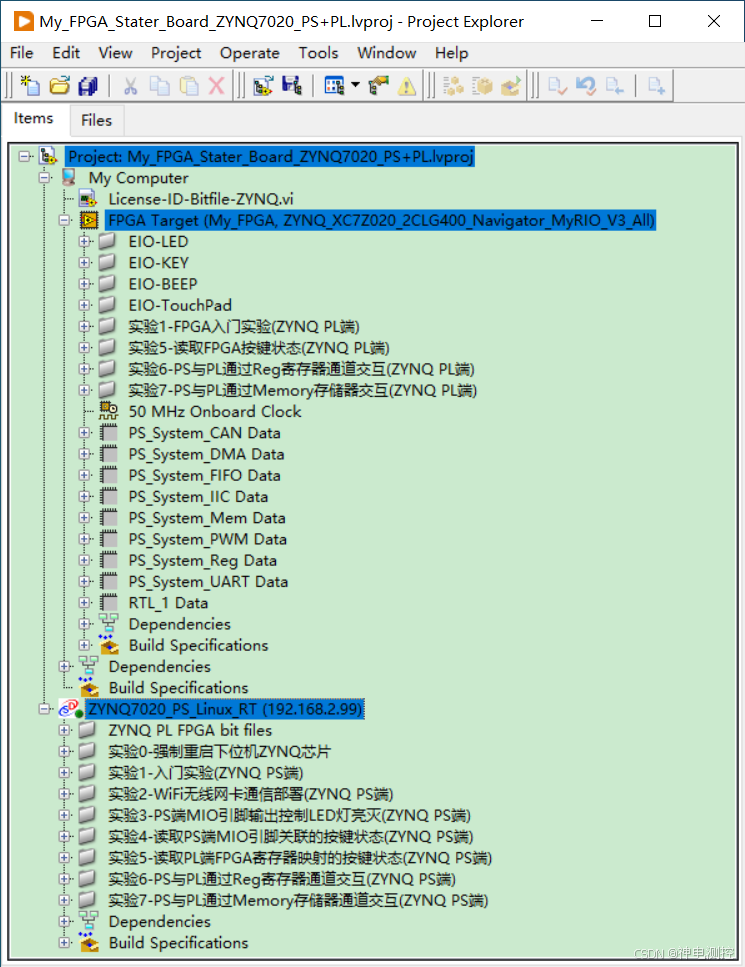

2)打开之前新建的项目浏览器“My_FPGA_Stater_Board_ZYNQ7020_PS+PL.lvproj”,如图8-9所示,可以看到该项目里面有两个终端分别是ZYNQ PL端FPGA部分和PS端Linux RT部分。

图8-9:打开前面新建好的LabVIEW项目浏览器(My_FPGA_Stater_Board_ZYNQ7020_PS+PL.lvproj)

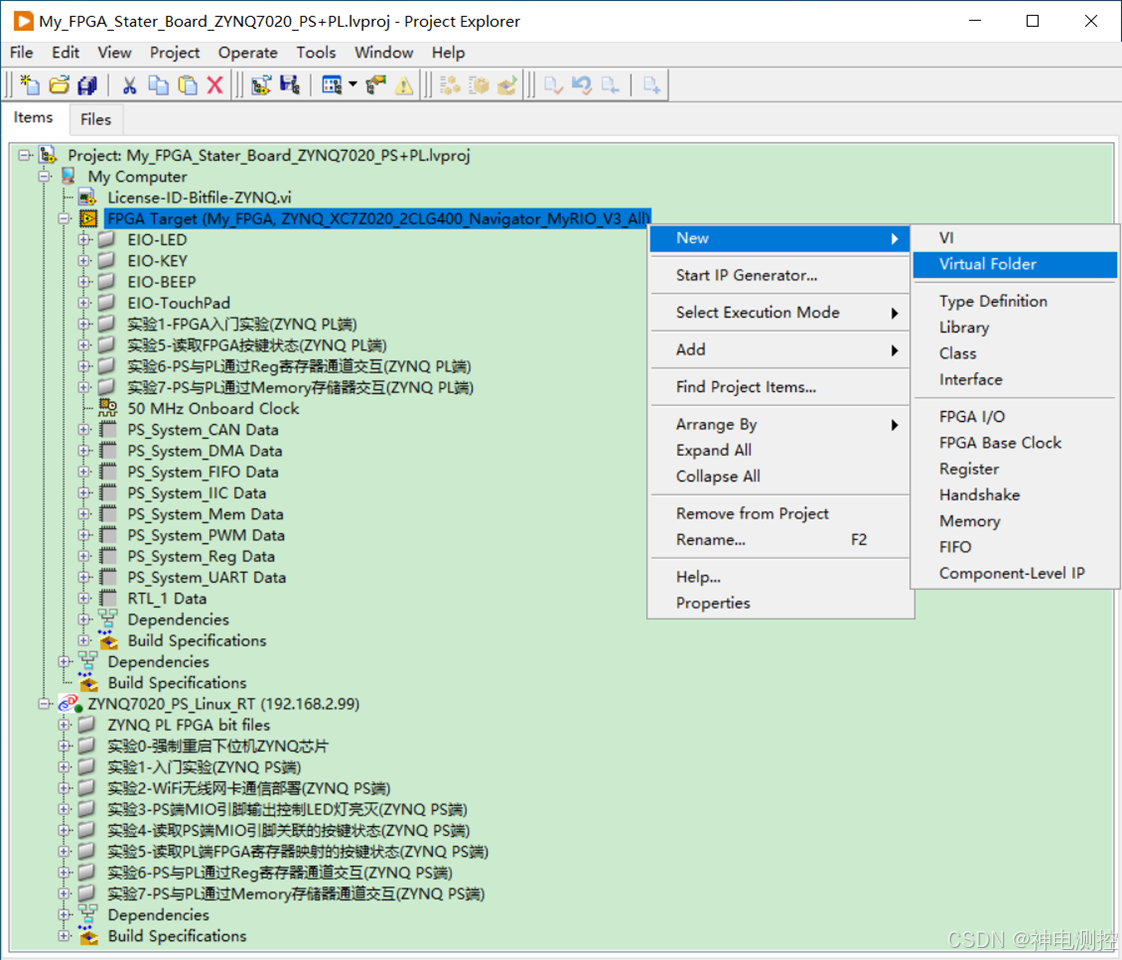

6.1.2:LabVIEW ZYNQ PL端FPGA应用程序编写(FPGA VI)

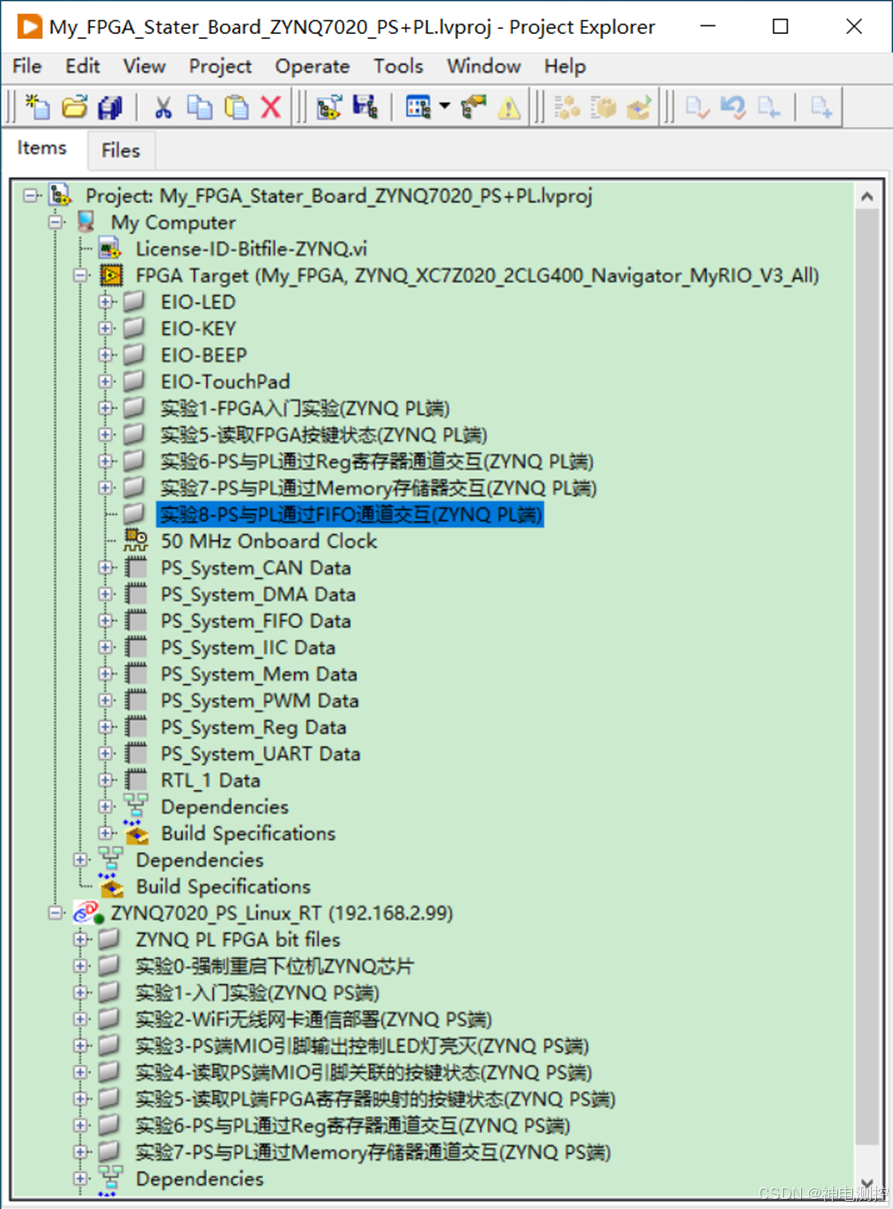

1右击“FPGA Target(My_FPGA, ZYNQ_XC7Z020_2CLG400_Navigator_MyRIO_V3_All)”,选择“New/新建>>Virtual Folder/虚拟文件夹”,创建一个虚拟文件夹,如图8-10所示;然后重命名为“实验8-PS与PL通过FIFO通道交互(ZYNQ PL端)”,如图8-11所示。

图8-10:右击FPGA终端新建一个虚拟文件夹

图8-11:虚拟文件夹重命名为“实验8-PS与PL通过FIFO通道交互(ZYNQ PL端)”

6.1.2.1:新建FPGA FIFO

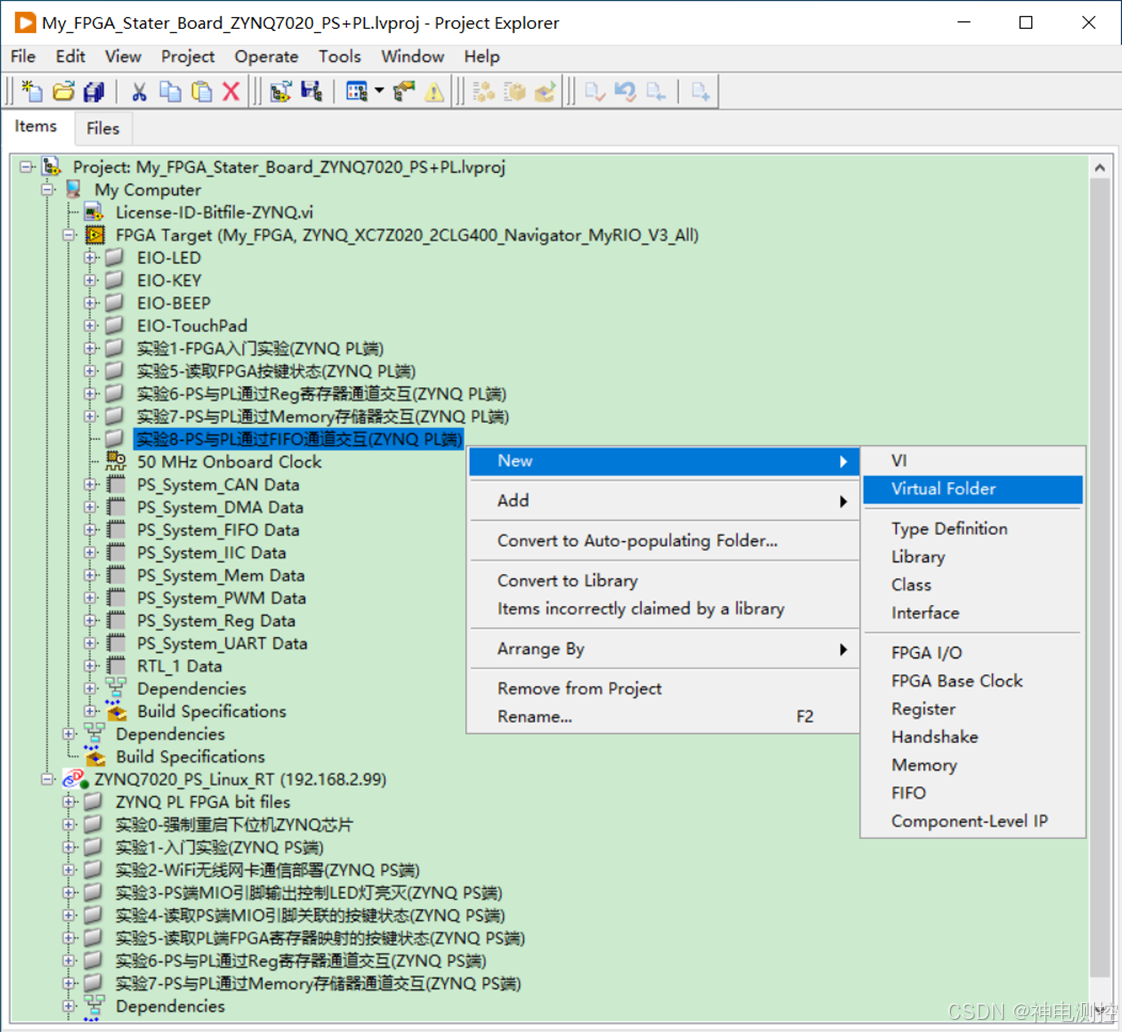

为了对FPGA终端下的不同对象进行分类管理,我们将FIFO通道单独存放到1个子虚拟文件夹里面,具体步骤如下:

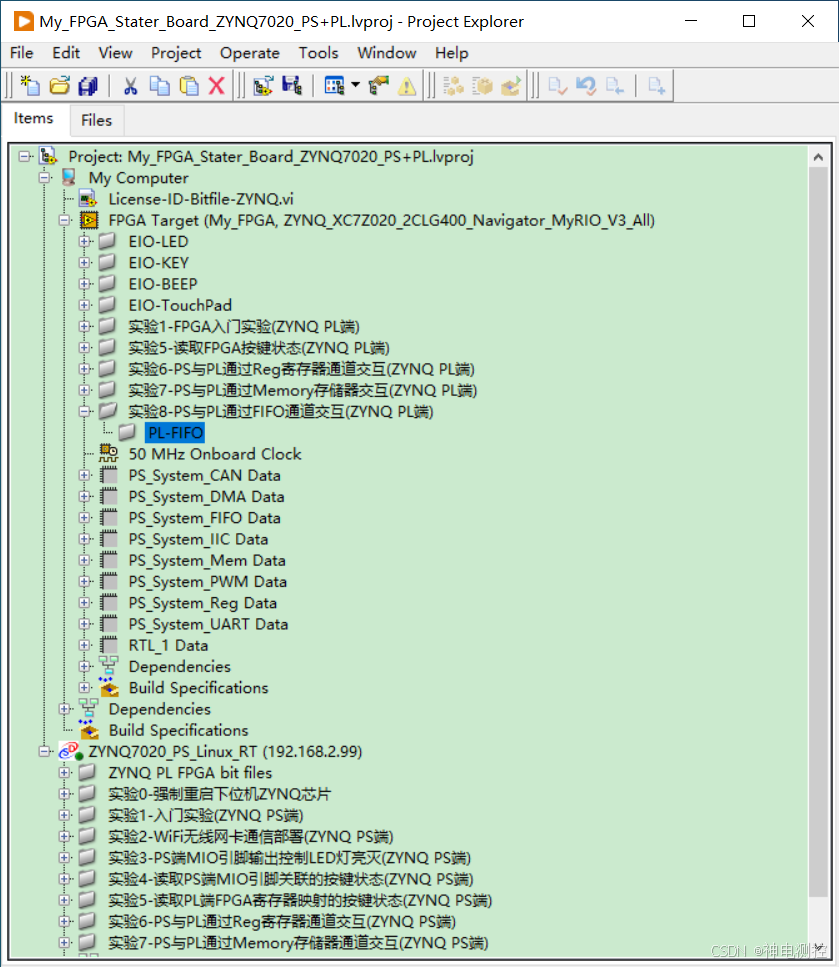

1)右击虚拟文件夹“实验8-PS与PL通过FIFO通道交互(ZYNQ PL端)”,选择“New/新建>>Virtual Folder/虚拟文件夹”,如图8-12所示,重命名为“PL-FIFO”,如图8-13所示,PL指的就是FPGA。

图8-12:右击ZYNQ PL端FPGA新建1个子虚拟文件夹

图8-13:将子虚拟文件夹重命名为“PL-FIFO”

然后,再以相同的方式创建两个虚拟文件夹分别用来管理PS2PL下行FIFO和PL2PS上行FI

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6630

6630

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?