前言

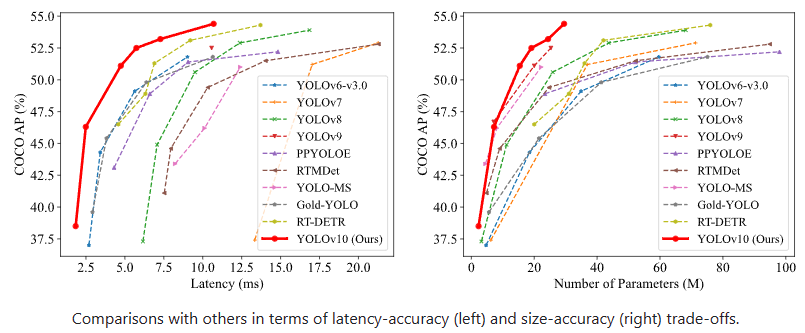

YOLOv10 是清华大学研究人员在 UltralyticsPython 清华大学的研究人员在 YOLOv10软件包的基础上,引入了一种新的实时目标检测方法,解决了YOLO 以前版本在后处理和模型架构方面的不足。通过消除非最大抑制(NMS)和优化各种模型组件,YOLOv10 在显著降低计算开销的同时实现了最先进的性能。并用大量实验证明,YOLOv10 在多个模型尺度上实现了卓越的精度-延迟权衡。

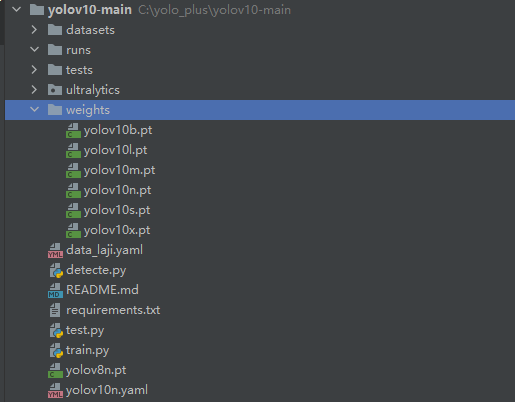

1.模型获取

官网连接:

https://github.com/THU-MIG/yolov10

也可以文末公众号内回复“YOLOv10”,获取全部代码、论文以及初始权重文件。

2.YOLOv10亮点

-

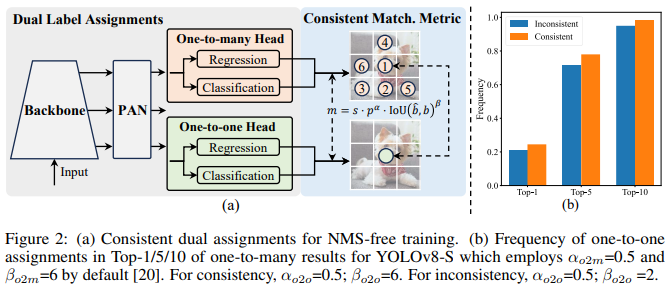

无 NMS 设计:利用一致的双重分配来消除对 NMS 的需求,从而减少推理延迟。

-

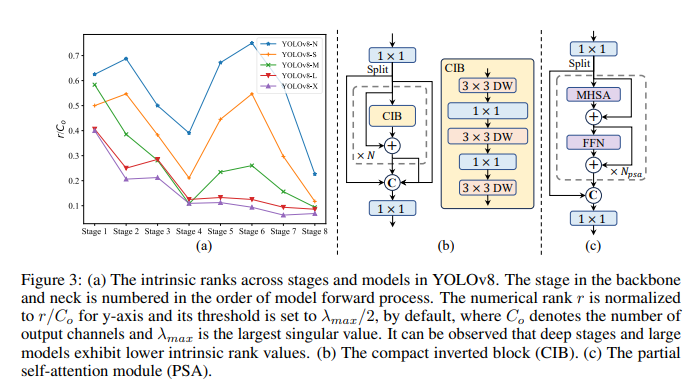

整体模型设计:从效率和准确性的角度全面优化各种组件,包括轻量级分类头、空间通道去耦向下采样和等级引导块设计。

-

增强的模型功能:纳入大核卷积和部分自注意模块,在不增加大量计算成本的情况下提高性能。

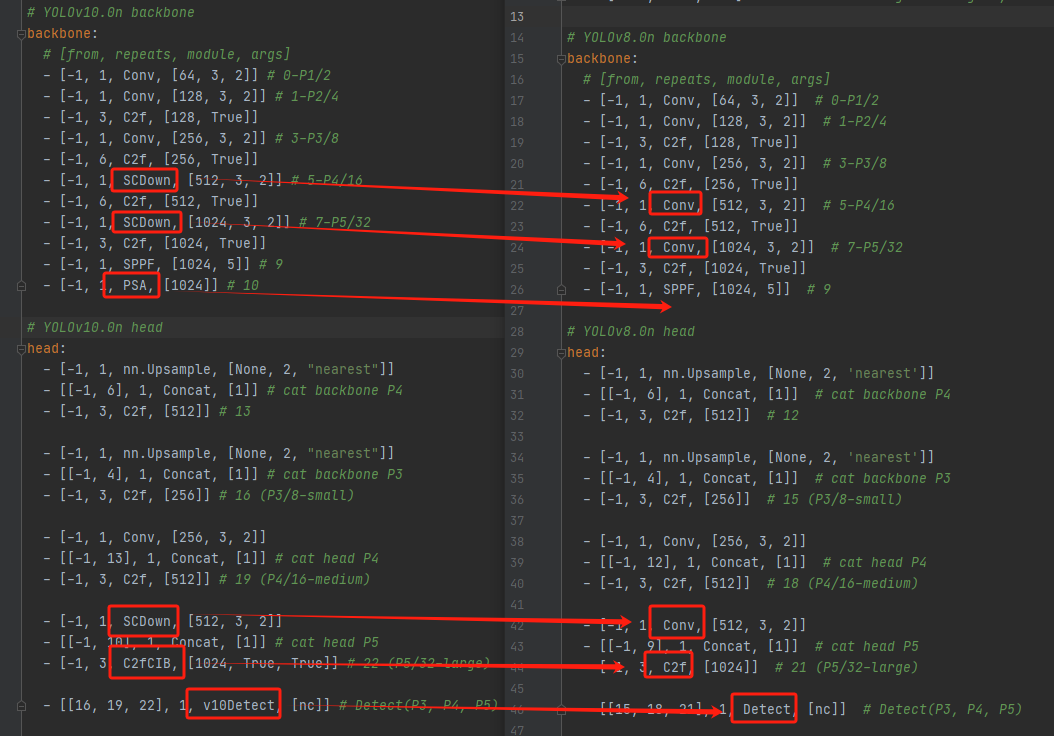

3.模型结构

YOLOv10与v8结构相比,从结构上看添加了PSA和在C2f结构中添加了CBI结构,去掉了NMS。

4.模型训练、验证、推理

需要导入YOLOv10模块,不是YOLO模块

from ultralytics import YOLOv10

# 加载模型

model = YOLOv10("yolov10n.yaml") # 从头开始构建新模型

model = YOLOv10("weights/yolov10n.pt") # 加载预训练模型(建议用于训练)

if __name__ == '__main__':

model.train(data="data_laji.yaml", imgsz=416, batch=32, epochs=10, workers=0) # 训练模型from ultralytics import YOLOv10

def main():

# 加载模型,test就是对测试集进行测试,删去就是对验证集进行测试

model = YOLOv10(r"runs/detect/train/weights/best.pt")

model.val(data="data_APSPC.yaml", split='test', imgsz=416, batch=16, workers=0) #模型验证

if __name__ == "__main__":

main()from ultralytics import YOLOv10

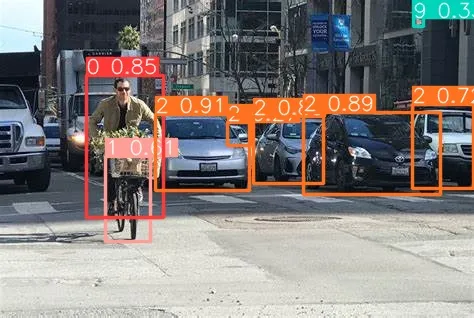

# 检测

model = YOLOv10(r"runs/detect/train/weights/best.pt")

results = model('datasets/images/val', save=True)

👇👇👇免费领取方式

在下方公众号内回复关键词:YOLOv10

最后:

如果你想要进一步了解更多的相关知识,可以关注下面公众号联系~会不定期发布相关设计内容包括但不限于如下内容:信号处理、通信仿真、算法设计、matlab appdesigner,gui设计、simulink仿真......希望能帮到你!

1487

1487

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?