DAC 的结构:

● Nyquist DAC:

- Binary-weighted DAC

- Unit-element (thermometer-coded) DAC

- Segmented DAC

- Resistor-string,current-steering,charge-redistribution DACs

● Oversampling DAC:(apply: Audio)

- Oversampling performed in digital domain (zero stuffing)

- Digital noise shaping (sd modulator)

- 1-bit DAC can be used

- Analog reconstruction/smoothing filter

DAC性能指标:

▶Static performance limited by matching (DNL INL)

● Systematic Errors

- Contact and wiring resistance (IR drop)

- Edge effects in unit element arrays (单元阵列的便捷效应)

- Process gradients(工艺梯度)

- Finite current source output resistance (有限的电流源内阻)

● Random Errors

- Lithography (光刻)

- Often Gaussian distribution (central limit theorem) (高斯分布)

Noting:对于DAC的INL&DNL仿真,比ADC快很多,输入code从 0~2^(N-1),每个code出现一次,然后看输出台阶装的波形,然后计算。

▶Dynamic performance limited by

● Finite settling time and slewing (有限的。。。)

- Finite RC time constant

- Signal dependent slewing

● Feedthrough

- Coupling from switch signals to DAC output

- Clock feedthrough

● Glitches due to timing errors

- Current sources won't switch simultaneously

二进制权重DAC

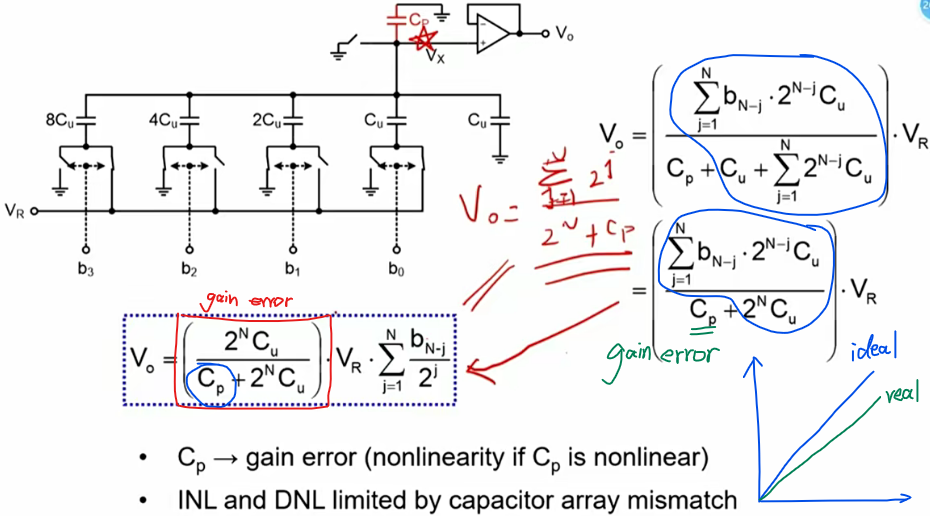

二进制权重就不在赘述了。看一下寄生电容Cp,相当于增大了冗余电容 redundant Cu ,使得总的电容加起来变大了,导致实际输出的 Vo 比理想的小,存在一个增益误差 gain error。

Gain Error Cancel:

①:调整 V_reference,前面存在增益gain,那么将 Vr / gian,就能将前面的gain error抵消掉。

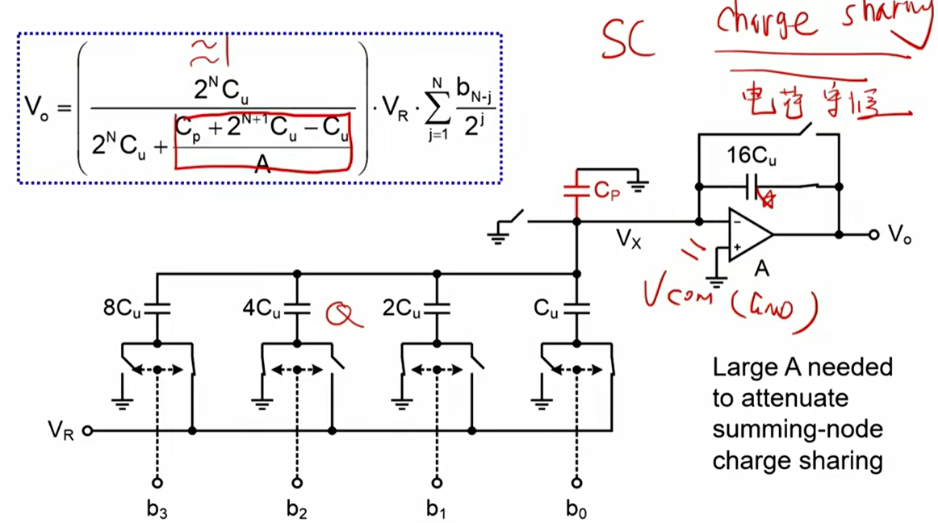

②:使Vx节点的电压不发生变化,那么Cp两端的电荷没有变化,自然影响不了。

方法:开关电容放大器

敏感的点(电荷守恒的点)是Vx,任何对 Vx 的电压能产生翻转的因素都可能引起误差。电容下级板的寄生,是接到强驱动信号 Vref&gnd 上的,影响不大。但是 bottom走线和top走线 可能会存在寄生,这个是敏感的(走线寄生会改变电容的绝对大小,相当于8*Cu+△C3,4Cu+△C2)

解决方法是:①减小走线间的寄生电容 --做好屏蔽,做dummy电容;②做好匹配,最起码让△C3=2*△C2,总的电容(算上寄生)要成比例 --三明治结构寄生匹配 。

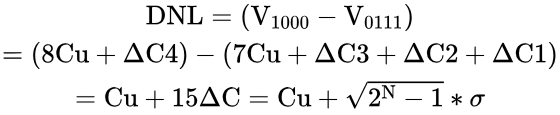

MSB 翻转造成的影响:

最差的INL&DNL,因为所有电容同时翻转,每个电容都贡献失配。(下式计算还需归一化到LSB)

![]()

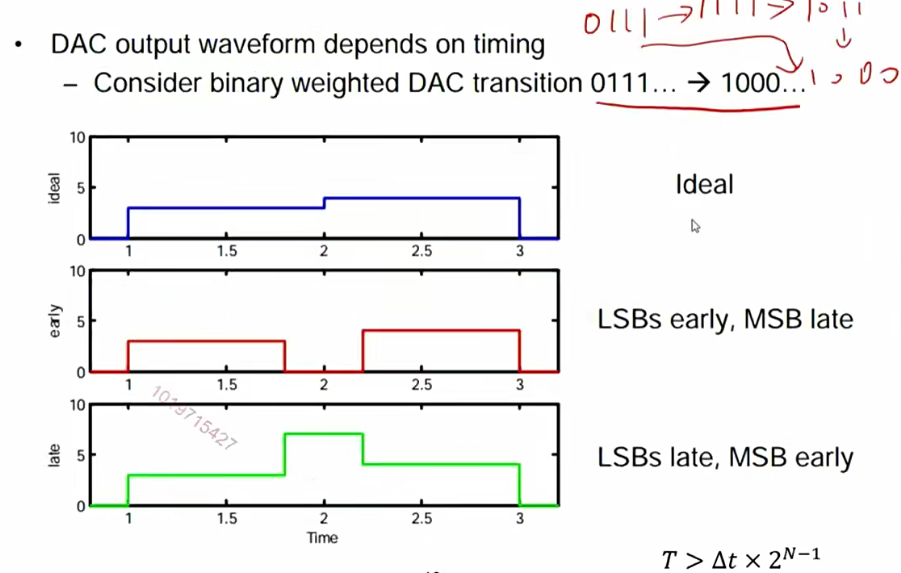

Output Glitches

实际DAC在输出时会有抖动,造成的原因:①时序上的误差;②带宽不够,时序响应不稳定;③开关动作的误差。解决方法:输出端加一个 de-glitching SHA (Sampling Hold Amplifier)

一般来说,只有单独做的DAC需要做SHA,ADC里面的DAC不需要,因为ADC里面会保证时序,规避掉glitches。(Pipline ADC 除外,因为要做余量放大 MDAC)

做SHA的作用:①消除输出抖动;②提供增益;③驱动下一级电路;④能进行I-V转换。

SHA不需要特别快快的带宽,SHA的 BW 只需要比采样时钟 fs 快就行,保证在下一次转换前,将DAC的输出建立好。

解释:glitch的来源之一:时序的误差——翻转的时候,相邻两次code并不是同时跳变,他们肯定有个中间态,code值是不确定的,这就带来了DAC的输出不确定,出现glitches。

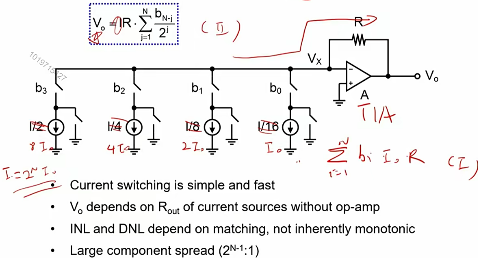

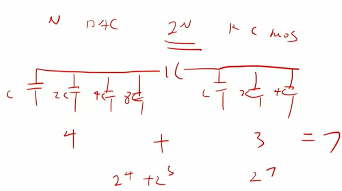

二进制权重电流型DAC——(Cap --> MOS管做电流镜)

电流切换简单,快速。存在一个折中关系:最终输出的电压是 Vo = I*R,当R较大,I 变小,功耗变小,但是电阻噪声变大;反之当R较小,噪声较小,但是I变大,功耗变大。然后类似CDAC一样,INL&DNL 取决于电流源的match,类似的如果满足不了 I3 >=(I2+I1+I0),会造成缺码现象(missing code),造成非单调(not inherently monotonic),二进制DAC的通病。

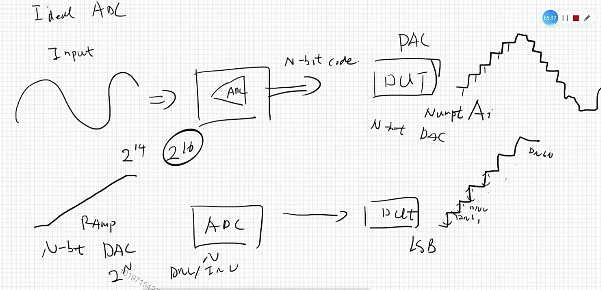

DAC的仿真方法:

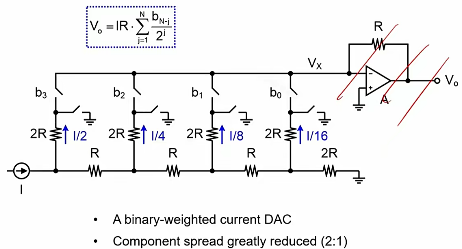

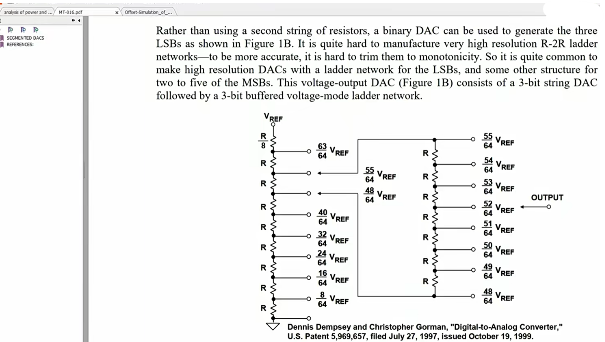

R-2R DAC:

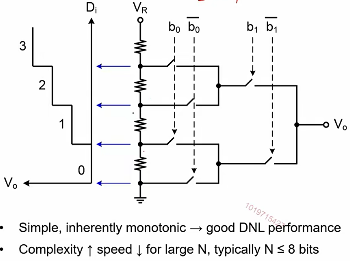

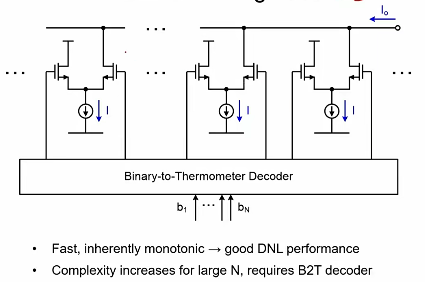

Unit-element (thermometer-coded) DAC(温度计编码的DAC)

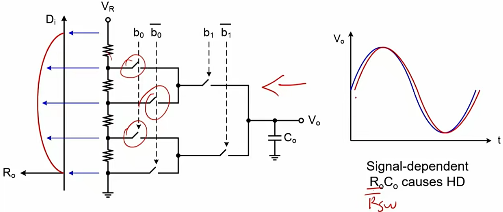

Unit-element Resistor-String DAC (电阻串联DAC,一样,R、C、MOS 都适用)

温度计码,天然单调(monotonic),不缺码,DNL性能好。位数高的话开关阵列复杂,速度慢。

存在 code-dependent Ro&Rswitch。不同的code,抽头出去的电阻是不一样的,对应开关的电阻也是不一样的,这样就导致输出电阻Ro随code变化,导致signal-dependent RoCo,带宽不一样。

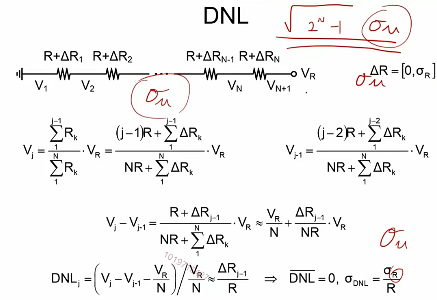

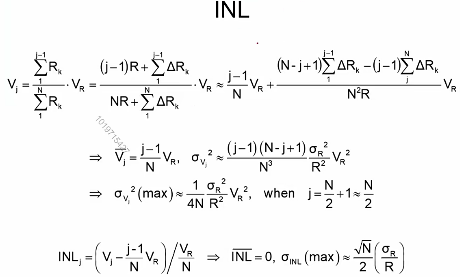

下面看看为什么说DNL好呢?

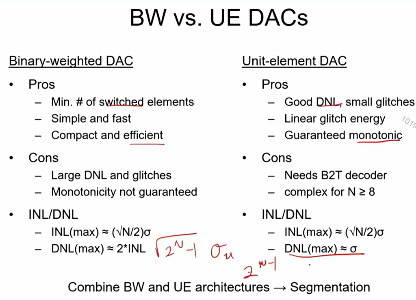

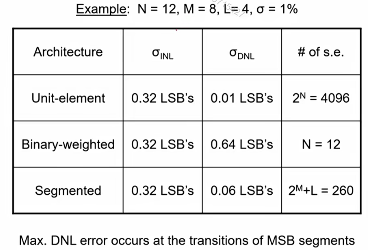

二进制码最坏DNL发生在中间,MSB跳转,所有电容都发生翻转,贡献 (2^N - 1)个mismatch源。DNL_wc = sart(2^N -1)*σ_u。

温度计码相邻两个code只有一位不同,也就是说只有一个R贡献了DNL,并且所有的DNL都是相同的,不存在最坏情况。DNL = σ_u。

注意:

所有结构的 INL 都是由匹配决定的,他们的INL都是一样的,INL_wc = sqrt(2^N -1)*σ_u。

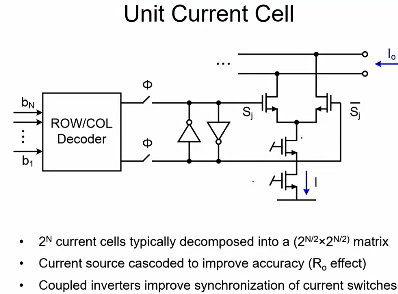

Unit-elementCurrent-String DAC

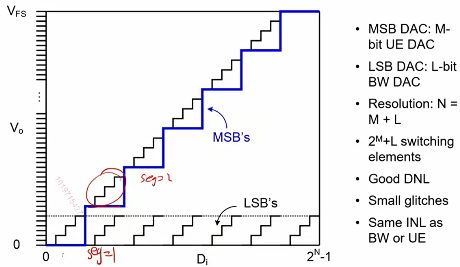

Segmented DAC(分段式DAC)

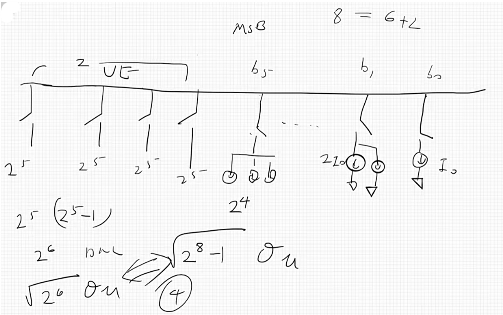

Segment 的好处:例如这个8位的DAC,拆分成6+2,前六位用二进制编码,后两位用温度计编码,温度计编码。MSB翻转时,相较二进制码,segment高两位用的温度计码,每次翻转只有2^5个单位电容,总的翻转电容时2^6个,DNL=sqrt(2^6)*σ_u ,相较纯二进制码 DNL = sqrt(2^8-1)*σ_u,大大减小。右下图,一般没有那么这样的,一般MSB=4位,LSB=8位。

还有一种分段式CDAC:上图是分段式电阻DAC,先粗量化MSB,然后通过开关切换,进行细量化LSB。

4938

4938

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?