前言

SPI是常用的通信手段之一,经常使用,但也经常踩坑;网上资料很多,但对于CS/NSS使用的讲解比较少,正好最近使用SPI也遇到了一些问题,记录一下。

SPI中NSS作用和用法

简单来说,NSS和CS是一个东西,主要用于片选从机的。SPI控制器上连接的内部NSS引脚。

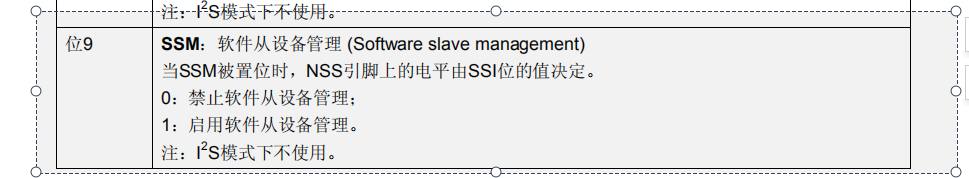

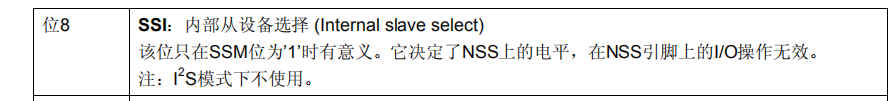

NSS硬件模式和软件模式:可以通过寄存器配置,选择将内部NSS引脚连接到SSI寄存器,使用寄存器控制NSS电平,也可以选择内部NSS引脚和外部真正的NSS GPIO相连,由外部引脚电平来控制NSS。

我画了一个关系图,可以清晰的看明白NSS的控制流程:

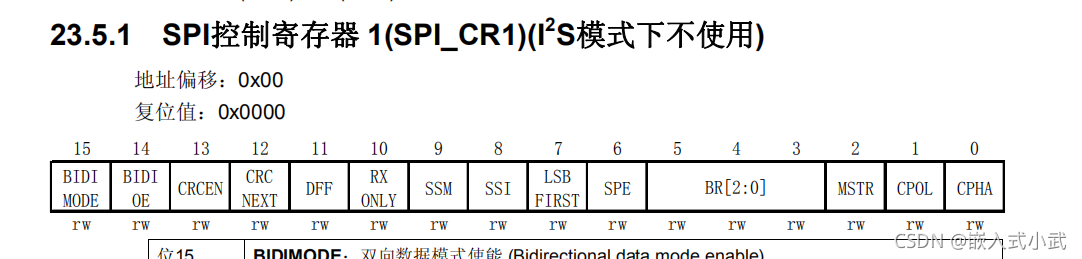

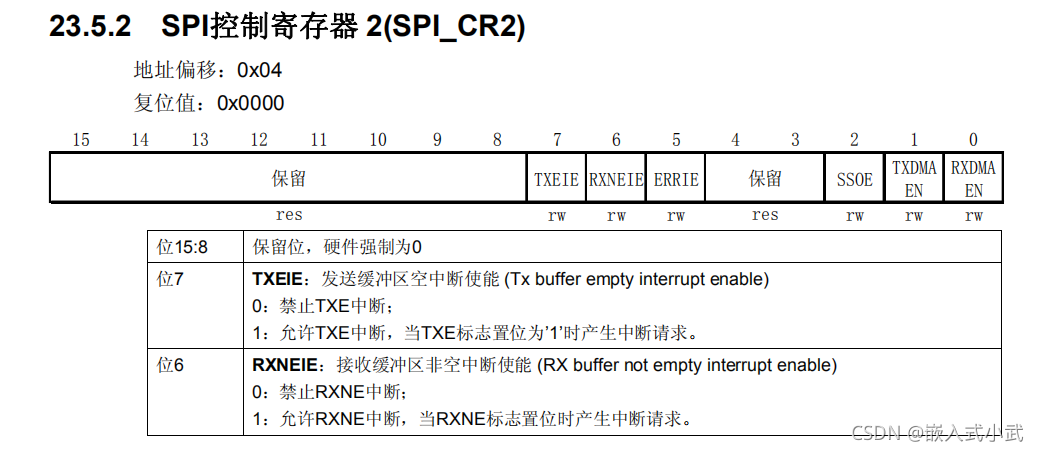

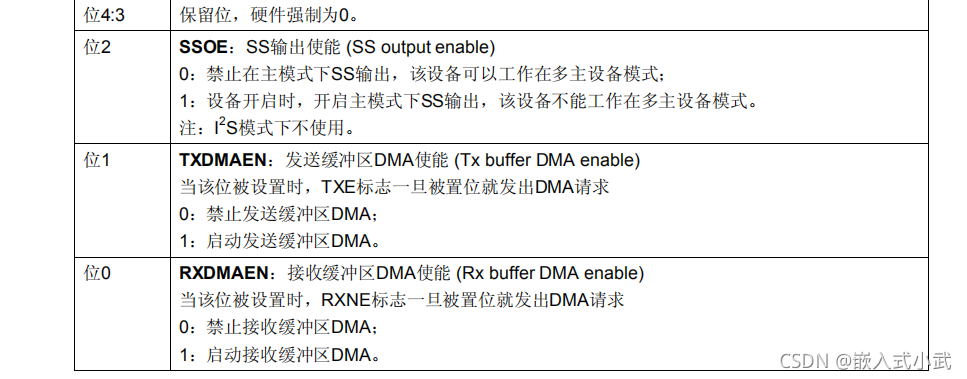

NSS软件和硬件模式,实际是由SPI的相关控制寄存器决定的,这里就简单说下,详细的SPI寄存器可以查阅所使用芯片的芯片手册。

图中就是cortex-m3中的SPI控制寄存器,其他的芯片也基本是一样的。

SPI使用时常见问题

1.接线错误,记住主机的MOSI和从机的MOSI相连,不是交叉相连!!!!!!!

MISO也是一样;不要接反了,我以前也曾接反过,导致一直通信不上。

2.主机和从机,时钟极性(CPOL)和采样方式(CPHA)以及数据发送顺序(高位先行或低位先行)要设置一样,要不然多半会导致数据不一致。

3.对于NSS硬件模式的从机;主机要确保在发送时钟信号前,控制从机的NSS引脚要拉低,通信结束后等待Busy后再拉高NSS!!!!

4.这就意味着主机,主机在SPI初始化时不要立刻使能,要在NSS拉低后,主机SPI再使能,否则,可能会导致从机接收的时钟脉冲少一个,导致从机接收的数据全部为2倍。

5.很多时候,主机的NSS引脚是不用的,直接使用一个任意的GPIO普通引脚片选从机,方便灵活;此时NSS就直接设为软件模式,主机对NSS不做关心。

其他的有机会再补充,本文对SPI协议逻辑没有详细讲解,网上资料很多,就不再重复讲述了,如果需要了解SPI协议逻辑可以参考:SPI原理讲解.

如果有疏漏请指出,共同交流完善

本文介绍了SPI协议中的NSS(或CS)引脚的作用和使用方法,包括硬件模式和软件模式的区别。强调了在SPI通信中接线、时钟配置、NSS控制的重要性,并列举了常见问题及解决策略,如正确设置 NSS 拉低和拉高时机,避免数据丢失。同时提醒在某些情况下,可以使用软件模式灵活控制从机片选。

本文介绍了SPI协议中的NSS(或CS)引脚的作用和使用方法,包括硬件模式和软件模式的区别。强调了在SPI通信中接线、时钟配置、NSS控制的重要性,并列举了常见问题及解决策略,如正确设置 NSS 拉低和拉高时机,避免数据丢失。同时提醒在某些情况下,可以使用软件模式灵活控制从机片选。

5224

5224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?