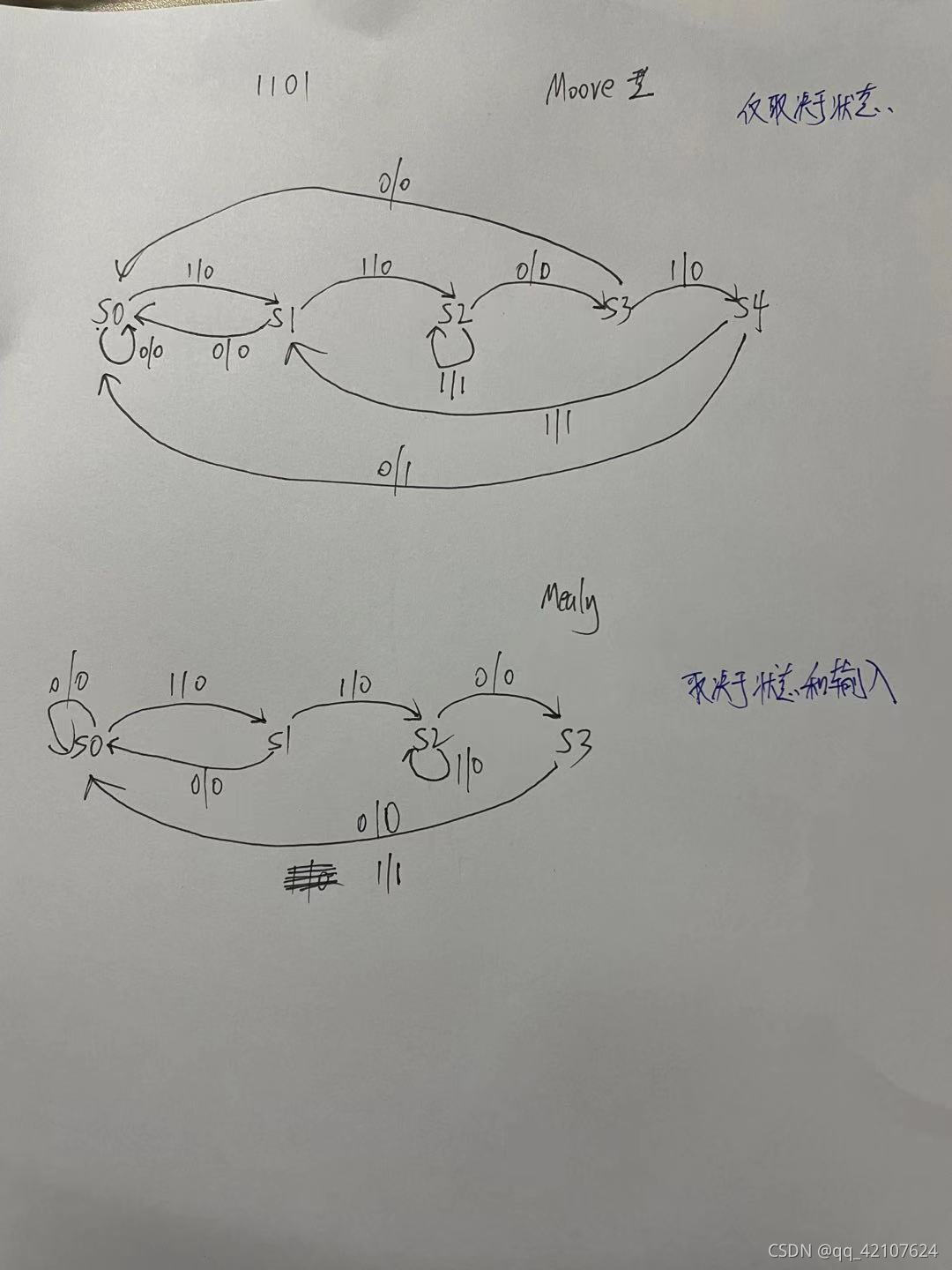

1、Moore状态机:仅取决于当前状态

设计高速电路时,使得输出与时钟几乎同步,即将状态变量直接用作输出,其输出组合逻辑部分只有连线。

2、Mealy状态机:取决于当前状态和输入

- moore完全描述状态转移图会比mealy机多一个状态

- 在verilog代码中就是,moore机的最后输出逻辑只判断state,mealy机的输出逻辑中判断c_

state && input

通过两种方式检测1101,不考虑重叠检测

Moore

//Moore

module detection(

input clk,

input rst_n,

input data_in,

output reg flag

);

reg [4:0] c_state;

reg [4:0] n_state;

parameter s0=5'b00001;

parameter s1=5'b00010;

parameter s2=5'b00100;

parameter s3=5'b01000;

parameter s4=5'b10000;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

c_state<=s0;

else

c_state<=n_state;

end

always@(*)begin

case(c_state)

s0:if(data_in)

n_state=s1;

else

n_state=s0;

s1:if(data_in)

n_state=s2;

else

n_state=s0;

s2:if(data_in)

n_state=s2;

else

n_state=s3;

s3:if(data_in)

n_state=s4;

else

n_state=s0;

s4:if(data_in)

n_state=s1;

else

n_state=s0;

default:n_state=s0;

endcase

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

flag<=0;

else if(c_state==s4)

flag<=1;

else

flag<=0;

end

endmodule

Mealy

//Mealy

module detection(

input clk,

input rst_n,

input data_in,

output reg flag

);

reg [3:0] c_state;

reg [3:0] n_state;

parameter s0=4'b0001;

parameter s1=4'b0010;

parameter s2=4'b0100;

parameter s3=4'b1000;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

c_state<=s0;

else

c_state<=n_state;

end

always@(*)begin

case(c_state)

s0:if(data_in)

n_state=s1;

else

n_state=s0;

s1:if(data_in)

n_state=s2;

else

n_state=s0;

s2:if(data_in)

n_state=s2;

else

n_state=s3;

s3:if(data_in)

n_state=s0;

else

n_state=s0;

default:n_state=s0;

endcase

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

flag<=0;

else if(c_state==s3&&data_in==1'b1) //现在的状态!!!!

flag<=1;

else

flag<=0;

end

endmodule

仿真testbench

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 22:52:31 09/25/2021

// Design Name: Stata_machine

// Module Name: C:/Users/74172/Desktop/FPGA/zsz_project/detection_1101/top.v

// Project Name: detection_1101

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: Stata_machine

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module top;

// Inputs

reg clk;

reg rst_n;

reg data_in;

// Outputs

wire out_mealy;

wire out_moore;

// Instantiate the Unit Under Test (UUT)

Stata_machine uut (

.clk(clk),

.rst_n(rst_n),

.data_in(data_in),

.out_mealy(out_mealy),

.out_moore(out_moore)

);

//clk

initial clk=0;

always #10 clk=~clk;

//rst_n

initial begin

// Initialize Inputs

data_in=0;

rst_n = 0;

#100;

rst_n = 1;

end

reg [7:0] data;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

data<=8'b1011_0110;

else

data<={data[6:0],data[7]};

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

data_in<=0;

else

data_in<=data[7];

end

endmodule

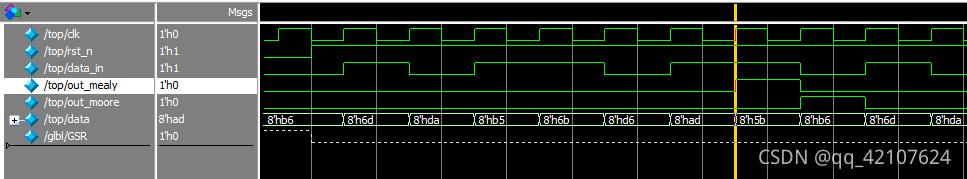

仿真结果

Moore:1101输入最后一个1的上升沿时,n_stata为s4,经过下一个上升沿后,c_stata为s4,再经过输出触发器的同步之后,下一个上升沿输出为1

Mealy:1101在输入0时n_stata为s3,下一个上升沿,c_stata为s3,并且此时输入为1时候,那么再经过输出触发器同步之后,下一个上升沿输出为1

故Moore比Mealy输出满一个周期

注释:Alt + C

取消注释:Shift + Alt + C

本文对比了Moore和Mealy状态机在电路设计中的应用,重点讲解了它们如何影响输出逻辑和时钟同步。Moore机仅依赖于当前状态,而Mealy机还考虑输入。通过Verilog代码实例,展示了两者在检测特定序列时的不同行为。仿真结果表明Moore机输出周期完整,Mealy机则根据输入条件触发。

本文对比了Moore和Mealy状态机在电路设计中的应用,重点讲解了它们如何影响输出逻辑和时钟同步。Moore机仅依赖于当前状态,而Mealy机还考虑输入。通过Verilog代码实例,展示了两者在检测特定序列时的不同行为。仿真结果表明Moore机输出周期完整,Mealy机则根据输入条件触发。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?