一、阻塞赋值

代码一:

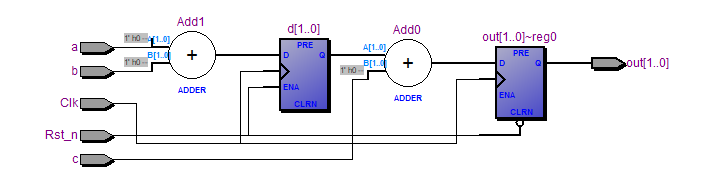

module block_nonblock(Clk, Rst_n, a,b,c,out);

input Clk;

input Rst_n;

input a,b,c;

output reg [1:0]out;

//out = a + b + c;

//d = a + b;

//out = d + c;

reg [1:0]d;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

out = 2'b0;

else begin

d = a + b; //阻塞赋值

out = d + c;

end

endmodule

代码二:

交换cout和d的顺序:

module block_nonblock(Clk, Rst_n, a,b,c,out);

input Clk;

input Rst_n;

input a,b,c;

output reg [1:0]out;

//out = a + b + c;

//d = a + b;

//out = d + c;

reg [1:0]d;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

out = 2'b0;

else begin

out = d + c;

d = a + b; //阻塞赋值,out = d + c;在前面

end

endmodule

二、非阻塞赋值

代码三:

module block_nonblock(Clk, Rst_n, a,b,c,out);

input Clk;

input Rst_n;

input a,b,c;

output reg [1:0]out;

//out = a + b + c;

//d = a + b;

//out = d + c;

reg [1:0]d;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

out <= 2'b0;

else begin

d <= a + b; //非阻塞赋值

out <= d + c;

end

endmodule

代码四:

交换cout和d顺序:

代码五:手动加入延时

`timescale 1ns/1ps

`define tp 1 //手动模拟延时,公司没说就不能用

module block_nonblock(Clk, Rst_n, a,b,c,out);

input Clk;

input Rst_n;

input a,b,c;

output reg [1:0]out;

//out = a + b + c;

//d = a + b;

//out = d + c;

reg [1:0]d;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

out <= 2'b0;

//out <= #`tp 2'b0; //加入延时

else begin

d <= a + b; //非阻塞赋值,out = d + c;在前面

//d <= #`tp a + b; //加入延时

out <= d + c;

//out <= d + c; //加入延时

end

endmodule

三、结论

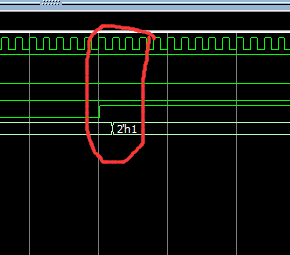

1、’在非阻塞赋值中,交换顺序并不会影响最后结果,运算并没有先后

2、结果出现延时的原因可能是寄存器的建立和运算(代码一中出现了一个寄存器,而代码二中出现了两个寄存器,所以代码二延时应该更高)

500

500

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?