HDLBits错题积累

Verilog Language

Procedures

Always if2

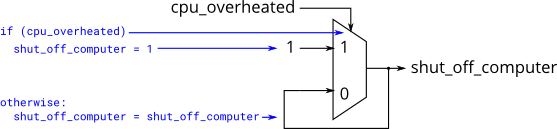

The following code contains incorrect behaviour that creates a latch. Fix the bugs so that you will shut off the computer only if it’s really overheated, and stop driving if you’ve arrived at your destination or you need to refuel.

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

end

// synthesis verilog_input_version verilog_2001

module top_module (

input cpu_overheated,

output reg shut_off_computer,

input arrived,

input gas_tank_empty,

output reg keep_driving ); //

always@(*) begin

if(cpu_overheated) begin

shut_off_computer =1 ;

end

else begin

shut_off_computer = 0;

end

end

always@(*) begin

if (~arrived) begin

keep_driving = ~gas_tank_empty;

end

else begin

keep_driving = 0;

end

end

endmodule

结论:

在如果没有指定else 块中的结果,一般为0。

endmodule

###### 结论:

在如果没有指定else 块中的结果,一般为0。

1360

1360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?