DDR4相比DDR3的相关变更点

相比DDR3,DDR4存在诸多变更点,其中与硬件设计直接相关的变更点主要有:

增加Vpp电源;

VREFDQ删除;

CMD、ADD、CTRL命令的端接变更为POD模式;

增加ACT_n控制指令

为增强数据读写可靠性增加的变更点主要有:

DBI;

Error Detection;

1 电源变化

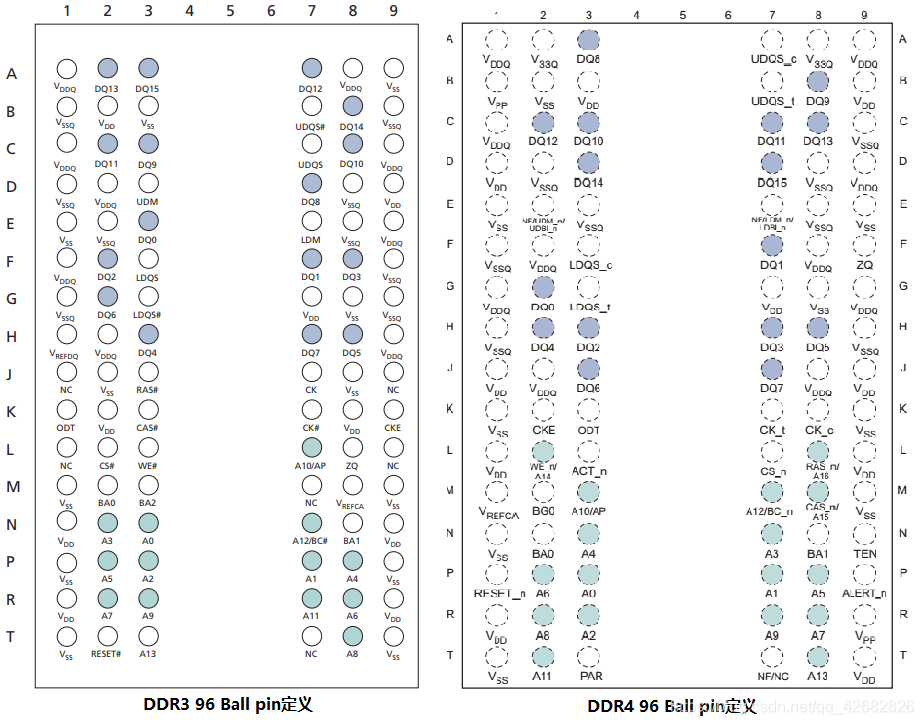

DDR3与DDR4的96 Ball封装pin定义对比如图1所示,DDR3中存在VDD、VDDQ、VREFDQ、VREFCA四种电源,其中VDD=VDDQ=1.5V,VREFDQ=VREFCA=0.75V。DDR4中电源网路变为VDD、VDDQ、Vpp、VREFCA,其中VDD=VDDQ=1.2V,Vpp=2.5V,VREFCA=0.6V,增加了Vpp电源,删除了VREFDQ电源,电源对比结果如表1所示。

图 1 DDR3和DDR4 96 Ball pin定义对比

表 1 DDR3 & DDR4电源网络对比

| DDR3电源网络 | 电源电压 | DDR4电源网络 | 电源电压 | |

|---|---|---|---|---|

| 电源名称 | 电压/V | 电源名称 | 电压/V | |

| VDD | 1.5 | VDD | 1.2 | |

| VDDQ | 1.5 | VDDQ | 1.2 | |

| VREFDQ | 0.75 | VPP | 2.5 | |

| VREFCA | 0.75 | VREFCA | 0.6 |

DDR4相比DDR3,核电压由1.5V降低为1.2V,相对应的,CMD、ADD、CTRL信号的参考电压VREFCA也下降到0.6V,这样可以降低DDR4的功耗。比较大的区别在于,DDR4中取消了VREFDQ,增加了Vpp。

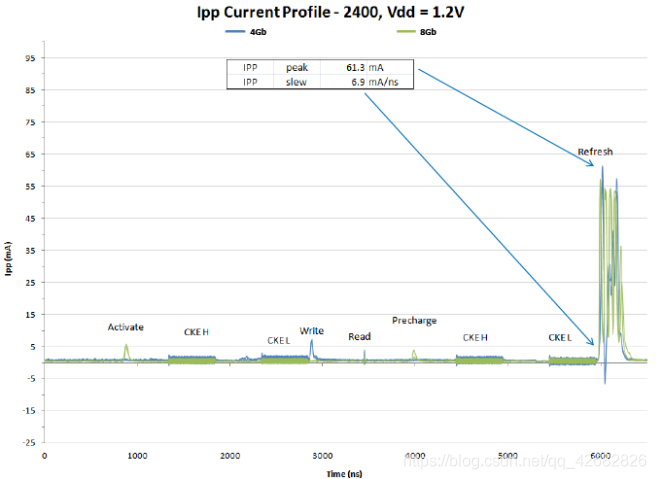

Vpp并非用于替代VREFDQ,Vpp是为DDR4内部的word line供电,从而保证DDR4的内核可以使用1.2V供电。也就是说,DDR4内核电压的下降一部分原因是由于引入了Vpp。Vpp的电流Ipp为窄脉冲电流,幅值在20mA~60mA之间。

图 2 Ipp电流分布

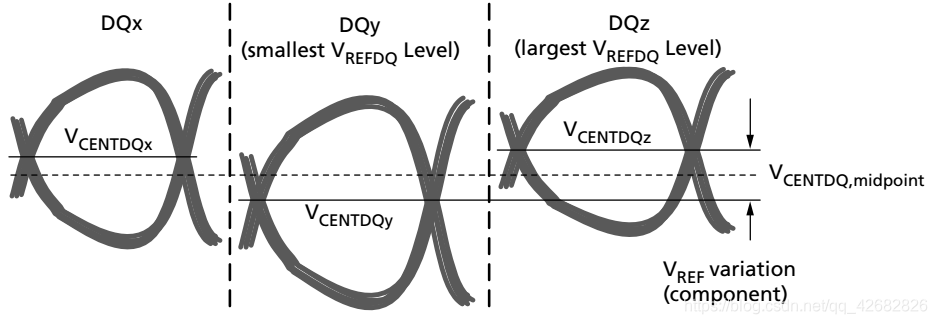

DDR4中的VREFDQ并非直接被删除,而是被集成在DDR4内部。这样就可以在DDR4内部动态调整VREFDQ的范围,使得DQ信号具有更强的鲁棒性。Micron的DDR4内部可以实现VREFDQ以0.65%VDDQ为分辨率的两种动态调整范围,Range1—Between 60% and 92.4% of VDDQ,Range2—Between 40% and 77.5% of VDDQ,两种动态调整范围分别应用于模组应用和单片应用场景。基于VREFDQ动态范围的需求,DDR4内部引入了VREFDQ校准机制。VREFDQ动态调整的目的是为了找到DQ信号的中间参考电平VCENT_DQ(pin mid),如图3所示。

图 3 VREFDQ对VCENT_DQ(pin mid)的影响

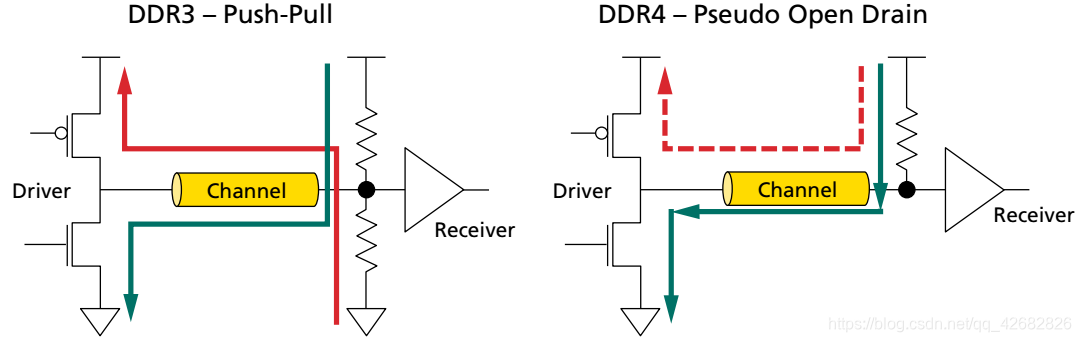

2 端接方式变化

DDR3中对于CMD、ADD、CTRL信号使用的是戴维南端接,端接电压为VTT=VDD/2,这将导致CMD、ADD、CTRL信号无论是低电平还是高电平,线路中均存在电流,故导致较大的功耗;DDR4中对于CMD、ADD、CTRL信号使用POD端接,也就是并联端接形式,这样在CMD、ADD、CTRL信号为高电平时线路中就不会存在电流,可以降低功耗。DDR3和DDR4端接方式的对比如图4所示。

图 4 DDR3和DDR4端接方式对比

3 ACT_n信号

为了避免由于容量增加、特性增加等因素给DDR4带来过多的管脚增加,DDR4中引入了ACT_n信号对部分ADD管脚进行功能复用。

如图1所示,DDR4中RAS_n与A16,CAS_n与A15,WE_n与A14管脚均存在复用关系,具体功能由ACT_n的电平决定,逻辑如表2所示。

表 2 ACT_n电平与三个管脚的复用关系

| ACT_n逻辑状态 | ACT_n逻辑状态 | |

|---|---|---|

| PIN NO. | High | Low |

| L2 | A14 | WE_n |

| M8 | A15 | CAS_n |

| L8 | A16 | RAS_n |

PIN NO. ACT_n逻辑状态

4 DBI功能

如2节所述,DDR4的DQ信号的端接使用POD模式,而POD端接在信号为高电平时无功耗需求,故为降低DDR4功耗,应尽量减少DQ信号中0电平出现的概率,使用的技术即为DBI(Data Bus Inversion)。

DBI功能带来的特性有:

每个DBI_n信号对应1byte,也就是说,1个DBI_n管脚对应X8 DDR4;UDBI_n、LDBI_n对应X16 DDR4;

DBI_n管脚与DM管脚复用,DM功能与DBI写功能不能同时使用;

可以支持X8和X16两种DDR4,不支持X4 DDR4;

Read/Write可以分别使用DBI,通过MR5管脚进行控制;

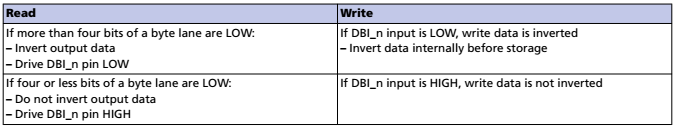

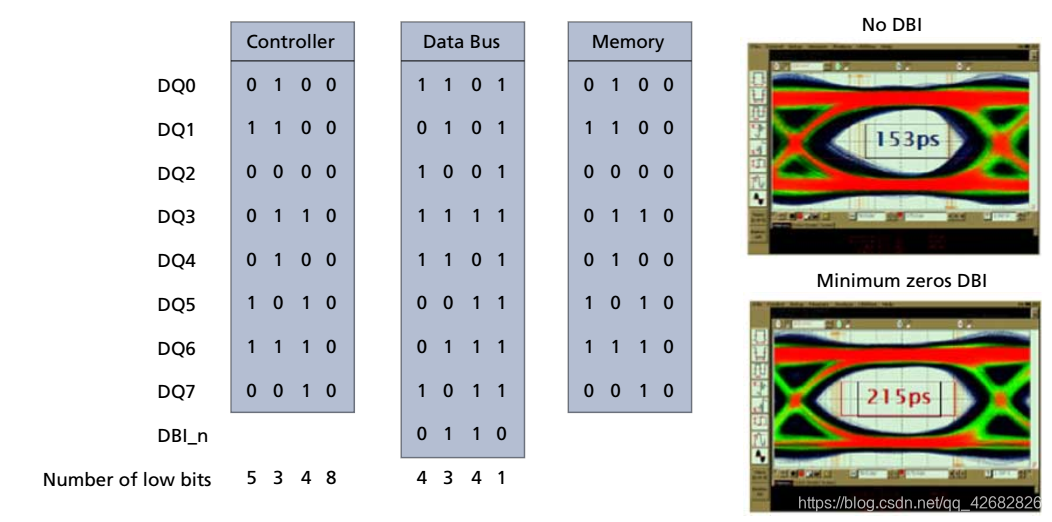

DQ信号每8bit存在4bit以上的0时,DBI会自动对DQ信号进行反向,如图5所示。DBI示例如图6所示。

图 5 DBI的工作条件

图 6 DBI示例

5 Error Detection功能

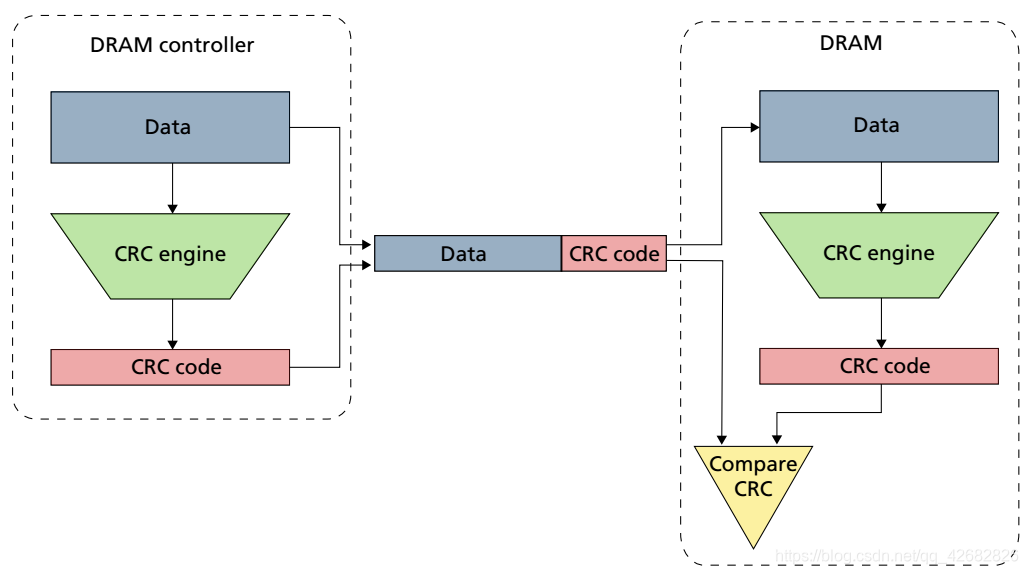

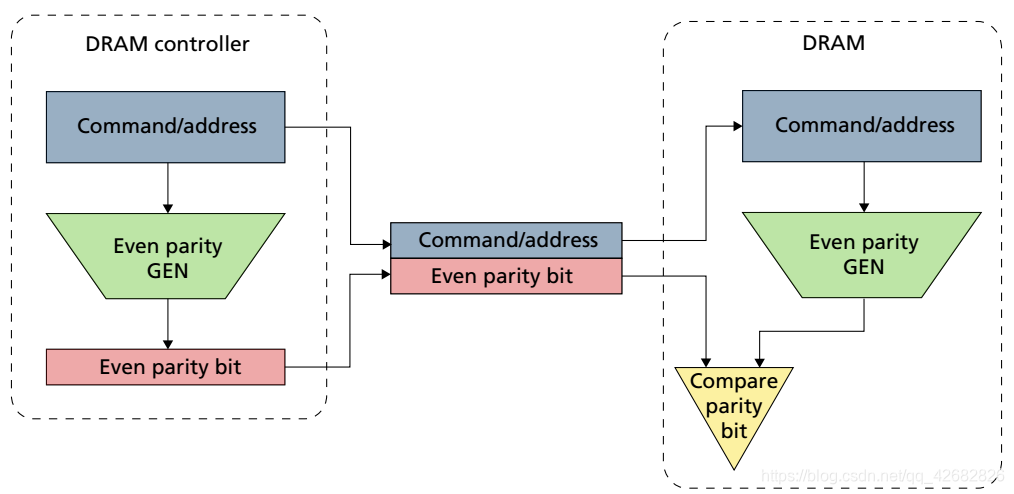

随着DDR4数据速率的提升,误码率也随之提升,故DDR4中增加Error Detection技术对DQ和CMD、ADD信号。

对于DQ信号使用内置的CRC校验,如图7所示;对于CMD、ADD、CTRL使用内置的奇偶校验,如图8所示。

图 7 DQ信号CRC校验原理

图 8 CMD、ADD、CTRL奇偶校验原理

参考:

Micron——TN-40-40: DDR4 Point-to-Point Design Guide Introduction;

917

917

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?