Cadence层次化设计-用与非门和反相器构成振荡器

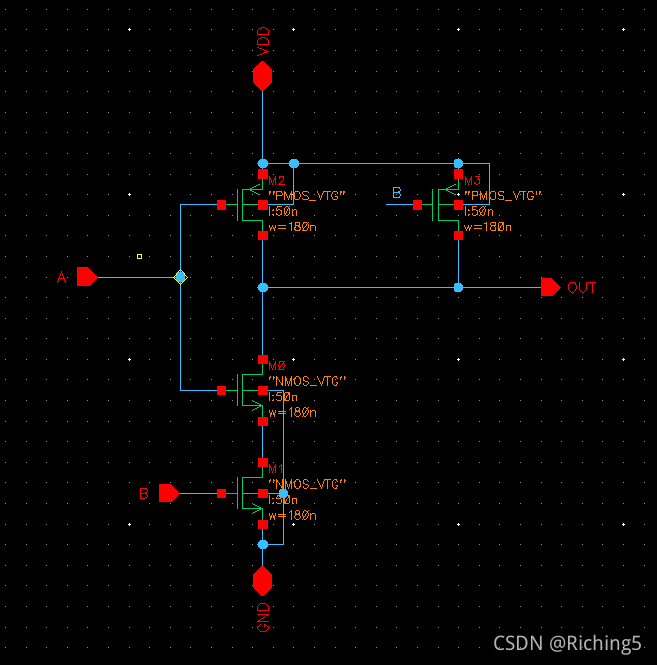

与非门电路原理图

第二个pmos的输入用的是label来连接输入B。按L即可创建label

注意M0的衬底电位

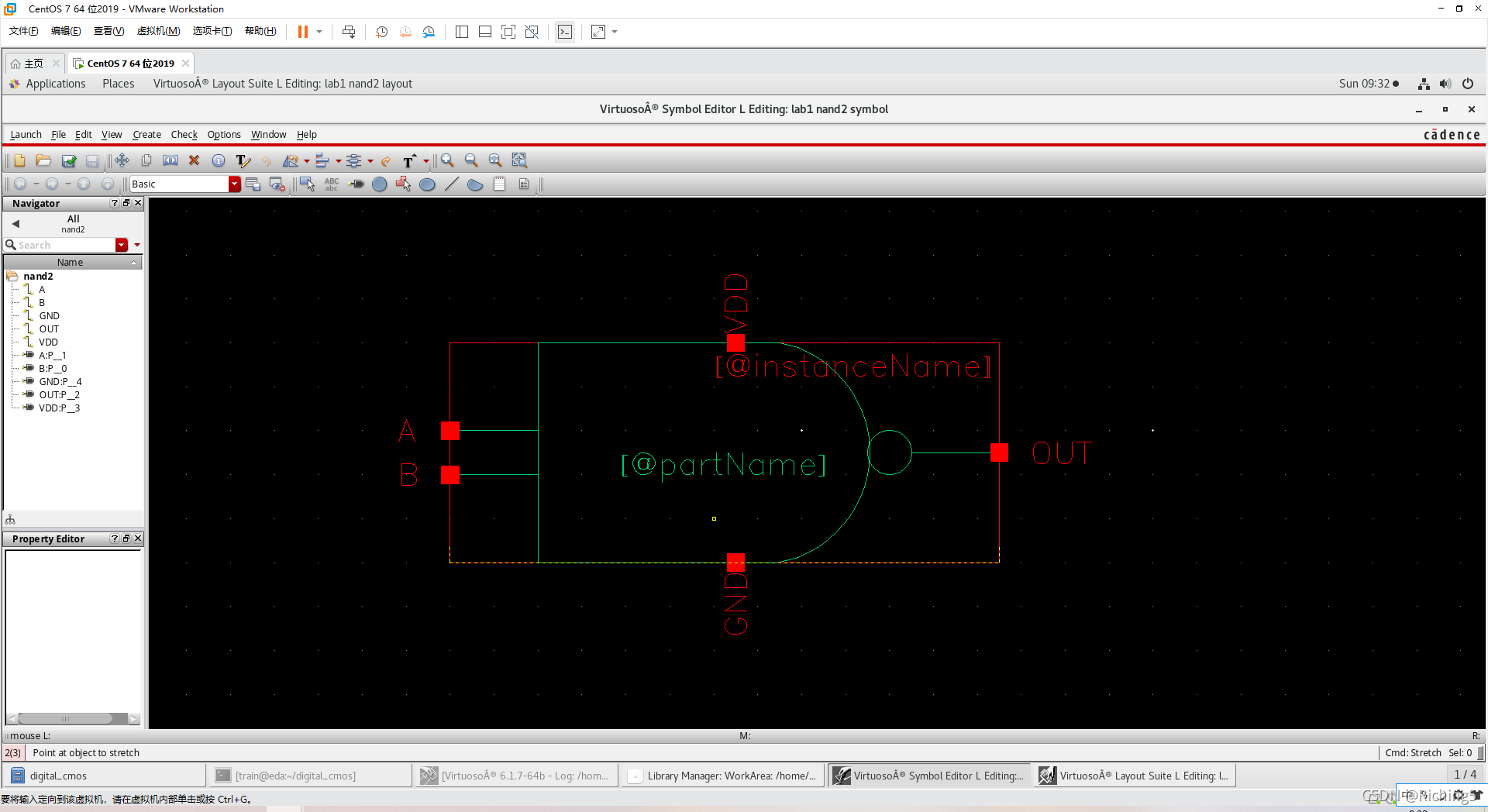

创建与非门symbol

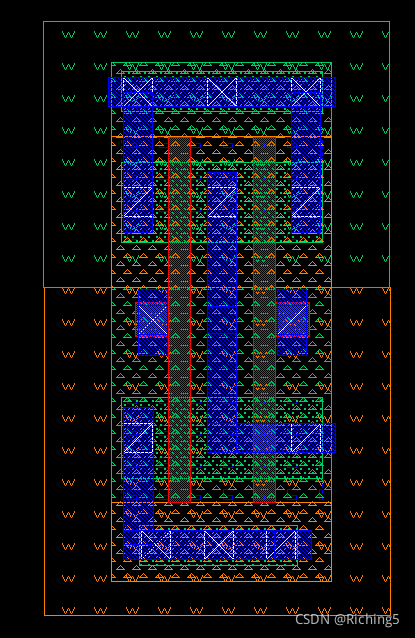

与非门版图

我出错的点:没根据管子宽长来设置active的宽度;没画vtg;pin没用net的metal1画;忘记设置格点。

折磨人呀

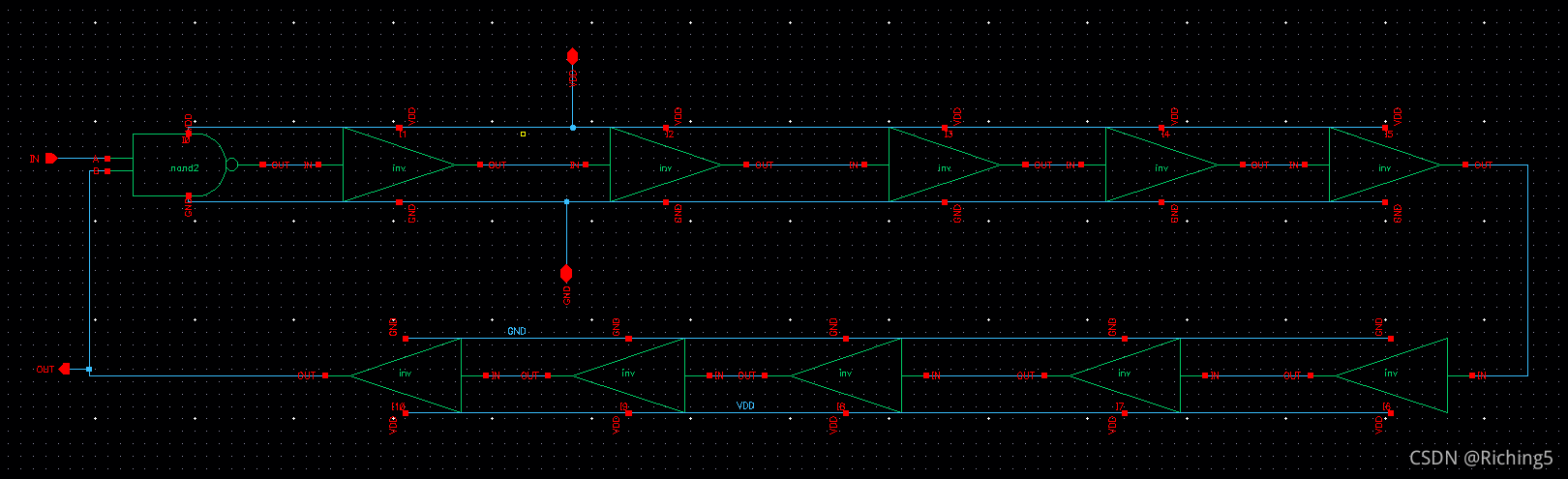

用之前的反相器和上面的与非门做振荡器

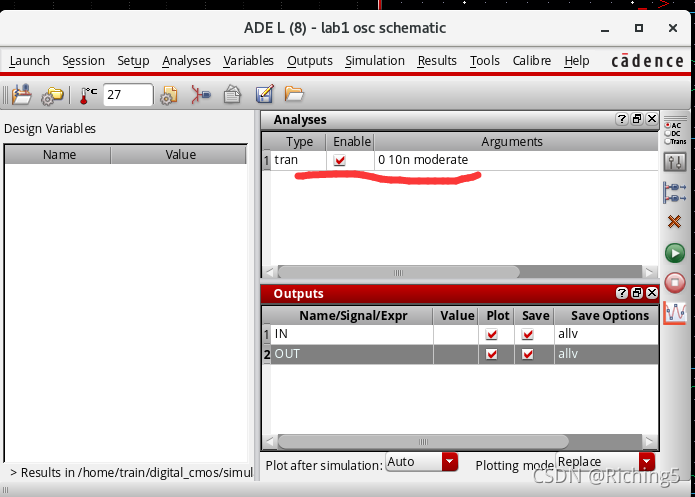

仿真

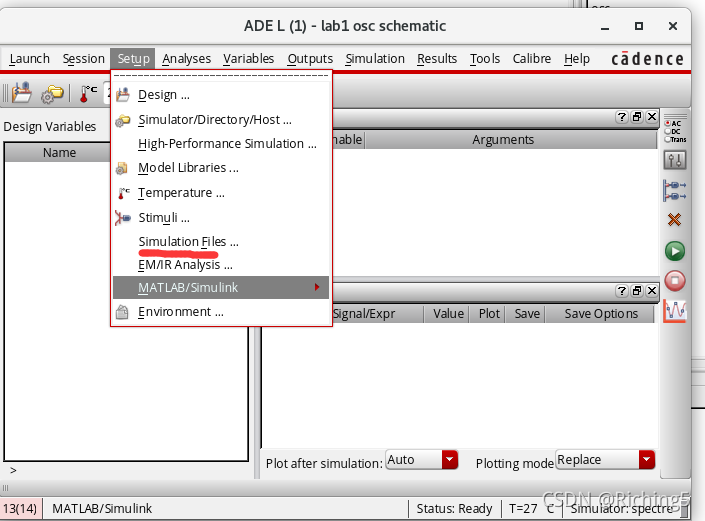

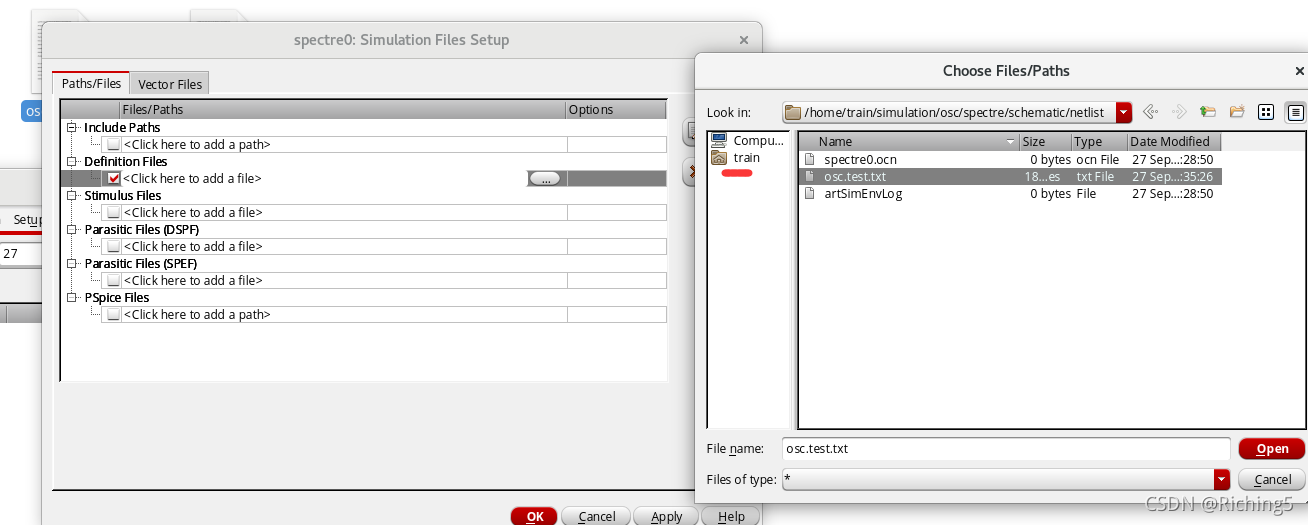

这里我们采用另外一种仿真方式,编写好仿真文件来仿真,而不用添加激励源。

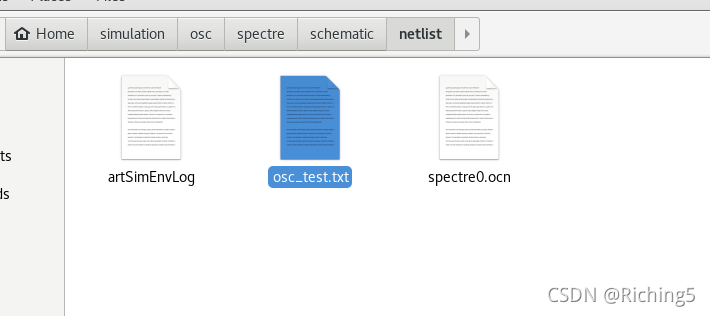

放到这个目录下

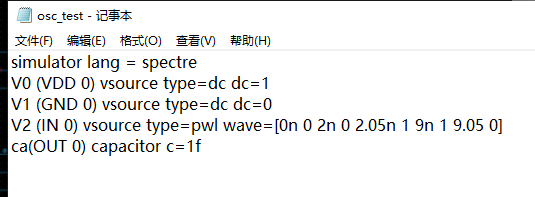

simulator lang = spectre 仿真用的类型(maybe)

V0 (VDD 0) vsource type=dc dc=1 设VDD=1v

V1 (GND 0) vsource type=dc dc=0 设GND=0v

V2 (IN 0) vsource type=pwl wave=[0n 0 2n 0 2.05n 1 9n 1 9.05n 0] 设置IN为脉冲波,最开始0ns为0v,2ns后还是0v,到2.05ns时为1…这里时间为绝对时间,都是相对于最开始0ns时

ca(OUT 0) capacitor c=1f 设置负载

添加这个文件,按路径点进去没有的话可以点一下train,再按路径。

但是我们同样需要设置tran

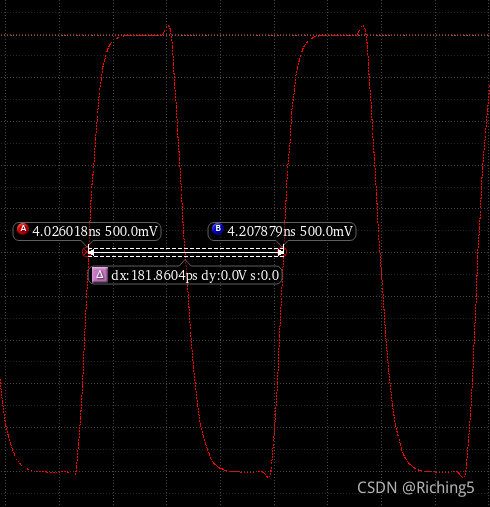

可以看到振荡周期为181ps

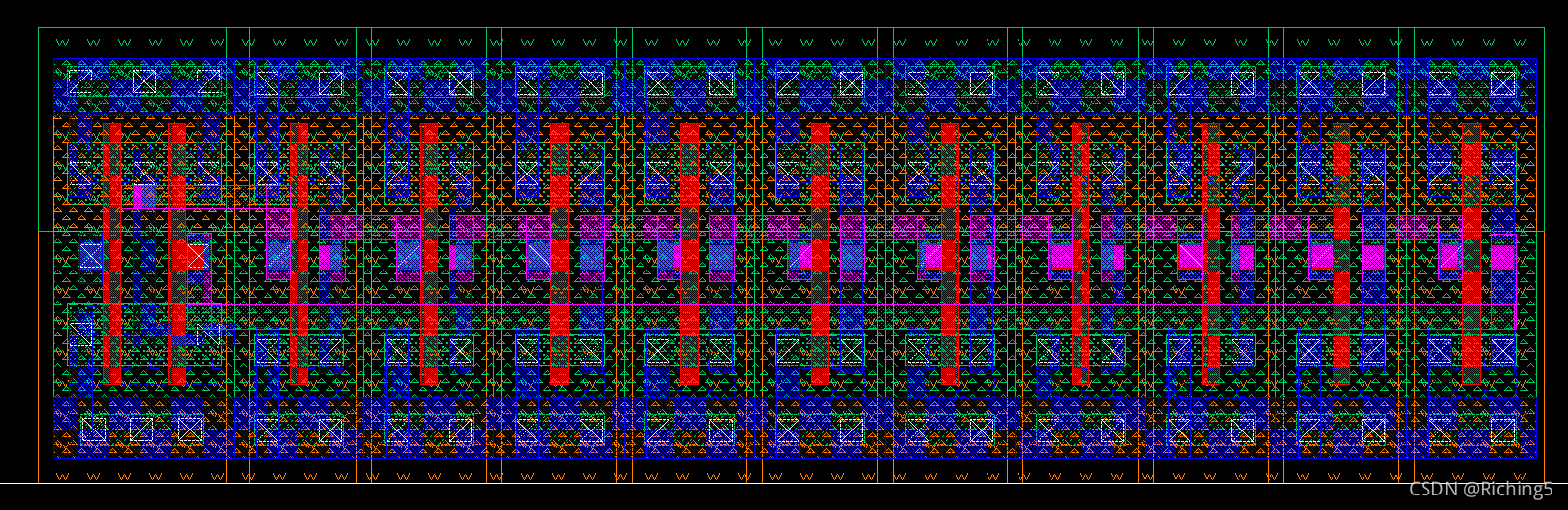

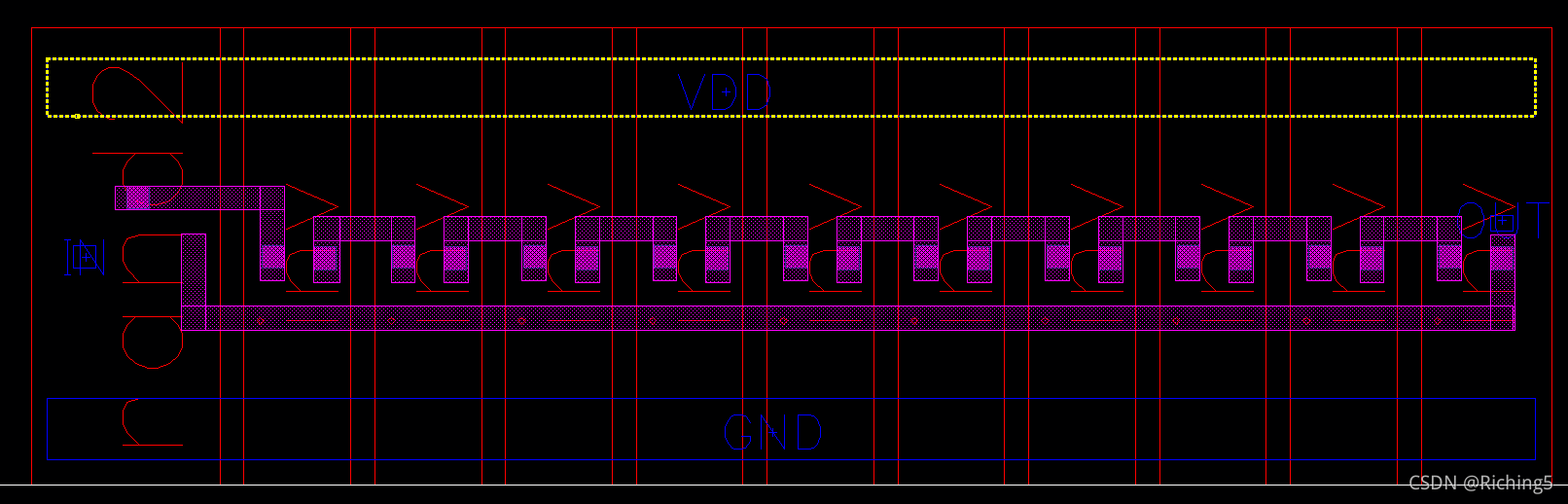

画振荡器版图

按i添加之前画好的版图,记得先按E设置显示图层数,不然看不到器件内部版图。

此时出现了在例化layout时元件离鼠标很远的问题,这就是在之前画版图时没把版图放在十字附近。

单是把与非门和非门放在一起做DRC就花了很多时间调整,一切为了对称

总结:1、与非门和非门的总长、n/pwell和implant 长度、栅长要相同

2、vdd gnd部分的metal完全覆盖well

3、栅极的输入放在同一水平线上

然后用via1和metal2连接这些器件输入输出。

(contact 特指poly到M1,via指Mx到Mx-1或者Mx+1,一般工艺via的接触阻抗小于contact)

添加pin,注意是用metal1的net

同样的我们对版图进行DRC LVS PEX,这里不做赘述。

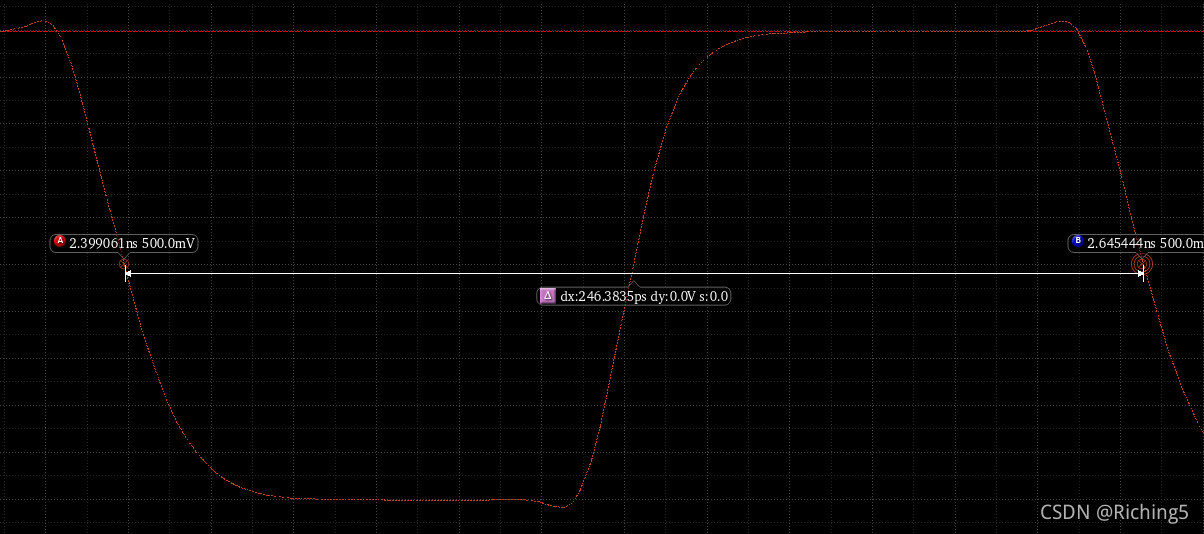

后仿真结果

现在振荡周期为246ps

本文详细介绍了使用与非门和反相器构建振荡器的步骤,包括电路原理图的绘制、与非门symbol和版图的设计、振荡器的仿真以及版图布局。在仿真中,通过设置不同电压源和负载,观察到了181ps和246ps的振荡周期。在版图设计时强调了对称性和尺寸一致性的重要性,并提醒注意接触和via的使用以及pin的金属层选择。

本文详细介绍了使用与非门和反相器构建振荡器的步骤,包括电路原理图的绘制、与非门symbol和版图的设计、振荡器的仿真以及版图布局。在仿真中,通过设置不同电压源和负载,观察到了181ps和246ps的振荡周期。在版图设计时强调了对称性和尺寸一致性的重要性,并提醒注意接触和via的使用以及pin的金属层选择。

1492

1492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?