记IC验证&测试实习 2020.11.13 - 2021.1.22

虽然过去挺久了hhh但感觉大四实习学到东西可以整理一下。实习部分大概分为两部分吧:测试(7天搬砖)& 验证部分(搬砖学习)

1.芯片测试----(成型的芯片)

1.1 任务1 bist通信测试+电压/温度测试

1.2 计算PLL锁相环输出频率

2.芯片验证

2.1 任务1:学Verilog

2.2 任务2:学Linux系统vi/vim

2.3 任务3:通过JTAG读写寄存器,通过AHB总线读写寄存器,查看仿真波形波形发现设计寄存器中的错漏。

扫描寄存器,读写寄存器;读设计文档理解芯片功能,根据功能确定读写验证的方案以及目标;验证,发现设计错误,撰写验证文档并于设计的老师反馈;完成覆盖率和回归测试。通过检查log与观察波形/打印所得数据 来检查是否符合芯片功能。

3.Verilog设计一个寄存器

3.1 看懂一个类似L1寄存器的Verilog代码

3.2 设计一个cache L2寄存器

1.芯片测试----(成型的芯片)

概述:bist通信测试+电压/温度测试

1.1 任务1:通过外部接口 读写写DIFIFO寄存器 ,控制REQCR / REQSR寄存器 触发总线桥发起AHB请求 ------读写bist寄存器以完成bist通信测试,通过读取返回的数据判断通信测试是否成功。

主要通过对bist csr寄存器的读写,来控制RAM的bist行为,并检查bist结果;

1)知道如何计算目标寄存器的地址;

基地址+偏移地址;

基地址:芯片设计手册

偏移地址:芯片设计手册每个寄存器的说明部分,都是偏移地址

2)知道如何对目标寄存器进行读写操作;

如果是一个写操作,流程大致如下:

1)通过外部接口输入“写DIFIFO寄存器”命令,输入写操作数据;

2)通过外部接口输入“写REQCR寄存器”命令,输入写操作的长度信息,同时指示是写操作;

3)通过外部接口输入“写REQAR寄存器”命令,输入写操作的起始地址,同时触发总线桥发起AHB请求。

如果是一个读操作,流程大致如下:

1)通过外部接口输入“写REQCR寄存器”命令,输入读操作的长度信息,同时指示是读操作;

2)通过外部接口输入“写REQAR寄存器”命令,输入读操作的起始地址,同时触发总线桥发起AHB请求;

3)通过外部接口输入“读DOFIFO寄存器”命令,得到读操作返回的数据。

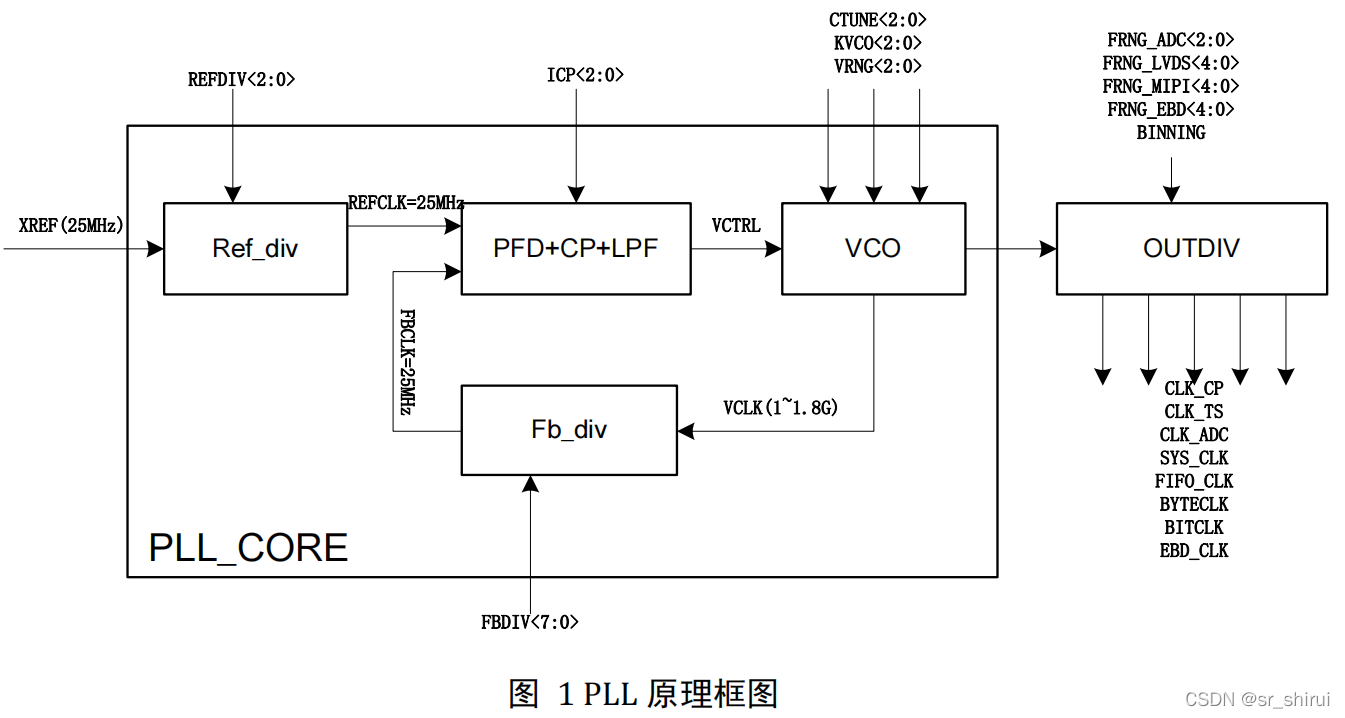

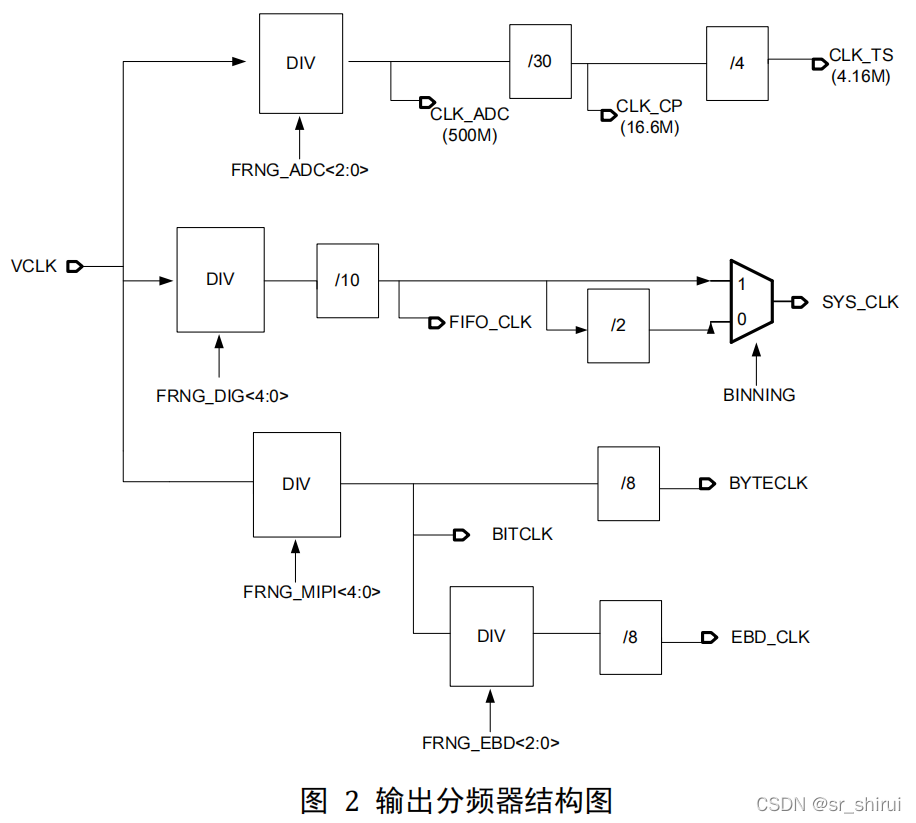

1.2 任务2:计算PLL(phase locked loop)锁相环输出频率,适当调整拨码开关

PD:鉴相器–相位比较,完成输入信号与反馈信号的相位比较。输出电压正比于两个输入电压的相位差

(PFD:鉴频鉴相器–系统的精度和稳定度 CP:电荷泵–宽的频率捕捉范围和快速锁定能力 LPF:低通滤波器–平滑滤波)

LF:环路滤波器–滤除鉴相器产生电压的高频部分,平滑滤波作用

VCO:压控振荡器–受控电压源产生的振荡频率

1、压控振荡器的输出经过采集并分频;

2、和基准信号同时输入鉴相器;

3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;

4、控制VCO,使它的频率改变;

5、这样经过一个很短的时间,VCO的输出就会稳定于某一期望值。

注:此款芯片Xref=25M首先经过R分频,输出25M给PFD+CP+LPF,传递给VCO,在锁相环内部传递给Fb分频,在外部传给out分频,产生不同频率传递给时钟

2.芯片验证

2.1 任务1:学Verilog,语法与进阶练习我将在下一个博客里详写

2.2 任务2:学Linux系统vi/vim,查看波形等工作,我已上传资源Linux常用命令以及vim常用命令

2.3 任务3:通过JTAG接口读写寄存器,通过AHB总线读写寄存器,查看仿真波形波形发现设计寄存器中的错漏。( rfuse_test; tfuse_test; reg_rfuse_test; reg_tfuse_test; bist_test; )

扫描寄存器,读写寄存器;读设计文档理解芯片功能,根据功能确定读写验证的方案以及目标;验证,发现设计错误,撰写验证文档并于设计的老师反馈;完成覆盖率和回归测试。通过检查log与观察波形/打印所得数据 来检查是否符合芯片功能。

发现错误举例:

1.读入的和写入的数据在不同的位置(寄存器位置写串了)

2. 控制信号没有自清除–通过波形观察

注意:有些寄存器只读寄存器无法写入,注意寄存器写入条件

代码思想是:在确定的寄存器地址上写1,并通过查看1的位置,是否完成写1操作来检查确定寄存器是否成功写1,写1的地址是否正确,写1是否符合寄存器设置的条件。代码片段如下:

在这里插入代码片

task rfuse_test;

begin

req_tbox_reg_wad(1'b1,13'h04, 32'h12); // CMR

$display("---------redundance efuse test-----------");

for(K=0;K<8;K=K+1)begin

$display("---------Bank-%x-----------",K);

nn=32'h01;

for(N=0;N<32;N=N+1)begin

wait(ef_access_fsm[5:0]==6'h03);

// $display("ef_access_fsm==0x03",$time);

#20;

// $display("---------nn==-%x-----------",nn);

req_ef_red_wbad (1'b1, K[2:0],K[7:0],nn[31:0]);

#2000;

wait(ef_access_fsm[5:0]==6'h03);

// $display("ef_access_fsm==0x03",$time);

req_ef_red_wbad (1'b0, K[2:0],K[7:0],32'h00);

nn=nn<<1;

end

end

$display("---------test-----------");

for(K=0;K<8;K=K+1)begin

$display("-------KKK=%x---------",K);

// for(N=0;N<32;N=N+1)begin

req_ef_red_wbad (1'b0, K[2:0],K[7:0],32'h00);

// end

end

end

endtask

task bist_test;

begin

$display("# Bist Test Start.........",$time);

force tb_chip.u_ddr4_chip.u_ddr4_core.u_mram_wrap.DIN_DL=64'h1;

tb_chip.u_ddr4_chip.u_ddr4_core.u_efuse_wrap.u_tbox.u_ctrl_reg.GP_BIST_enable=1'b1;

wait(tb_chip.u_ddr4_chip.u_ddr4_core.u_efuse_wrap.u_tbox.u_ctrl_reg.bist_done);

#2000;

//-----------w-----A------D---

req_reg_wad(1'b0,16'h8015,32'h00);

req_reg_wad(1'b0,16'h8006,32'h00);

req_reg_wad(1'b0,16'h8007,32'h00);

req_reg_wad(1'b0,16'h8008,32'h00);

req_reg_wad(1'b0,16'h800a,32'h00);

end

endtask

3.Verilog设计一个寄存器

3.1 看懂一个类似L1寄存器的Verilog代码

3.2设计一个cache L2寄存器

cpu知识整理

理论来源

https://github.com/lvyufeng/step_into_mips

目录

1.单周期设计各部分功能

2.5级流水线加入后的架构与性能提升

3.cache以及各存储器的作用功能

1.单周期设计各部分功能

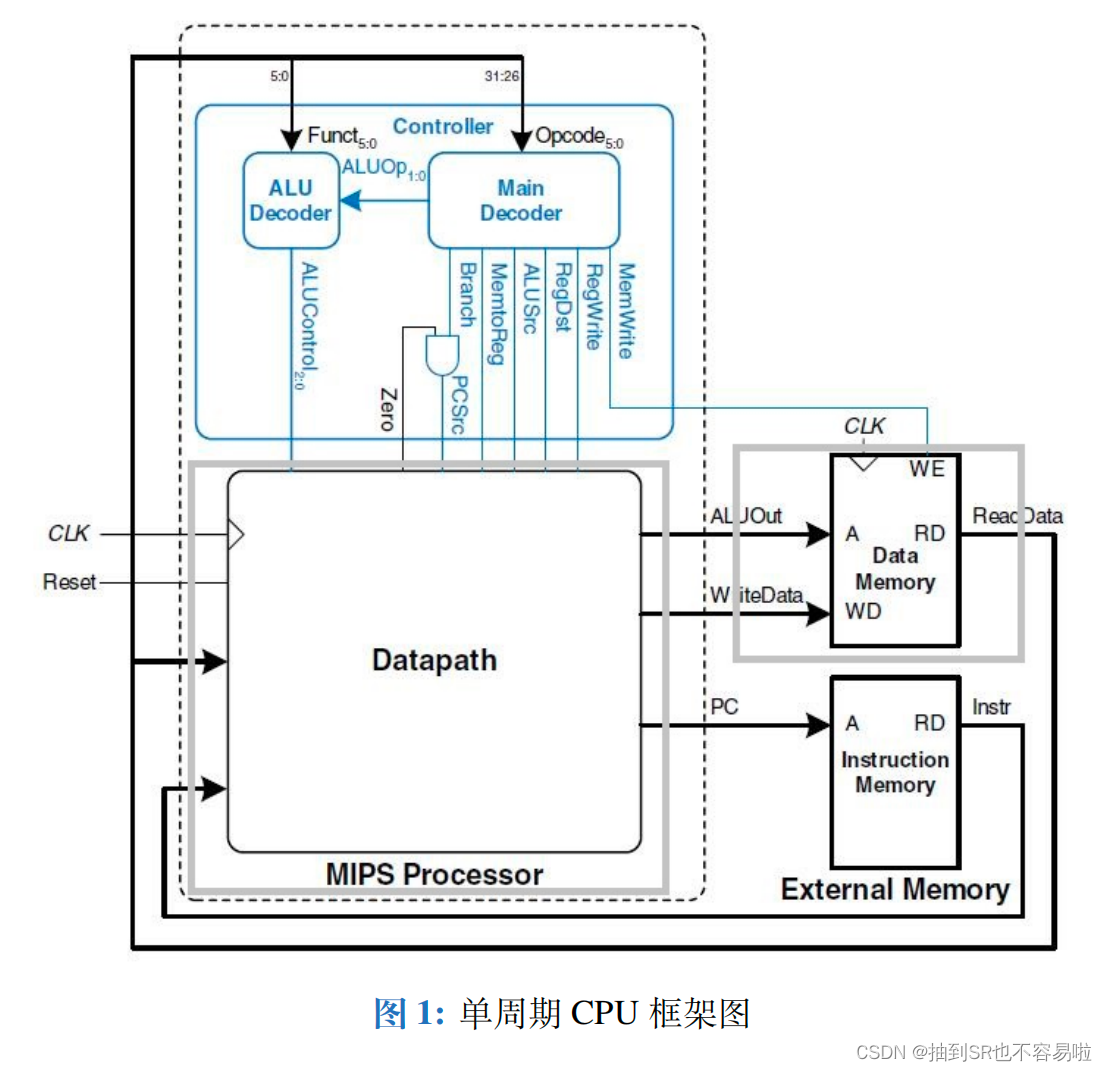

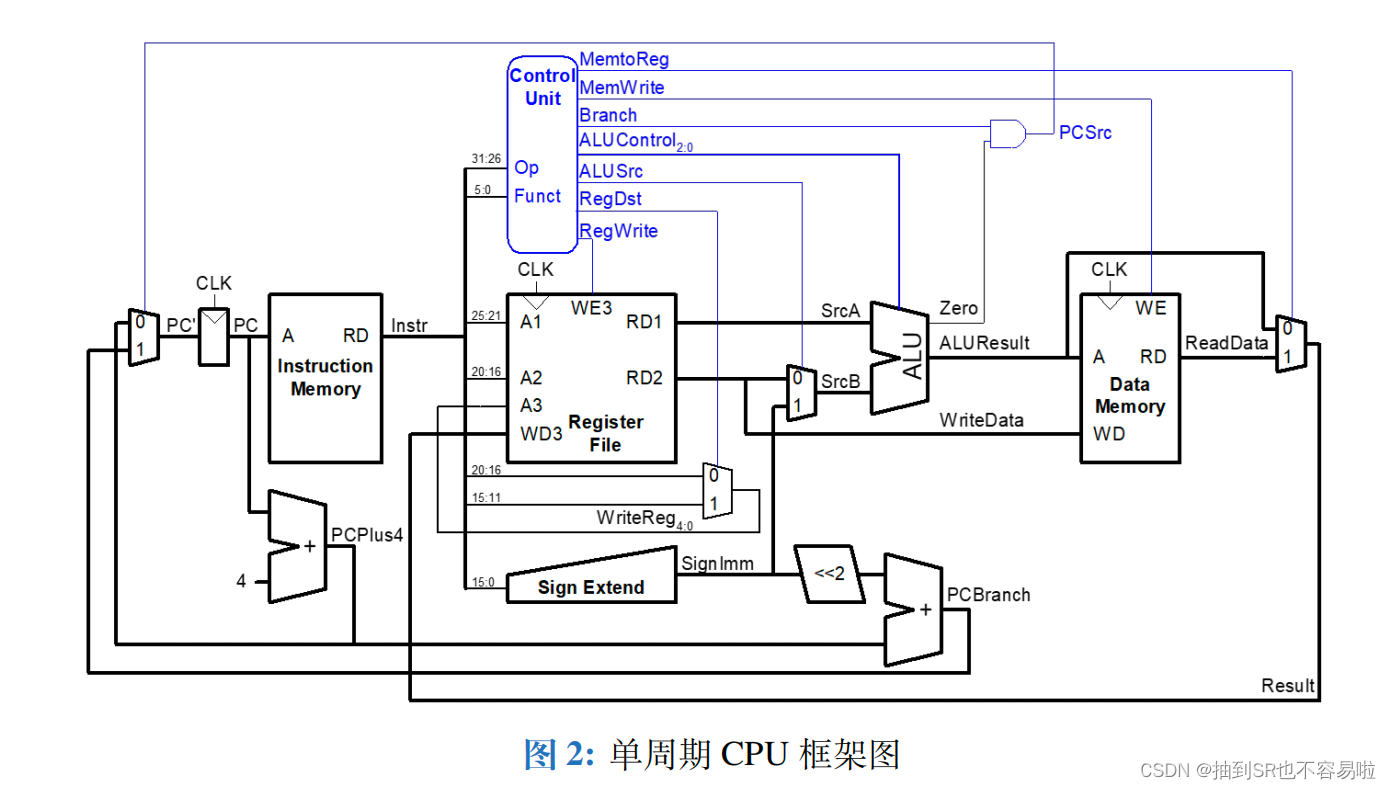

下图是一个单周期的cpu设计,cpu有5个执行步骤取指,译码,执行,访存,回写。

最上面的单元负责将指令的【31:26】=op-code译码器:

189

189

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?