第七章:功率门控示例

SALT技术示例工程提供了测试本书所述功率门控和状态保留方法的平台。本章我们会给出更详细的系统设计和RTL代码。

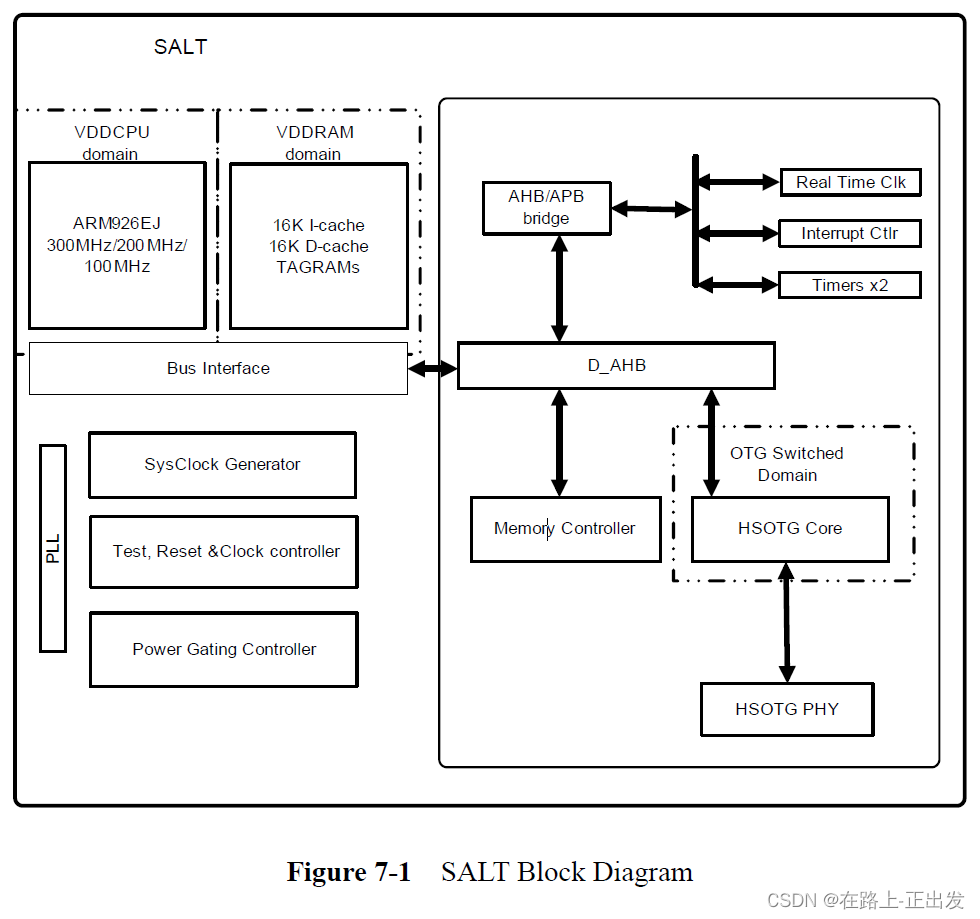

SALT芯片用90纳秒工艺技术实现,包含ARM处理器,AMBA总线以及对应的外设,新思科技(Synoposys)的USB OTG数字核和物理层PHY。ARM核与USB核独立电源门控。ARM核使用全状态保留;USB核使用部分状态保留。两个核都使用header样式的开关结构;因此二者共地,通过切换VDD实现电源开关。

在第一节,我们描述处理器的功率门控设计。图7-1所示是一个简化的SALT芯片结构框图。

7.1 支持的泄露模式

大多数基于电池供电的处理器设计必须仔细处理性能(以支持产品功能)和低功耗(以支持更长的电池寿命)之间的平衡。性能要求引导我们采用更高的性能、更容易泄漏的工艺。为了保持更长的电池寿命,我们需要提供积极的泄漏管理。

SALT工程中,处理器使用了4个低功耗模式。所有模式中,功率控制器产生SLEEP信号以进入低功耗模式,产生WAKE信号退出低功耗模式。为了增加泄露功率的节省量,增加通电断电的时间,包含如下模式:

订阅专栏 解锁全文

订阅专栏 解锁全文

1546

1546

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?