目录

前言

FIR 滤波器在数字信号处理领域发挥着重要的作用。本文就XILINX公司的 FIR IP核的使用作详细描述。

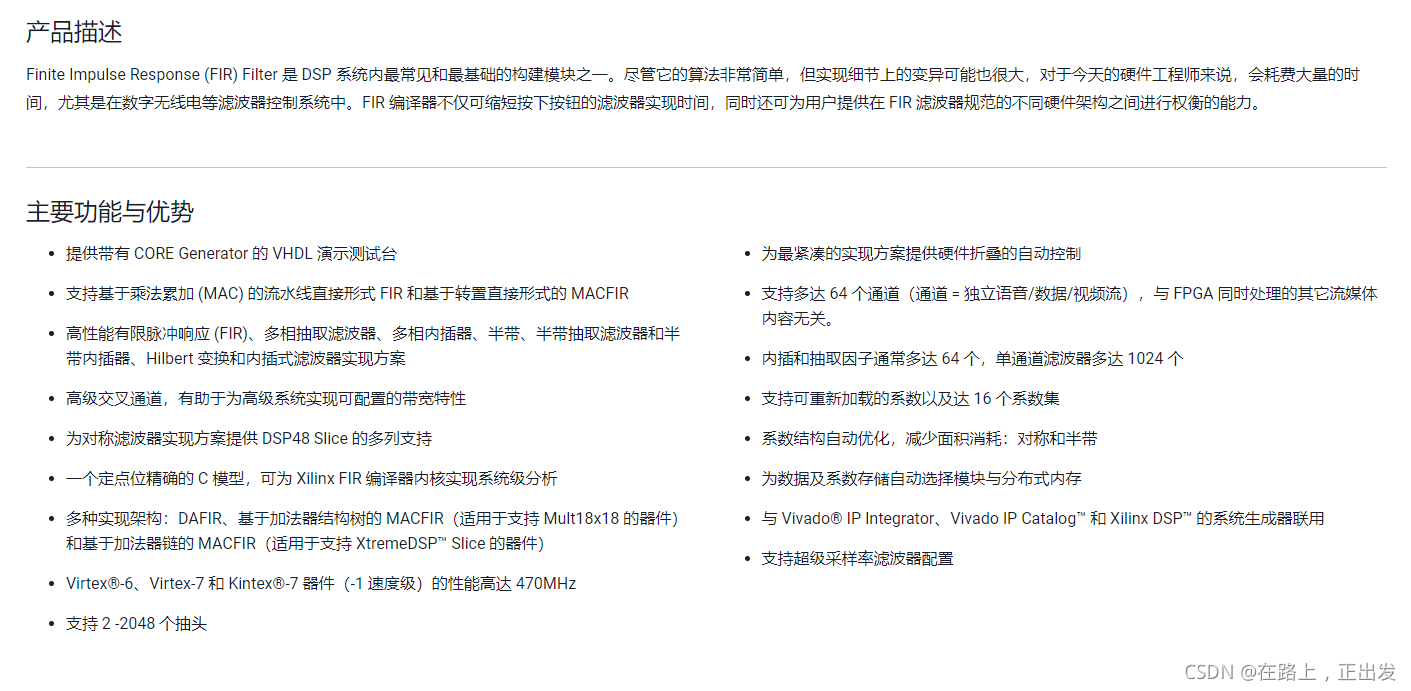

下面是XILINX官方的产品描述:

操作环境:Vivado IDE 2018.3

IP核版本:v7.2

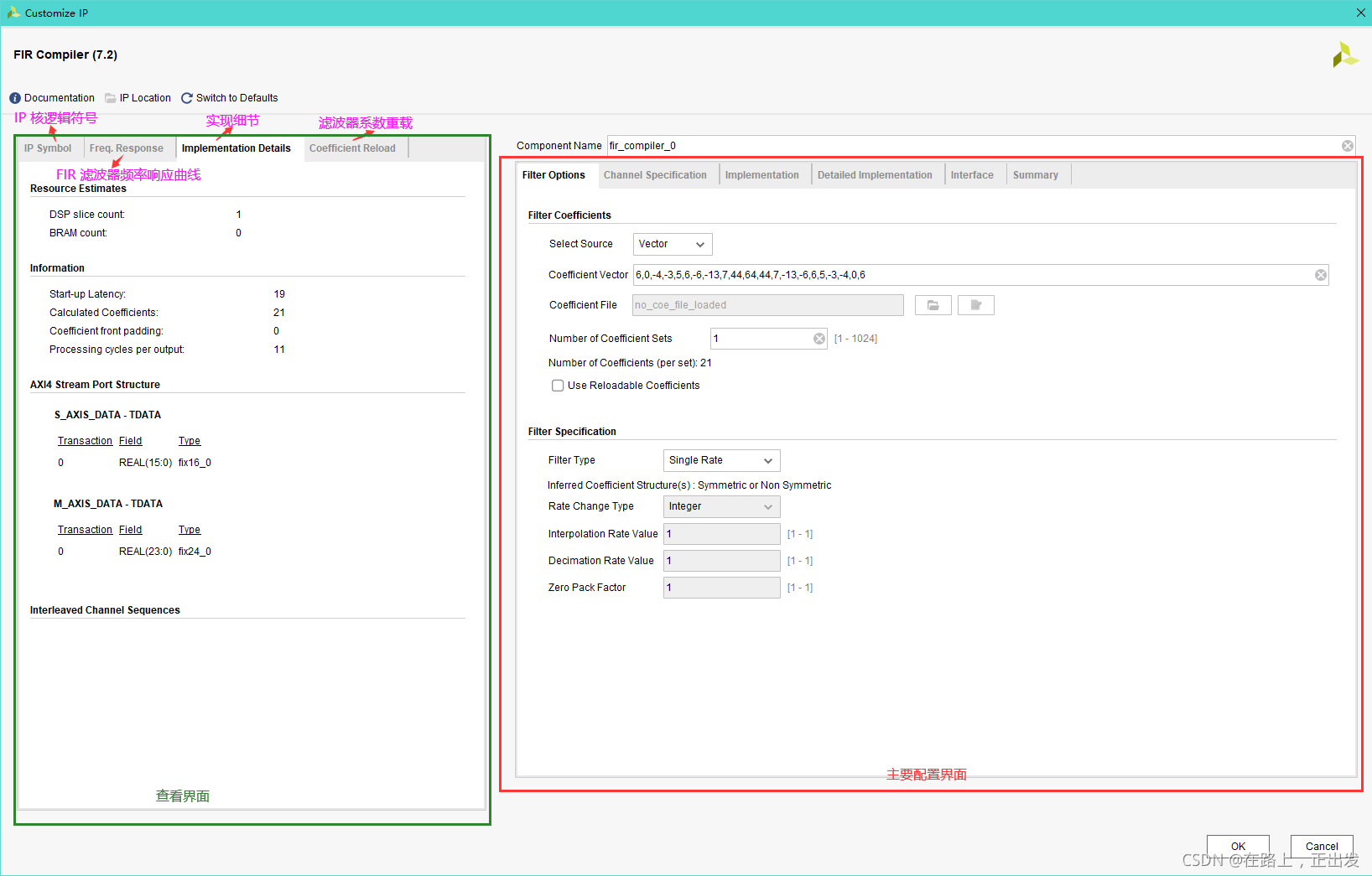

一、IP 核配置

1、总览

目录

FIR 滤波器在数字信号处理领域发挥着重要的作用。本文就XILINX公司的 FIR IP核的使用作详细描述。

下面是XILINX官方的产品描述:

操作环境:Vivado IDE 2018.3

IP核版本:v7.2

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?