虚拟机:VMware-workstation-full-14.0.0.24051

环 境:ubuntu 18.04.1

应用工具:VCS(verilog compiled simulator,编译型代码仿真器)

一、学习内容(1)

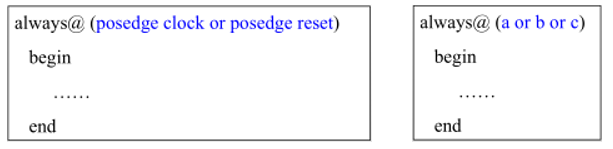

二、结构语句

- initial语句:只执行一次

- always语句:不断重复执行,直到仿真结束

- task语句:可在程序模块中的一处或多处调用

- function语句:可在程序模块中的一处或多处调用

(1)initial语句

initial begin

语句1;

...

语句n;

end

在仿真的初始状态对各变量进行初始化;在测试文件中生成激励波形作为电路的仿真信号。

【例1】

……

parameter size=16;

reg[3:0] addr;

reg reg1;

reg[7:0] memory[0:15];

initial begin

reg1 = 0;

for(addr=0;addr<size;addr=addr+1);

memory[addr]=0;

end

……

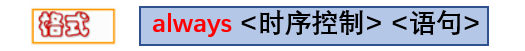

(2)always语句

如果always块中包含一个以上的语句,则这些语句必须放在begin_end或fork_join块中!

always @ (posedge clk or negedge clear) begin

if(!clear) qout = 0; //异步清零

else qout = 1;

end

always语句必须与一定的时序控制结合在一起才有用!如果没有时序控制,则易形成仿真死锁!

//生成一个0延迟的无限循环跳变过程——形成仿真死锁

always areg = ~areg;

//在tb文件中,用于生成一个无限延续的信号波形——时钟信号

‘define half_period 50

module half_clk_top;

reg reset, clk; // 输入信号

wire clk_out; // 输出信号

always #half_period clk = ~clk;

...

endmodule

【例2】用always块语句产生T’FF和8位二进制计数器

- always块语句模板

always @ (<敏感信号表达式>)begin

// 过程赋值语句

// if语句

// case语句

// while ,repeat ,for 循 环

// task ,function 调用

end

-

一个变量不能在多个always块中被赋值

-

敏感信号表达式又称事件表达式或敏感表,当其值改变时,则执行一遍块内语句;

-

在敏感信号表达式中应列出影响块内取值的所有信号!

-

敏感信号可以为单个信号,也可为多个信号,中间需用关键字or连接!

-

敏感信号不要为x或z,否则会阻挡进程!

-

always的时间控制可以为沿触发,也可为电平触发。

-

关键字posedge表示上升沿;negedge表示下降沿。

//模板1

always @ (Inputs) //所有输入信号必须列出,用or隔开

begin

...//组合逻辑关系

end

//模板2

always @ (Inputs) //所有输入信号必须列出,用or隔开

if (Enable) begin

...//锁存动作

end

//模板3

always @ (posedge Clock) // Clock only

begin

...// 同步动作

end

//模板4

always @ (posedge Clock or negedge Reset)

// Clock and Reset only

begin

if (! Reset) // 测试异步复位电平是否有效

..// 异步动作

else

...// 同步动作

end // 可产生触发器和组合逻辑

//模板5

always @ (posedge Clock or negedge Reset)

// Clock and Reset only

begin

if (! Reset) // 测试异步复位电平是否有效

..// 异步动作

else if

...// 同步动作

else if

...//同步动作

end // 可产生触发器和组合逻辑

通常采用异步清零!只有在时钟周期很小或清零信号为电平信号时(容易捕捉到清零信号)采用同步清零。

三、小结

作者:xlinxdu

版权:本文版权归作者所有

转载:未经作者允许,禁止转载,转载必须保留此段声明,必须在文章中给出原文连接。

1496

1496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?