# 一、前沿:在学习verilog中,写运行代码时,我们最常用的就是always;

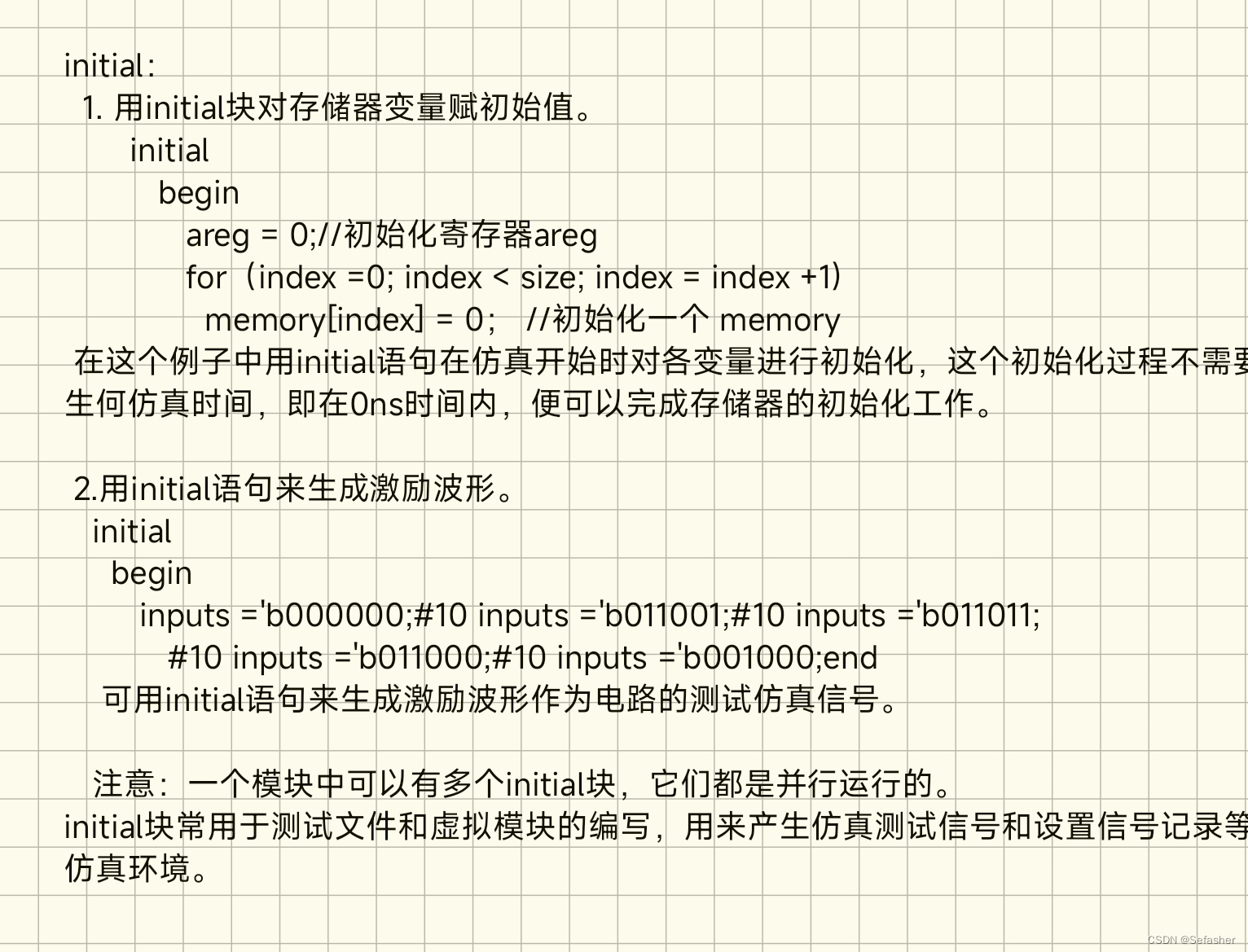

写测试激励文件代码,我们最常用的就是initial。

这也是二者的最最常用的功能之一。

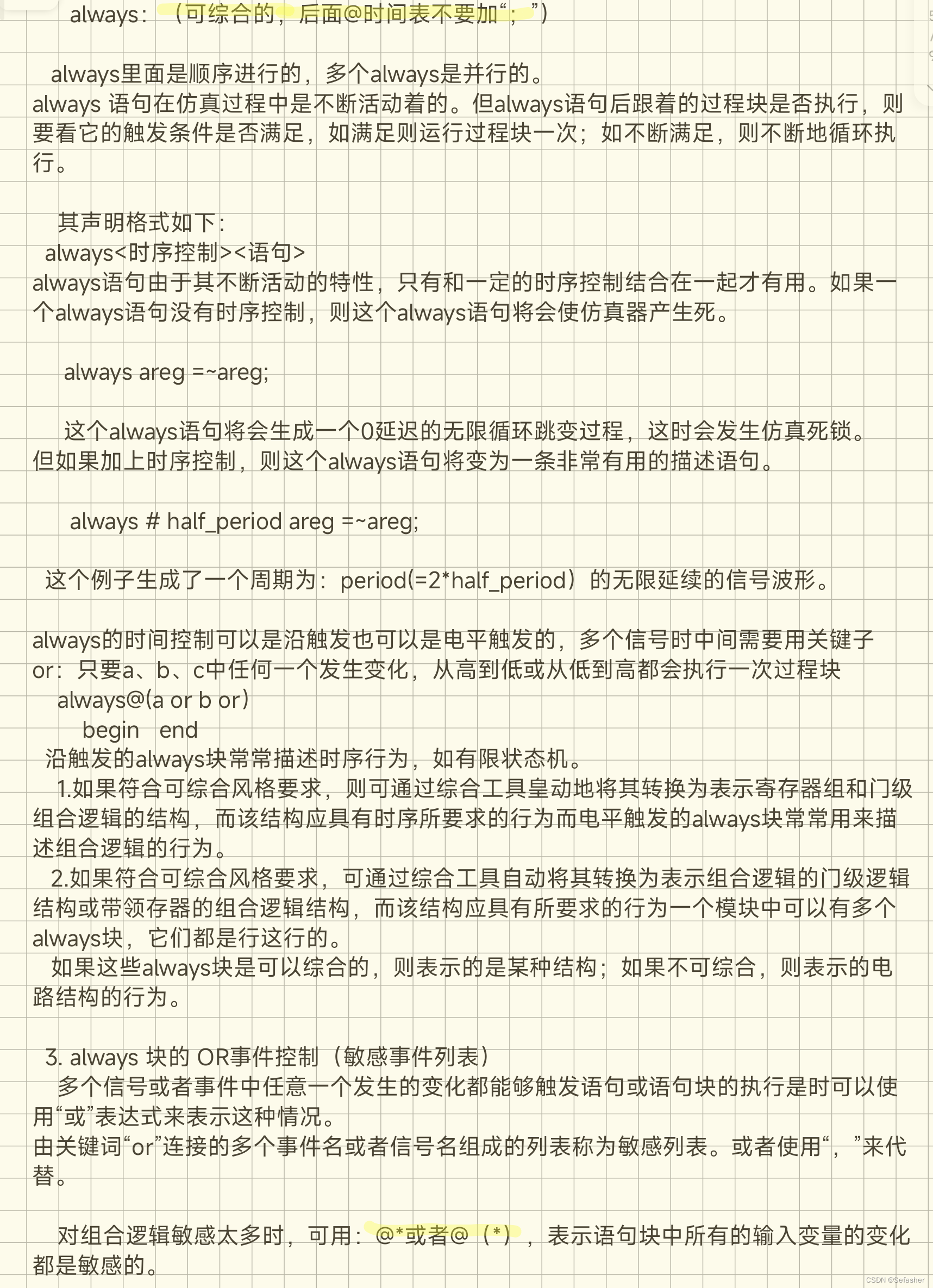

# 二、区别:他们两人最大的区别就是——运行次数:initial只能运行一次,而always可以运行很多次,只要有敏感事件表中的事件发生(时钟信号,边沿触发,电平触发等)它就可以运行。

(正因如此,因此也产生了相关的问题:

1. 没有终止的信号,使他它永远进行下去;

2. 产生锁存器:即不论新变化信号来与否,新信号是否变化,其运行姐结构不变。)

# 三、always:

# 四、initial

3856

3856

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?