1、这次做了CS450前三道,最后一道实在是看不懂。其实第三道题我就有一点看不懂了。。啥分支预测,啥狗屁啊,看着波形图还勉强能写的出来。

2、第四道题属于波形图看不懂,题目也看不懂,准备等学习一段事件之后再来看看。现在做也没有意义。

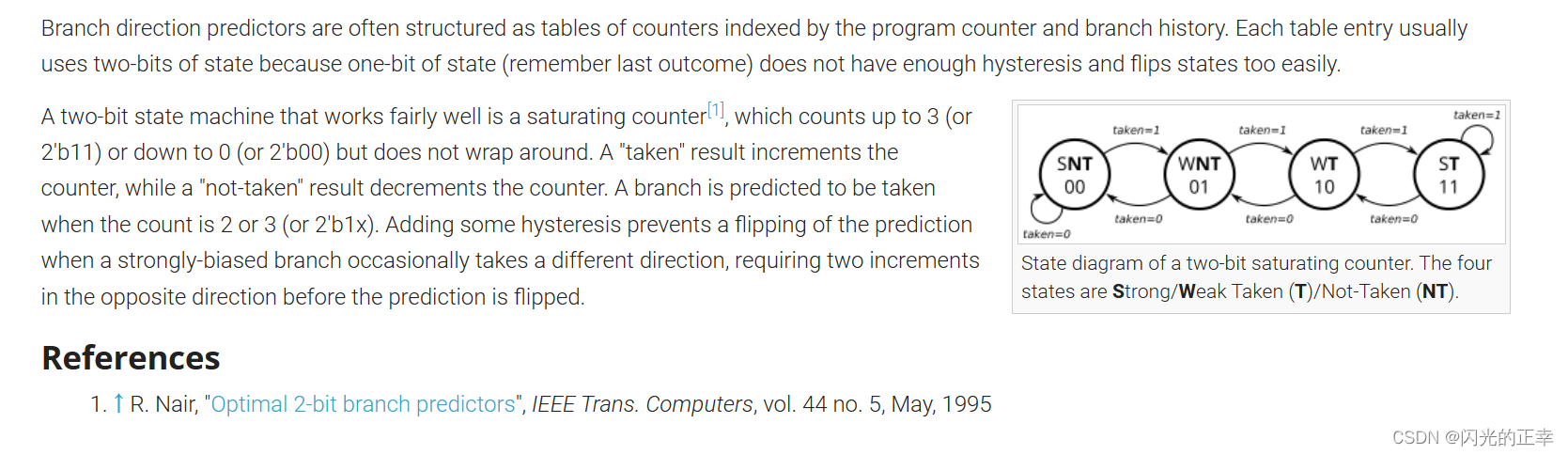

前三道完整代码如下:(counter那个写的太不完美了,看别人写的之后才发现自己写的一点也不优雅),第三道题目的理解,分析出来就不难了,我是根据答案的波形图写出来的,属于是逃课了。

完整代码如下:

1、Cs450/timer

module top_module(

input clk,

input load,

input [9:0] data,

output tc

);

reg [9:0]counter;

always@(posedge clk)begin

if(load)begin

counter<=data;

if(data==0)

tc<=1'b1;

else

tc<=1'b0;

end

else if(counter==0)begin

counter<=0;

end

else begin

counter<=counter-1'b1;

if(counter<=1)

tc<=1'b1;

else

tc<=1'b0;

end

end

endmodule

//简单的timer计数器

2、

module top_module(

input clk,

input areset,

input train_valid,

input train_taken,

output [1:0] state

);

always@(posedge clk or posedge areset)begin

if(areset)

state<=2'b01;

else begin

case({train_taken,train_valid})

2'b11:begin

if(state==2'b11)

state<=2'b11;

else

state<=state+1'b1;

end

2'b01:begin

if(state==2'b00)

state<=2'b00;

else

state<=state-1'b1;

end

default:state<=state;

endcase

end

end

endmodule

//简单的状态机,一段式就可以写完。

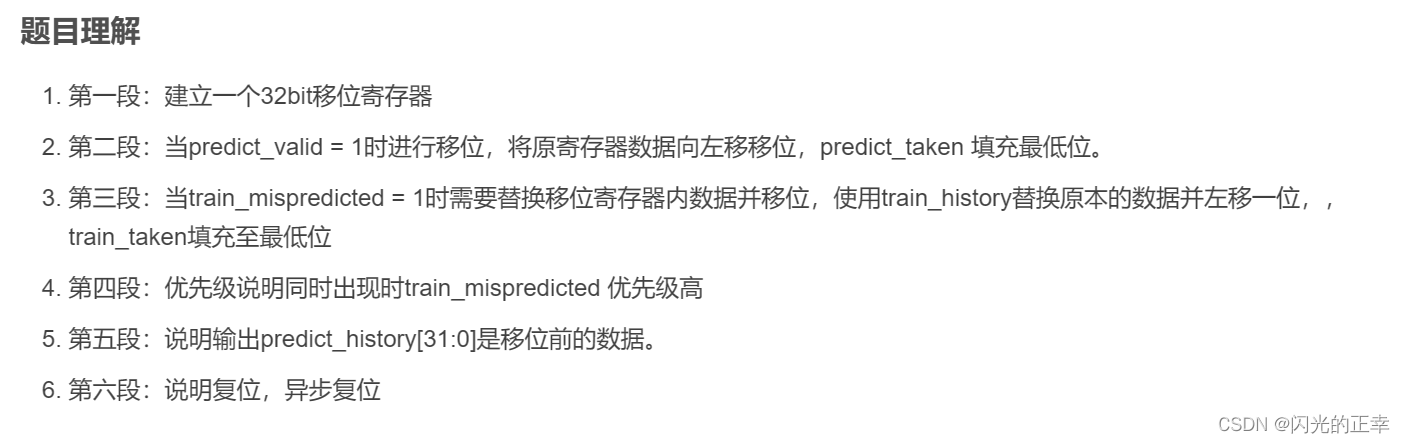

3、Cs450/history shift

module top_module(

input clk,

input areset,

input predict_valid,

input predict_taken,

output [31:0] predict_history,

input train_mispredicted,

input train_taken,

input [31:0] train_history

);

always@(posedge clk or posedge areset)begin

if(areset)

predict_history<=32'd0;

else begin

if(train_mispredicted==0)

case({predict_valid,predict_taken})

2'b11:begin

predict_history<=predict_history<<1;

predict_history[0]<=1;

end

2'b10:predict_history<=predict_history<<1;

default:predict_history<=predict_history;

endcase

else begin

if(train_taken)begin

predict_history<=train_history<<1;

predict_history[0]<=1;

end

else

predict_history<=train_history<<1;

end

end

end

endmodule

//虽然写出来了,但是相当于看着波形图写出来了,完全不知道啥意思啊。

547

547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?