上篇该系列博文中通过MDIO接口实现了PHY芯片的状态检测,验证其已处于1000M 全双工工作模式。在设计MAC逻辑之前,要先清楚MAC与PHY之间的接口以及以太网协议细节,这样才能保证网络的兼容性。本文内容多来自Xilinx官方文档pg051 tri-mode-eth-mac.

1.GMII接口

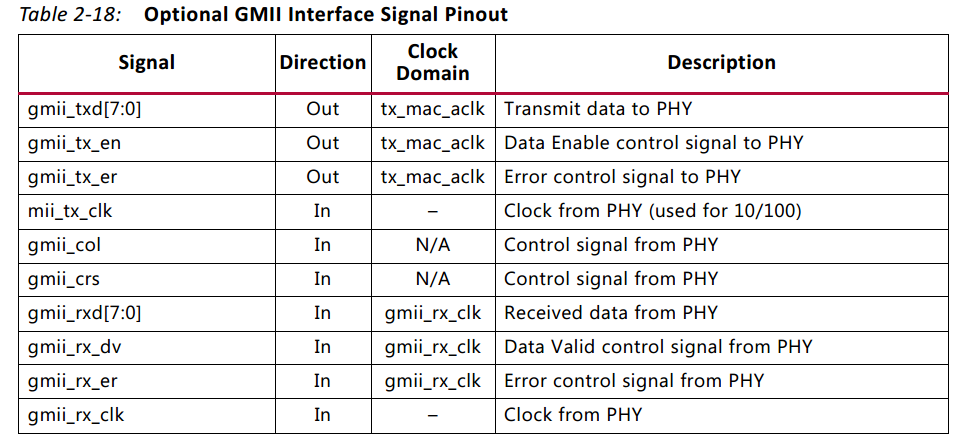

此处使用较简单的GMII接口,接口列表及说明如下:

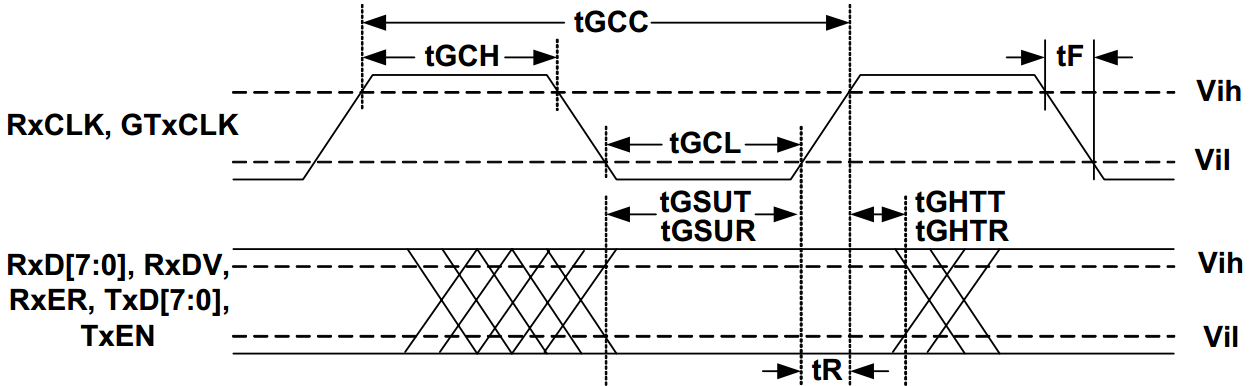

TX方向时钟tx_mac_aclk由FPGA给出,RX方向时钟gmii_rx_clk由PHY芯片经过内部CDR模块从接收数据中恢复出来,时钟频率均为125MHz。TX和RX方向基本均由三个信号组成:d en/dv er。查看开发板上使用的以太网PHY芯片RTL8211EG-VB datasheet中AC Characteristics:

数据在时钟上升沿采样,因此TX端可在时钟下降沿更新数据,RX端时钟上升沿接收数据即可。

2.以太网协议规范

MAC层的功能就是“成帧解帧”,接下来查看以太网数据帧结构和规则。

FPGA设计千兆以太网MAC(2)——以太网协议及设计规划

最新推荐文章于 2024-05-17 12:26:09 发布

订阅专栏 解锁全文

订阅专栏 解锁全文

308

308

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?