带宽是影响FPGA加速器的重要因素,因为大量的并行计算对数据量要求很大。如果加速器对数据的访问是不规则的,那么cache miss就会大大影响加速器性能。这篇来自FPGA2019会议的报告,向我们展示了如何来更好的处理cache miss问题,提高对缓存的利用率以及提高加速器效率。

01

Cache miss的问题

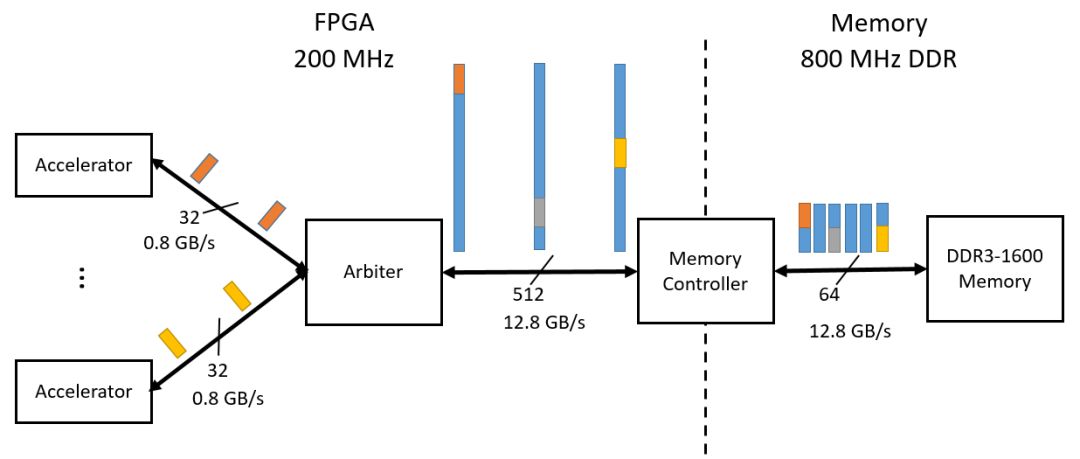

假设DDR可以提供12.8GB/s的带宽,FPGA上的并行加速器的数据输入带宽为0.8GB/s,可以并列16个这种加速器。这些加速器通过arbiter来直接访问DDR。如果它们访问的数据是连续规则的,那么DDR的带宽可以被充分利用。但是这些加速器需要的数据在DDR中并不是规则排列的,如图1.1。这样就会造成频繁的访问DDR,这样DDR的带宽就不够用,造成的结果就是加速器会受到延迟,效率无法得到提升。就如同图1.1所示,实际上有效利用的DDR带宽只有0.8GB/s。

图1.1 不规则数据需要造成频繁访问DDR

一种解决问题的方法是使用blocking cache&

一文告诉你怎么解决cache miss的问题

最新推荐文章于 2025-03-11 14:27:53 发布

本文探讨了在FPGA加速器中如何处理cache miss问题,介绍了传统的non-blocking cache结构及其缺点,并提出通过Cuckoo hashing算法和动态可扩展subentries来改进,以提高带宽利用率和加速器效率。

本文探讨了在FPGA加速器中如何处理cache miss问题,介绍了传统的non-blocking cache结构及其缺点,并提出通过Cuckoo hashing算法和动态可扩展subentries来改进,以提高带宽利用率和加速器效率。

订阅专栏 解锁全文

订阅专栏 解锁全文

726

726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?