第3章 FPGA实现数字信号处理基础

FPGA中数的表示

FPGA中数的运算

有限字长效应

FPGA中的常用处理模块

数字信号是指时间和幅度均是离散的信号,时间离散是指信号在时间上的不连续性,且通常是等间隔的信号;幅度离散是指信号的幅度值只能取某个区间上的有限值,而不能取区间上的任意值。当使用计算机或专用硬件处理时域离散信号时,因受寄存器或字长限制,这时的信号实际上就是数字信号。物理世界上的原始信号大多是模拟信号,在进行数字信号处理之前需要将模拟信号数字化,数字化的过程中会带来误差。

本章将对数的表示及运算、有限字长效应等内容展开讨论。与DSP、CPU不同,FPGA没有专用的CPU或运算处理单元,程序运行的过程其实是庞大电路的工作过程,几乎每个加、减、乘、除等操作都需要相应的硬件资源来完成。XILINX公司的FPGA开发套件ISE提供了丰富且性能优良的常用运算模块及其他专用知识产权(IP)核,熟练掌握并应用这些IP不仅可以提高设计效率,还可以有效提高系统的性能。本章将详细介绍几种最常用的运算处理模块,并在后续章节中使用这些模块进行设计。

3.1FPGA 中数的表示

3.1.1 莱布尼兹与二进制

在德国图灵根著名的郭塔王宫图书馆(SchlossbiliothkezuGotha)保存着一份弥足珍贵的手稿,其标题为:“1与0,一切数字的神奇渊源,这是造物主的秘密美妙的典范。因为一切无非都来自上帝。”这是德国通才大师莱布尼兹(Gottfried Wilhelm Leibniz,见图 3-1)的手迹。但是,关于这个神奇美妙的数字系统,莱布尼兹只有几页异常精炼的描述。用现代人熟悉的表达方式,我们可以对二进制做如下的解释:

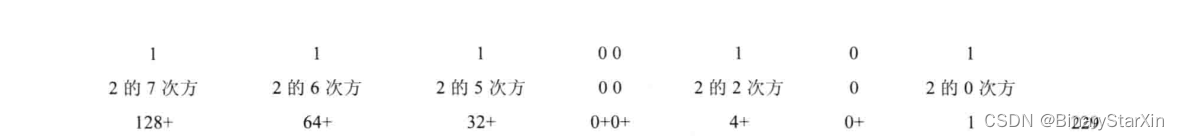

以此类推,把等号右边的数字相加,就可以获得任意一个自然数,或者说任意一个自然数均可以采用这种方式进行分解。我们只需要说明的是采用了2的几次方,而舍掉了2的几次方。二进制的表述序列都从右边开始,第一位是2的0次方,第二位是2的1次方,第三位是2的2次方,以此类推。一切采用2的乘方的位置,我们就用“1”来标志;一切舍掉2的乘方的位置,我们就用“0”来标志。例如,对于序列“11100101”,根据上述表示方法,可以很容易推算出序列所表示的数值。

在这个例子中,十进制的数字“229”就可以表述为二进制的“11100101”。任何一个二进制数字最左边的一位都是“1”。通过这个方法,用1到9和0这十个数字表述的整个自然数列都可用“0”和“1”这两个数字来代替。“0”与“1”这两个数字很容易被电子化:有电流就是“1”,没有电流就是“0”。这就是整个现代计算机技术的根本秘密所在。

1679年,莱布尼兹写了题为“二进制算术”的论文,对二进制进行了充分的讨论,并建立了二进制的表示及运算。随着电子计算机的广泛应用,二进制进一步大显身手。因为电子计算机是用电子元件的不同状态来表示不同的数码,如果要用十进制就要求元件能准确地变化出十种状态,这在技术上是非常难实现的。二进制只有两个数码,只需两种状态就能实现,这正如一个开关只有“开”和“关”两种状态。如果用“开”表示“0”,“关”表示“1”,那么一个开关的两种状态就可以表示一个二进制的数。由此我们不难想象,五个开关就可以表示五个二进制的数,这样运算起来就非常方便。

3.1.2 定点数表示

1.定点数的定义

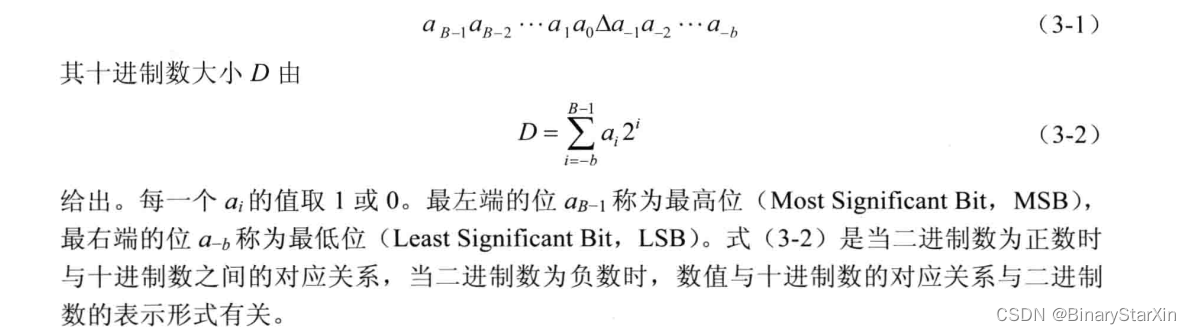

几乎所有的数字计算机,包括FPGA在内的数字信号处理器件,数字和信号变量都是用二进制来表示的。数字使用符号“0”和“1”来表示,称为比特(Binary Digit,bit)。其中,二进制小数点将数字的整数和小数部分分开。为了与十进制小数点相区别,使用三角符号“A”来表示二进制的小数点位置。例如,十进制 11.625 的二进制表示为“1011A101”二进制小数点左边的四位“1011”形成整数部分,小数点右边的三位“101”代表数字的小数部分。对于任意一个二进制数来讲,均可由B个整数位和b个小数位组成,如式(3-1)所示:

表示一个数的一组数字称为字,而一个字包含位的数目称为字长。字长的典型值是个为2的幂次方的正整数,如8、16、32等。字的大小通常用字节(Byte)来表示,一个字节有8个比特。

2.定点数的三种形式

定点数有三种表示形式:原码、反码及补码。这3种表示方法在FPGA设计中使用十分普遍,下面分别进行讨论。

(1)原码表示法。原码表示法是指符号位加绝对值的表示法。符号位通常用0表示正号,用1表示负号。例如,二进制数(x)2=0Δ110表示的是+0.75;(x)2=1Δ110表示的是-0.75。如果已知原码各位的值,则它代表的十进制可表示为

B-2D =(-1)°в-i=-b

(3-3)

(2)反码表示法。正数的反码与原码相同。负数的反码表示方法也十分简单,将原码除符号位的所有位取反,即得到负数的反码。例如,十进制数-0.75的二进制原码表示为(x)2=1Δ110,其反码为1A001。

(3)补码表示法。正数的补码、反码及原码完全相同。负数的补码与反码之间有一个简单的换算关系:补码等于反码在最低位加1。例如,十进制数-0.75的二进制原码表示为(x)2==1A110,反码为1001,其补码为1010。值得一提的是,如果将二进制数的符号位定在最右边,即二进制数表示整数,则负数的补码与负数绝对值之间也有一个简单的运算关系:补码当做正整数,补码的整数值+原码绝对值的整数值=2。还是上面相同的例子,十进制数-0.75 的二进制原码表示为(x)2==1A110,反码为1001,其补码为1010。补码1010的符号位定在最末位,且当做正整数1010,十进制数为10,原码1110的符号位定在最末位,且取绝对值的整数 0110,十进数为6,则10+6=16=2。在二进制运算过程中,补码最重要的特性是可以将减法用加法运算的规则实现。

原码的优点是乘除运算方便,不论正负数,乘除运算都一样,并以符号位决定结果的正负号;若做加法则需要判断两个数符号是否相同;若做减法,还需要判断两个数绝对值的大小,而后用大数减小数。补码的优点是加减法运算方便,不论正负数均可直接相加,且符号位同样参与运算。

3.1.3 浮点数表示

1.浮点数的定义及标准

浮点数是属于有理数中某特定子集的数的数字表示,在计算机中用来近似表示任意某个实数。具体地说,这个实数由一个整数或定点数(即尾数)乘以某个基数的整数次幂得到,这种表示方法类似于基数为10的科学记数法。一个浮点数A由两个数m和e来表示,即 A=mx6。在任意一个这样的数字表示系统中我们需要确定两个参数:基数b(记数系统的基)和精度B(使用多少位来存储)。m(即尾数)是B位二进制数,如±dAddd…ddd。如果m的第一位是非0整数,m称做规格化后的数据。一些数据格式使用一个单独的符号位s(代表“+”或者“-”)来表示正负,这样m必须是正的。e在浮点数据中表示基的指数。采用这种表示方法,可以在某个固定长度的存储空间内表示定点数无法表示的更大范围的数。此外,浮点数表示法通常还包括一些特别的数值:+∞和-∞(正负无穷大),以及NaN(NotaNumber)等。“无穷大”用于数太大而无法表示的时候,NaN 则指示非法操作或者出现一些无法定义的结果。大部份计算机采用二进制(b=2)的表示方法。位(bit)是衡量浮点数所需存储空间的单位,通常为32位或64位,分别叫做单精度和双精度。一些计算机提供更大的浮点数,例如,Intel公司的浮点运算单元Intel8087协处理器(以及集成了该协处理器的其他产品)提供80位长的浮点数,这种长度的浮点数通常用于存储浮点运算的中间结果。还有一些系统提供128位的浮点数(通常用软件实现)。

在IEEE754标准之前,业界并没有一个统一的浮点数标准。很多计算机制造商都设计自己的浮点数规则以及运算细节。那时,实现的速度和简易性比数字的精确性更受重视。这种情况给代码的可移植性造成了不小的困难。直到1985年,Intel打算为它的8086微处理器引进一种浮点数协处理器的时候,聘请了加州大学伯克利分校的最优秀的数值分析家之William Kahan教授,来为8087FPU 设计浮点数格式。WilliamKahan又找来两个专家来协助他,于是就有了KCS 组合(Kahn,Coonan and Stone),并共同完成了Intel的浮点数格式设计。

Intel的 KCS 浮点数格式完成得如此出色,以至于IEEE决定采用一个非常接近KCS的方案作为IEEE的标准浮点格式。IEEE于1985年制订了二进制浮点运算标准(BinaryFloating-Point Arithmetic)IEEE 754,该标准限定指数的底为2,同年被美国引用为ANSI标准。目前,几乎所有计算机都支持该标准,大大改善了科学应用程序的可移植性。考虑到IBM System/370的影响,IEEE于1987年推出了与底数无关的二进制浮点运算标准IEEE 854,同年该标准也被美国引用为ANSI标准。1989年,国际标准组织IEC批准JEEE754/854为国际标准IEC559:1989。后来经修订,标准号改为EC60559。现在,几乎所有的浮点处理器完全或基本支持IEC60559。

2.单精度浮点数据格式

IEEE 754标准定义了浮点数的存储格式,包括部分特殊值的表示(无穷大和NaN);同时给出了对这些数值进行浮点操作的规定。它也制定了4种取整模式和5种例外(Exception),包括何时会产生例外,以及具体的处理方法。

在IEEE754中规定了4种浮点数的表示格式:单精度(32位浮点数)、双精度(64位浮点数)、单精度扩展(>43位,不常用)、双精度扩展(>79位,通常采用80位进行实现)。事实上,很多计算机语言都遵从了这个标准,包括可选部分。例如,C语言在IEEE 754发布之前就已存在,现在它能完美支持IEEE754标准的单精度和双精度运算,虽然它早已有另外的浮点实现方式。

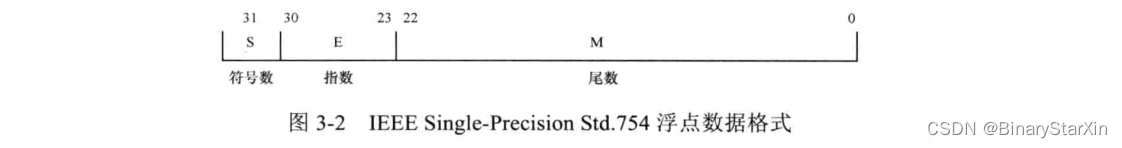

单精度(IEEESingle-Precision Std.754)浮点数据格式如图 3-2所示。

符号位S(Sign)占1bit,0代表正号,1代表负号;指数位E(Exponent)占8bit,E的取值范围为0~255(无符号整数),实际数值e-E-127,有时E也称为“移码”,或不恰当地称为“阶码”(阶码实际应为e);尾数位M(Mantissa)占23bit,M也叫做有效数字位(Significant)、系数位(Coefficient),甚至被称做“小数”。在一般情况下,m=(1.M)2,使得实际的作用范围为1≤尾数<2。为了对溢出进行处理,以及扩展对接近0的极小数值的处理能力,IEEE754对M做了一些额外规定。

(1)0值:以指数E、尾数M全零来表示0值。当指数位S变化时,实际存在“正0”和“负0”两个内部表示,其值认为都等于0。

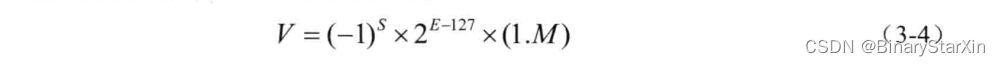

(2)E=255、M=0时,用做无穷大(或Infinity、∞)。根据符号不同,又有+∞、一00。NaN:E=255、M不为0时,用做NaN(NotaNumber,“不是数”之意)。浮点数所表示的具体值可用下面的通式表示

式中,尾数(1.M)中的“1”为隐藏位。

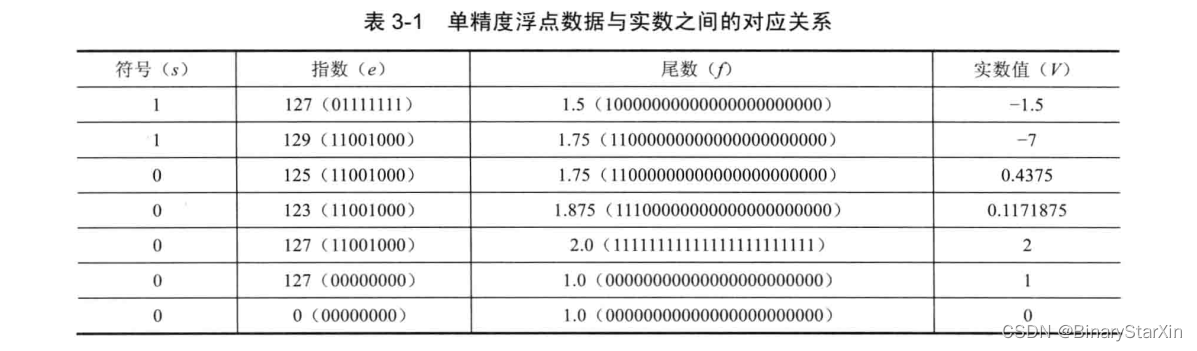

还需要特别注意的是,虽然浮点数的表示范围及精度与定点数相比有很大的改善,但因为浮点数毕竟也是以有限的 32bit长度来反映无限的实数集合,因此大多数情况下都是一个近似值。表3-1是几个浮点格式数据与实数之间的对应关系表。

3.一种适合 FPGA 处理的浮点数据格式

与定点数相比,浮点数据虽然可以表示更大范围、更高精度的实数,然而在FPGA器件中实现时却需要占用成倍的硬件资源。例如,加法运算,两个定点数据直接相加即可,浮点的加法却需要更为繁杂的运算步骤。

对阶操作:比较指数大小,对指数小的操作数的尾数做移位,完成尾数的对阶操作。尾数相加:对对阶后的尾数进行加(减)操作。

规格化:规格化有效位并且根据移位的方向和位数修改最终的阶码。这一系列操作不仅需成倍地消耗FPGA内部的硬件资源,也会成倍地降低系统的运算速度。对于浮点数乘法操作来说,一般需要以下的操作步骤。

指数相加:完成两个操作数的指数相加运算。

尾数调整:将尾数f调整为1.f的补码格式。

尾数相乘:完成两个操作数的尾数相乘运算。

规格化:根据尾数运算结果调整指数位,并对尾数进行舍入截位操作,规格化输出结果。

浮点乘法器的运算速度主要由FPGA内部集成的硬件乘法器决定。如果将24位的尾数修改为18位的尾数,则可在尽量保证运算精度的前提下最大限度地提高浮点乘法运算的速度,同时也可大量减少所需的乘法器资源(XILINX公司的大部分FPGA 芯片内部的乘法器核均为18bitx18bit。2个24bit数的乘法操作需要占用4个18bitx18bit的硬核乘法器,2个18bit数的乘法操作只需占用1个18bitx18bit的硬核乘法器)。IEEE标准中尾数设置的隐藏位主要是考虑节约寄存器资源,而FPGA内部具有丰富的存器资源,如直接将尾数表示成18bit的补码格式,则可去除尾数调整的运算,也可以减少一级流水线操作。

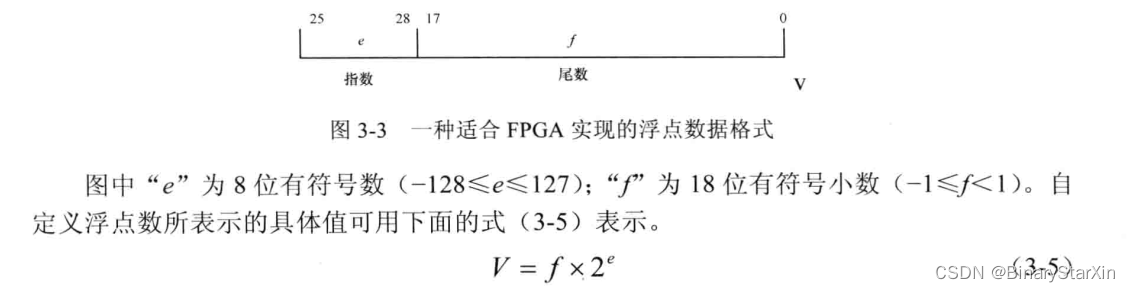

文献[19]根据FPGA内部的结构特点定义了一种新的浮点数据格式,如图3-3所示。

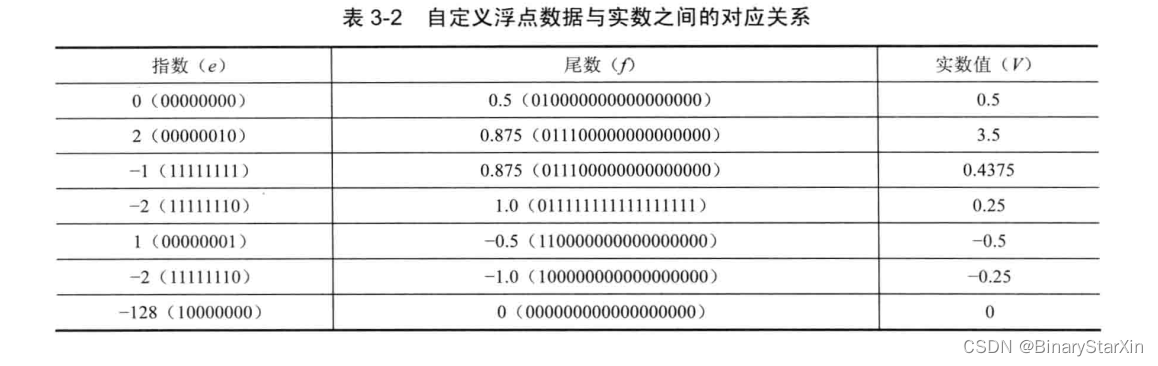

为便于数据规格化输出及运算,规定数值“1”的表示方法为指数为“0”,尾数为“1”数值“0”的表示方法为指数为“-128”,尾数为“0”。这种浮点数据格式与单精度格式的区别在于:自定义格式将原来的符号位与尾数位合并成18bit的补码格式定点小数,表示精度有所下降,却可大大节约乘法器资源(由4个18bitx18bit乘法器减少到1个),从而达到有效减少运算步骤并提高运算速度(由二级18bitx18bit乘法运算减少到一级运算)的目的。表3-2是几个自定义浮点格式数据与实数之间的对应关系表。

547

547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?