一、概述

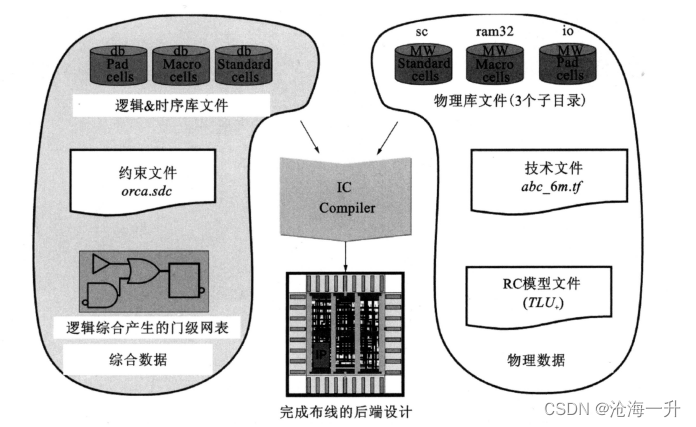

ICC数据设置的文件关系框图如图:

后端工具在数据设置阶段需要对两大类数据进行设置,包括从前端设计继承的综合数据 以及后端设计需要的物理数据。

- 综合数据主要包括前端逻辑综合已经设置过的逻辑与时序库文件、设计约束文件sdc以 及综合网表文件。

- 物理数据主要包括标准单元、内存RAM等IPJO管脚三类物理库文件,工艺和设计规则 检查相关的技术文件tf以及建模信号互连线延迟的RC模型的TLU+文件。

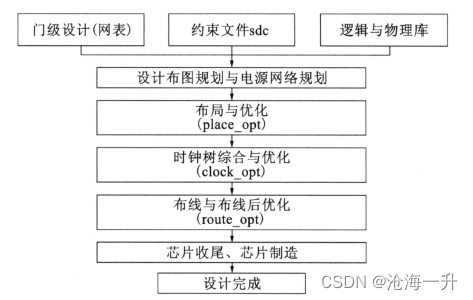

如下图所示为ICC数字芯片后端设计主要步骤流程图。图中第一层准备的三部分数据,分别是综合映射的门级设计(网表)、约束文件sdc、逻辑与物理库文件。本文讲述的就是第一 层数据设置阶段。

二、逻辑库设置

逻辑库提供:标准单元(与非门、或非门、异或门、寄存器等)的时序和功能信息;提供宏块 (RAM、ROM、IP如处理器核心等)的时序信息;定义驱动和负载的设计规则(design rule),如最大/最小扇出Max/Min fanout、最大/最小电容负载Max/Min capacitance、最大/最小信号转换时延Max/Min transitiono。通常,逻辑库与前端综合工具Design Compiler(DC)中的设置相同,通过目标库target library与链接库link library变量指定。

1、读入门级网表

ICC可以打开Milkyway数据库,读入由DC创建的门级设计文件,读入文件类型包括: ddc、Verilog、VHDL等,其中ddc文件可包含设计属性信息。ICC可一次读入多个设计文件, 读入设计文件(门级网表)的命令具体如下:

read_ddc #读入ddc

read_verilog #读入.v文件

read_vhdl #读入.vhd文件

read_verilog filel.v file2.v … #读入多个文件2、多次实例化设计调整

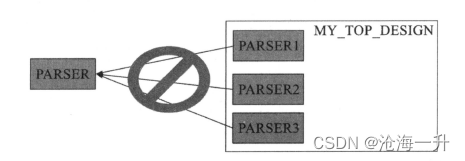

IC Compiler不支持有多个实例(non-uniquified)的设计。如下图中的顶层设计中实例化3个PARSER模块是不允许的。

对于包含多个实例的设计,ICC脚本命令需要使用current_ design命令,该命令指定了当前的顶层设计名称,并执行uniquify命令,实现实例唯一化,即对参考设计实例化模块的 唯一拷贝。

current_design MY_TOP_DESIGN

uniquify

对比uniquify操作之前、之后,会发现被多次调用的模块的模块名自动添加后缀名,实现 各个模块的唯一实例化。例如被3次实例化的PARSER的模块名通过uniquify命令自动改为PARSER_1、PARSER_2、PARSER_3。uniquify命令对于前端以及后端设计的意义在于允许ICC对相同的实例根据各自情况(输入驱动、输出负载、输入和输出信号的时序要求)独立优化逻辑,改进设计结果。

3、逻辑库设置

这里可以参考DC的设置,

lappend search_path ./design_data ./scripts MYMMW_libs #搜索路径

lappend search_path [glob MYMMW_libs/* /LM]

set link_library H* gates_max.db io_max.db rams_max.db" #链接库

set target_library "gates_max.db" #目标库

set symbol_library gates.sdb io.sdb rams.sdbn #符号库

三、物理库设置

1、物理参考库

物理参考库(physical reference libraries)用于物理设计的数据库设置。

物理参考库包含标准单元、宏块、管脚的布局布线的必要信息。icc的物理参考库采用的是Milkyway参考库格式,库文件夹以mw为后缀名。物理参考库提供的信息包括:

- 定义布局的单元块(tile);

- 标准单元布局行的行高;

- 标准单元最小宽度单位(即单元块的宽度);

- 布线方向;

- 布线轨道(track)的间距。

物理参考库设置命令采用创建设计库命令create_mw_lib,并选项 -mw_reference_library指定设计的物理参考库。

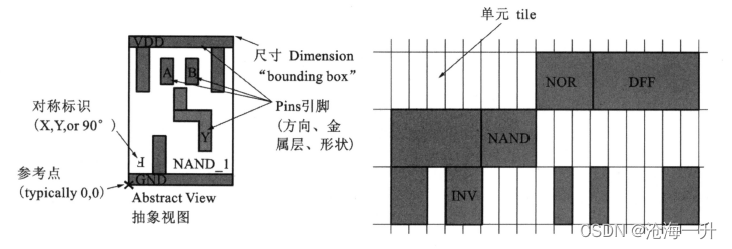

create_mw_lib -mw_reference_library ...如下图所示,物理库包含了芯片加工和底层设计需要的标准单元、宏块IP以及IO管脚的物理信息。具体包括单元的尺寸、引脚位置、参考点、方向等。

上图中符号F作为对称标识,指示单元是否旋转或水平/垂直镜像。布局的标准单元与单元块(tile)的关系如上图图右所示。所有标准单元cell都是tile的面积整数倍,任意一个单元都可以由一个或多个tile 横向拼接而成。tile与标准单元保持相同高度,即标准单元行高。但标准单元的宽度为tile宽度的整数倍。基于单元tile的标准单元版图设计图设计简化了布局排列规则,便于EDA工具建模和电路实现。

物理参考库的信息被保存在Milkyway数据库中,主要包括以下三种视图:

- CEL:完全的版图视图;

- FRAM:布局布线中使用的抽象视图,在布局布线中使用。FRAM包含的信息是CEL 的一部分,占用更少存储空间;

- LM带时序和功耗信息的逻辑模型(LM库为可选设置)。

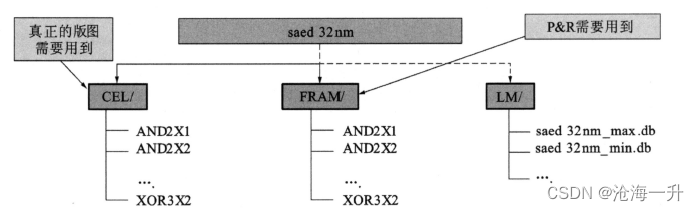

如下图所示为saed 32nm物理参考库文件层次结构,包含三个子文件夹内容。该参考库文件层次结构显示的是后端参考库的标准单元子库。复杂的后端工艺库针对不同的工艺角(corner)和不同工作模式(mode)独立建立后端参考库的LM db库文件,以反映不同工作条件下的时序等信息。

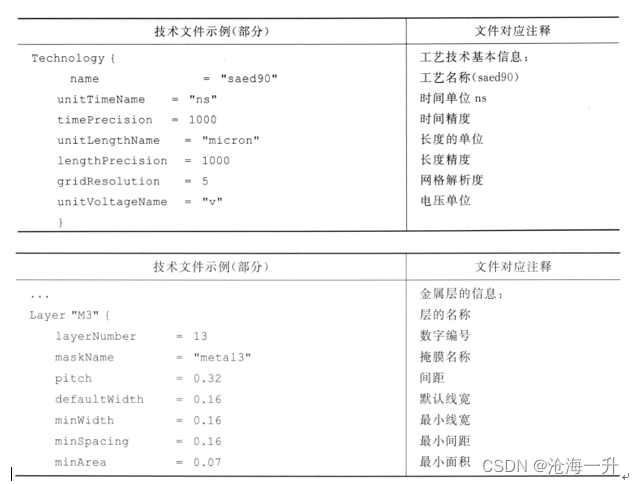

2、技术文件的格式与功能

技术文件简称tf文件(后缀名为.tf)o对于每一种工艺(如IBMO .13um、TSMC 90nm)都 需要单独定义tf文件。tf文件包含金属层的参数,具体包括:

- 每一金属层/过孔层的编号和名称定义;

- 每一金属层/过孔层的设计规则(包括最小线宽、线与线间距等);

- 层/过孔的物理和电气特性;

- 电阻的介电常数;

- 电气参数的单位与精度;

- 每一层/过孔显示的颜色与图案;

- 可能包含参数提取的电容模型等。

tf文件示例如下:

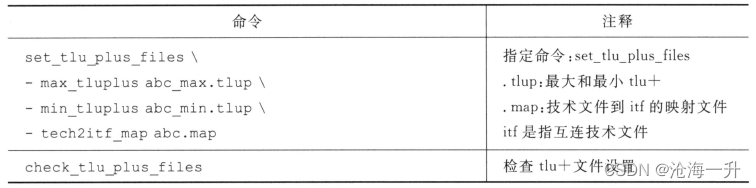

3、指定tlu+文件

tlu+(tlu plus)文件为寄生RC模型文件。从布局到布线的各个环节都需要参考tlu+文件提供的RC数据,计算信号线的时间延迟。

Cell单元延时由输入信号电平转换时间(transition)和门的输出负载(负载电容之和,包括线网电容Cnet和与线网连接的驱动单元的管脚电容Cpin)决定。

线网时延由线网的寄生阻抗Rnet和线网连接负载电容Cnet决定。

线网和单元的时延分开计算,ICC需要知道线网 的寄生阻抗和电容值。

tlu+模型通过线网的几何信息和文件存储的查找表计算线网的C和R值。

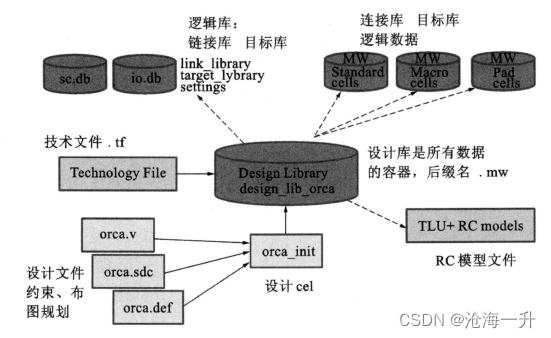

4、创建设计库

create_mw_lib命令创建设计库,设计库是设计的容器,后缀名为mw。物理参考库与技术文件是在创建Milkyway设计库时指定。创建设计库举例如下:创建设计库,指定技术文件 和物理参考库,创建完成后打开库。打开设计库的过程类似于其他设计软件打开一个新建的 工程。

create_mw_lib design_lib_orca -open \ #创建设计库design_lib_orca并打开

-technology abc_6m.tf \ #指定技术文件

-mw_reference_library "sc ram32 io" #指定mw参考库,即物理库

# sc:标准单元库,io管脚库,ram32存储器库

set_check_library_options -all #设置检查库设置为全部检查

check_library #检查库

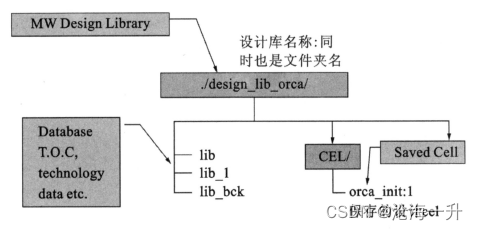

这里需要说明的是设计库、设计单元、参考库和输入文件关系,如下图:

Milkyway设计库的UNIX /Linux文件结构如下图。图中的lib、lib_1、lib_bak等文件中存储了内容列表(T.O.C)、导入的技术文件、指向参考库的指针等。

新创建的设计库中不包含设计单元,因此在执行create_mw_lib命令后, 只能看到在当前工作路径下创建了与设计库同名的文件夹,其中包含lib、lib_1、lib_bak等文 件,但不包含CEL文件夹。执行输入v格式或者ddc格式的设计后,将自动创建CEL文件 夹,并在CEL中保存与设计顶层模块同名的设计单元,如orca_init:1。

save_mw_cel命令保存CEL视图。单元名称中的冒号(:)和数字后缀表示单元保存的文件编号。设计单元在设计库中保存后,在CEL文件夹中可能存储多个单元名称相同,但冒号后数字编号不同的设计文件,这些数字编号不同的文件共同构成了设计单元。

5、保存和导入设计

在导入ddc或者v文件格式的设计后,当设置完成后,保存Milkyway设计的命令为save_mw_cel,举例如下:

save_mw_cel -as xxx选项-as设置保存单元名称。关键设计阶段后建议保存设计单元,以便后期设计工作有问题时打开前期设计结果,重复前面阶段的设计工作。注意保存单元后,当前ICC 打开的设计还是保存前的设计单元。

默认链接库link_library、搜索路径search_path、目标路径target_library和TLU +设置 保存在设计CEL中。如果库文件更新或者保存位置发生变化,这些设置需要重新加载。如果重新打开CEL,默认保存的设置不会重新加载,除非先进行以下设置(自动重置cel 的lib设置):

set auto_restore_mw_cel_lib_setup true

open_mw_cel xxx

四、检查及其他操作

1、检查库正确加载

完成逻辑库和物理库设置后,使用check_library命令检查库的不一致性,例如在逻辑库和物理库之间的cell单元和管脚差异、物理库内缺少CEL和FRAM视图以及多个参考库中有重复单元等。

set_check_library_options -all # 设置检查库选项打开

check_library #检查库命令

check_tlu_plus——files # tlu+ 文件检查单独完成

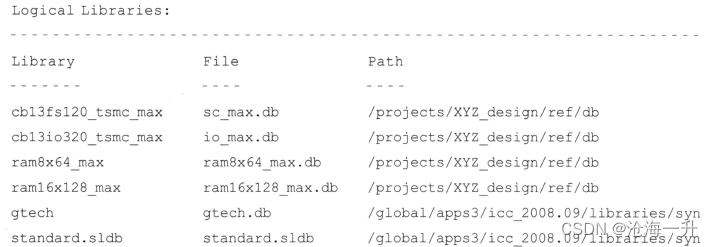

使用list_libs命令,列出所有逻辑库文件的名称、文件、路径,便于核对。在读入网表和完成链接后,才能使用list_libs命令。list_libs显示信息的示例如下:

2、定义逻辑电源与地信号连接

采用derive_pg_connection命令,定义电源和地网络P/G名称,定义单元的电源管脚和地管脚名称,并将各个单元的电源引脚和地引脚连接到P/G网络。采用derive_pg_connection 命令,把单元的固定连接高、低电平的管脚用-tie选项控制连接到电源网络VDD、VSS。采 用check_mv_design命令和-power_nets,检查设计的电源网络。

derive_pg_connection -power_net VDD -power_pin VDD -ground_net VSS -ground_pin VSS

derive_pg_connection -power_net VDD -ground_net VSS -tie

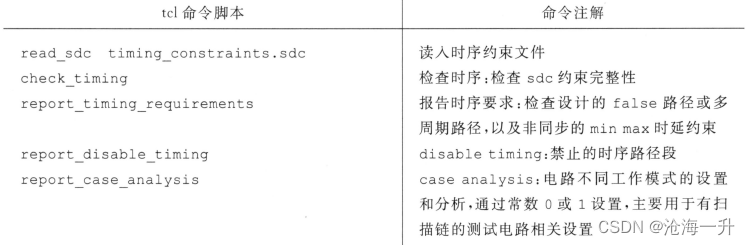

check_mv_design -power_nets 3、应用时序约束并检查

ICC的时序约束要与DC综合阶段相同,最好采用兼容的sdc格式。时序约束应用并检查脚本见表:

sdc文件确保包含对时钟约束偏移、延时、电平转换时间。采用report_clock -skew查看设计的时钟信息。

在数据设置阶段要确保时钟没有定义为传播时钟(CTS步骤后时钟网络建立后传播时钟才有意义),采用report_clock命令查看。

此外,在进行设计布图规划和布局之前,有必要确保设计没有被过度时序约束。约束需要和设计指标对应。下面面脚本里显示了 ZIC (零互连延迟检查)检查步骤。首先设置打开互连线零时延模式,忽略线网传输时延;再检查时序,看是否有明显时序违例;检查后关闭互连线零时延模式。

set_zero_interconnect_delay_mode true

report_constraint -all

report_timing

set_zero_interconnect_delay_mode false

4、去除不需要的理想线网和网络

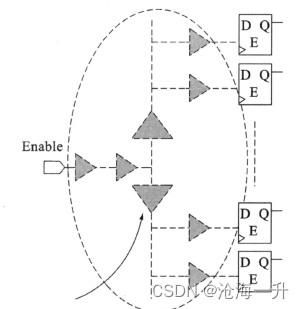

在数据设置阶段去除不需要的理想网络,这些网络一般是高扇出网络,如复位Reset、置位Set、使能Enable、选通Select等系统控制信号。如下图所示,当Enable使能信号去掉后,ICC才能根据时序约束和布局走线的几何信息,合理插入缓冲电路。

理想网络属性通过remove_ideal_network命令去除,例子如下:

remove_ideal_network [get_ports Enable Select Reset]5、数据设置脚本示例

包括创建设计库、设置物理参考库、设置技术文件、 设置tlu +文件、设置并逻辑连接电源和地网络信号,以及对完成的各项设置检查。

createjnw_lib design_lib_orca -open - technology techfile.tf \

-mw_reference_library “sc io ram32"

set_check_library_options -all

check_library

set_tlu_plus_files - max_tluplus cbl3_6m_max.tluplus \

-min_tluplus cbl3_6m_min.tluplus \

-tech2itf_map cbl3_6m.map

check_tlu_plus_files

import_designs design. v -format verilog - top ORCA

list_libs

derive_pg_connection - power_net VDD - power_pin VDD \

-ground_net VSS - ground_pin VSS

derive_pg_connection -power_net VDD -ground_net VSS - tie check_jnv_design -power_nets

read_sdc constraints.sdc #如果读入包含约束信息的ddc,可忽略该步骤

check_timing

report_timing_requirements

report_disable_timing

report_case_analysis r

eport_clock

report_clock -skew

source tim_opt_ctrl.tcl #调用时序优化控制脚本

set_zero_interconnect_delay_mode true

report_constraint -all

report_timing set_zero_interconnect_delay_mode false

remove_ideal_network Eget_ports "Enable Select Reset"]

save_mw_cel - as xxx_setup

其中,时序和优化控制脚本中设定的变量和命令影响ICC后续步骤,因此需要在设计规划(布图)之前设定。示例如下:

#tim_opt_ctrl.tcl

set_app_var timing_enablejnultiple_clocks_per_reg true

set_app_var case_analysis_with_logic_constants true

set_fix_multiple_port_nets -all -buffer_constants

set_auto_disable_drc_nets -constant false

set_dont_use < off_limit_cells>

set_prefer - min < hold_fixing_cells>

set_app_var physopt_delete_unloaded_cells false

set_ideal_network [all_fanout -flat -clock_tree]

set_cost_priority {max_transition max_delay}

set_app_var enable_recovery_removal_arcs true

set-max_area 0

set_app_var physopt_power_critical_range < t>

set_app_var physopt_area_critical_range < t>更多的变量和命令设置,可以查看ICC软件帮助或用户手册。

https://blog.csdn.net/qq_21842097/article/details/120368910

https://blog.csdn.net/qq_21842097/article/details/120368910

917

917

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?