xilinx series 7 PCIE xdma读写测试兼问题记录

PCIE调试之路

最近在调试xilinx 7系列的pcie,遇到了很多问题,用此进行记录和帮助更多的人;欢迎大家一起讨论~~~

在此简单介绍一下PCIE,PCI Express是新一代的总线接口。英特尔公司提出了要用新一代的技术取代PCI总线和多种芯片的内部连接,并称之为第三代I/O总线技术。随后在2001年底,包括Intel、AMD、DELL、IBM在内的20多家业界主导公司开始起草新技术的规范,并在2002年完成,对其正式命名为PCI Express。它采用了目前业内流行的点对点串行连接,比起PCI以及更早期的计算机总线的共享并行架构,每个设备都有自己的专用连接,不需要向整个总线请求带宽,而且可以把数据传输率提高到一个很高的频率,达到PCI所不能提供的高带宽。

划重点:实现的是点对点连接,频率非常高

PCI Express的接口根据总线位宽不同而有所差异,包括X1、X4、X8以及X16(X2模式将用于内部接口而非插槽模式)。较短的PCI Express卡可以插入较长的PCI Express插槽中使用。PCI Express接口能够支持热拔插。PCI Express卡支持的三种电压分别为+3.3V、3.3Vaux以及+12V。用于取代AGP接口的PCI Express接口位宽为X16,将能够提供5GB/s的带宽,即便有编码上的损耗但仍能够提供4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

划重点:支持热插拔,X16兼容X8,X4,X2(均向下兼容)

关于TLP包的详解可以看这位大佬的文章:https://hellocode.blog.csdn.net/

内容有限,历史仅介绍到此。

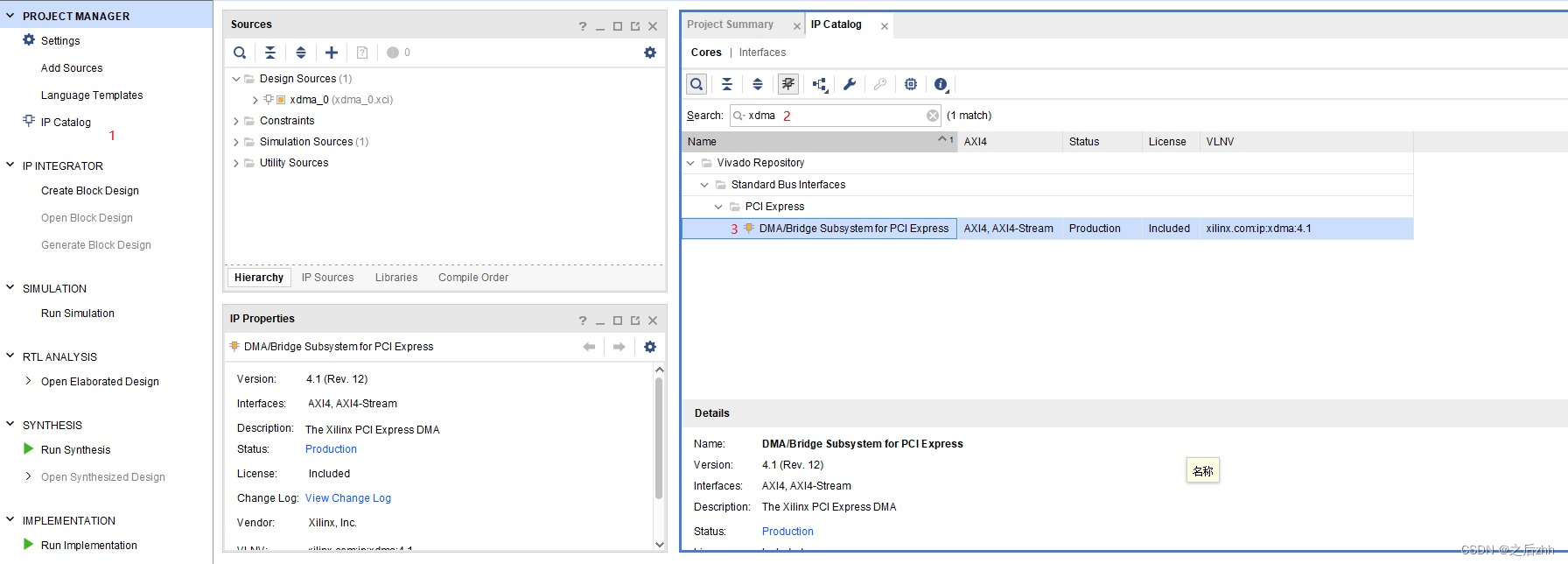

vivado工程创建

- 创建IP,过程如下;

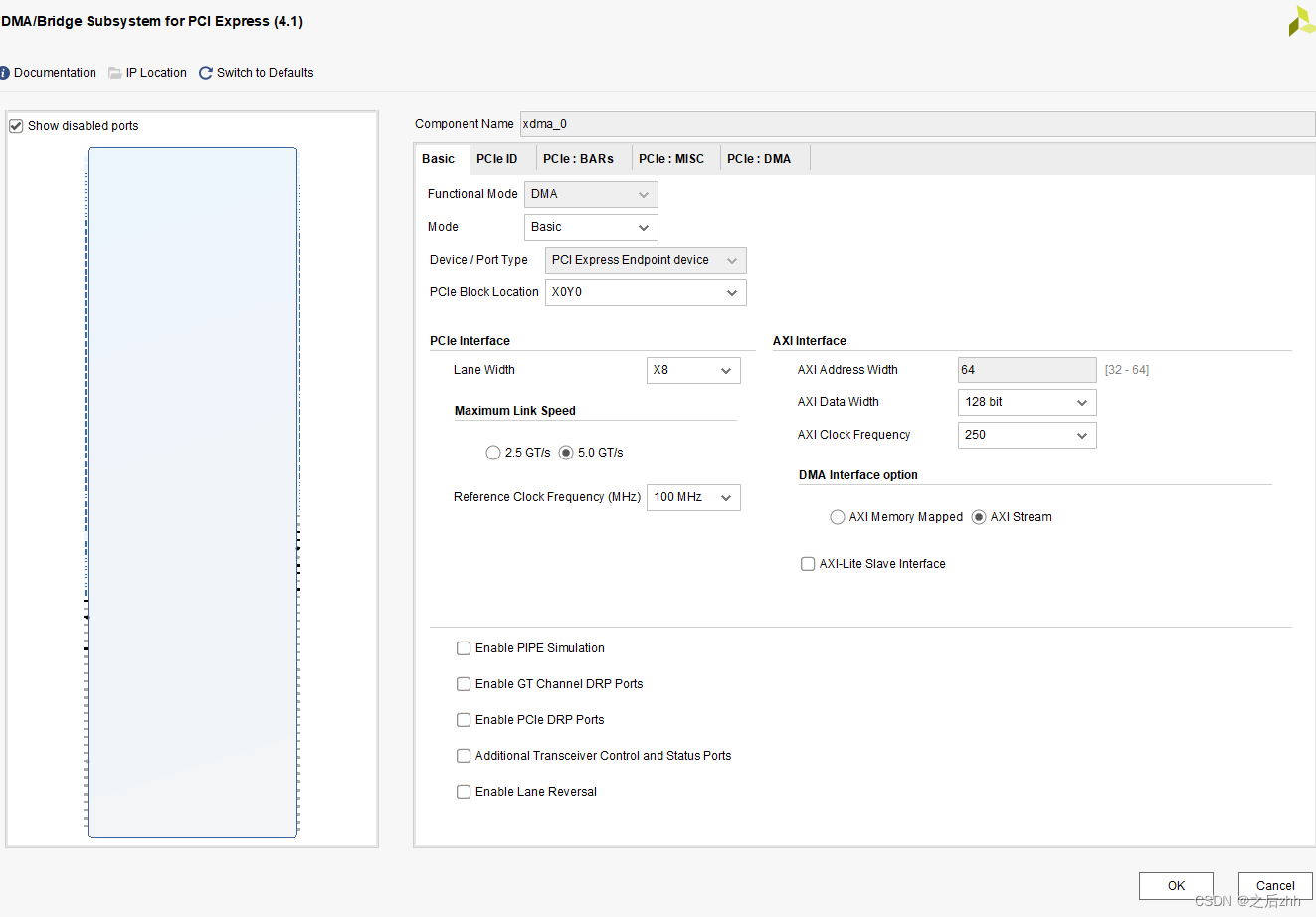

- IP配置如下所示;

Lane Width:KC705支持X8

Max Link Speed:选择5.0GT/s 即PCIE2.0

Reference Clock :100MHZ,参考时钟 100M

DMA Interface Option:接口选择 AXI4 接口

AXI Data Width:128bit,即 AXI4 数据总线宽度为128bit

AXI Clock :250M,即AXI4 接口时钟为250MHZ

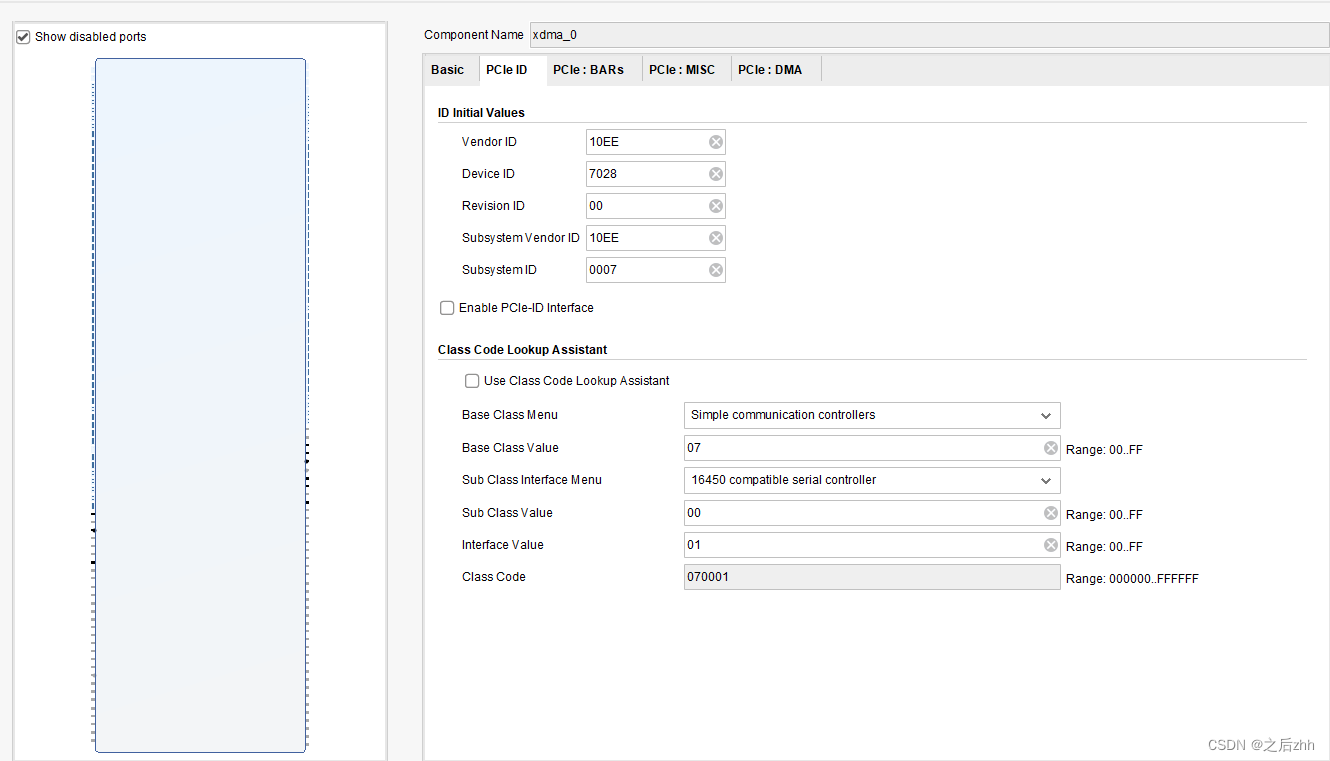

这个界面基本上默认就行VID是厂家编号不需要修改,

Device ID可以按照自己喜欢修改(doge)其余保持默认;

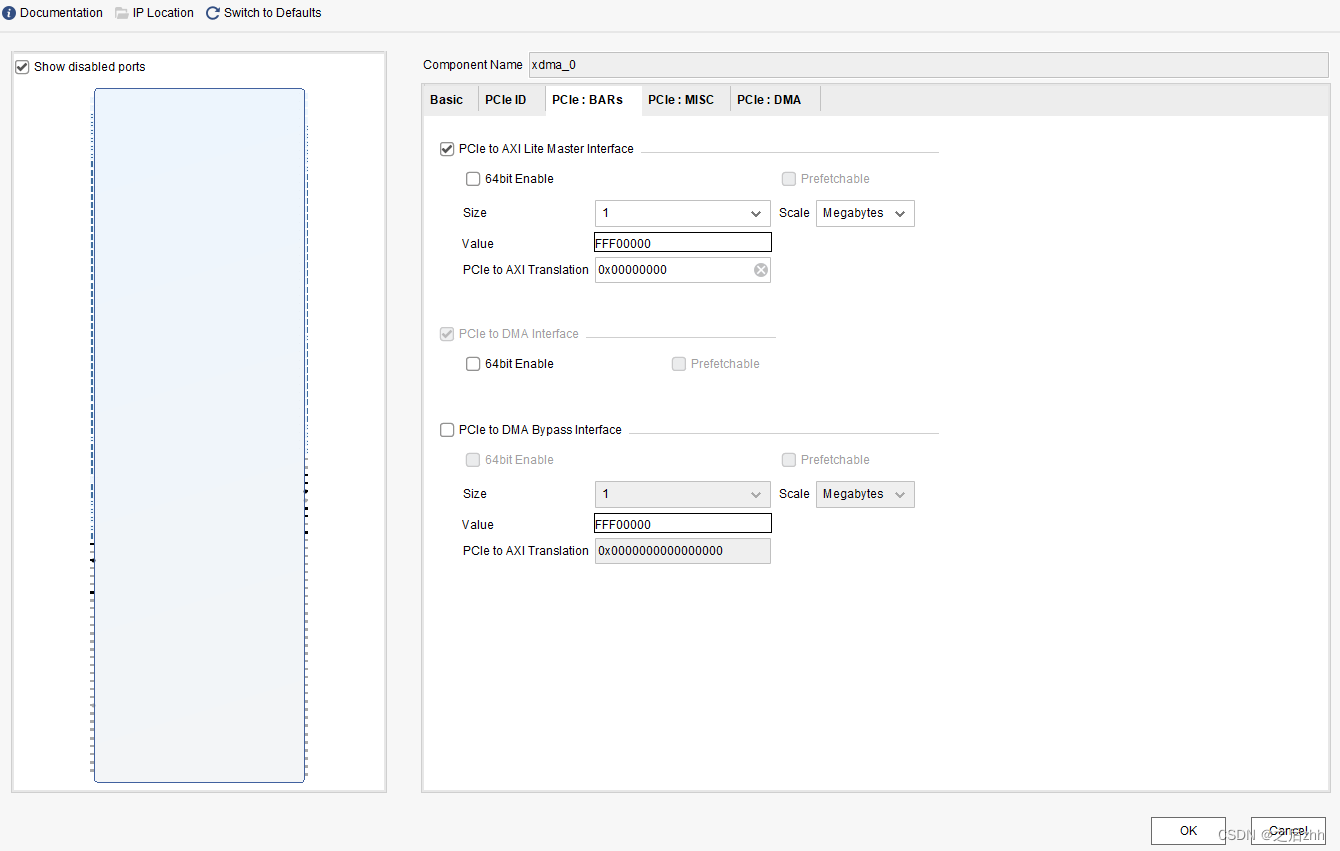

1、首先使能 PCIE to AXI Lite Master Interface ,这样可以在主机一侧通过PCIE 来访问用户逻辑侧寄存器或者其他AXI4-Lite 总线设备

2、查相关资料,PCIE to AXI Translatio:主机侧PCIE BAR 地址与用户逻辑侧地址是不一样的,

这个设置就是进行BAR 地址到AXI 地址的转换,比如主机一侧 BAR 地址为0,IP 里面,转换设置为 0x80000000,则主机访问 BAR 地址 0 转换到AXI LIte 总线地址就是0x80000000;这里先保持默认。

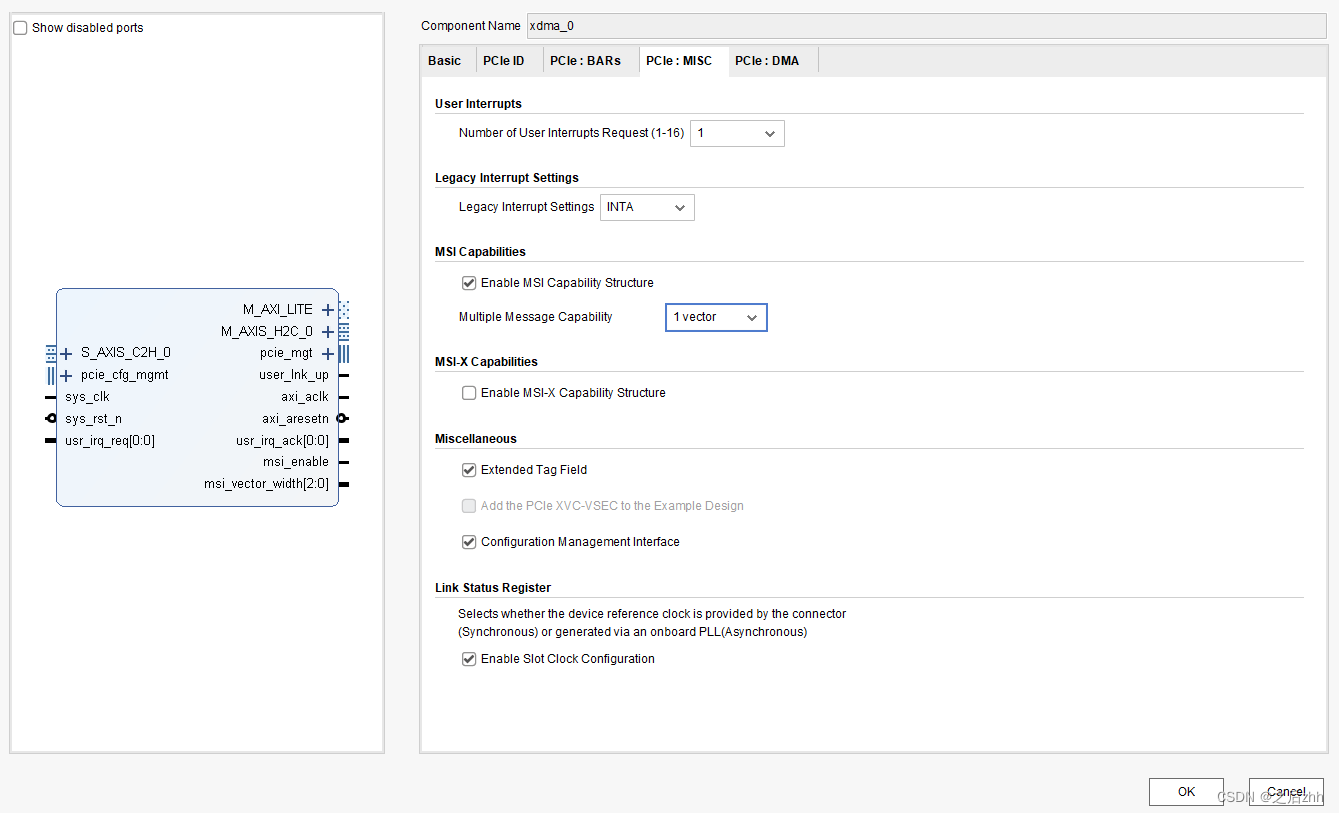

PCIE 中断设置

User Interrupts:用户中断,XDMA 提供16 条中断线给用户逻辑,这里面可以配置使用几条中断线。

Legacy Interrupt:XDMA 支持 Legacy 中断选择 MSI 中断

注意:MSI 中断和 MSI-X 中断只能选择一个,否则会报错,如果选择了 MSI 中断,则可以选择 Legacy 中断, 如果选择了 MSI-X 中断,那么 MSI 必须取消选择,同时Legacy 也必须选择None。此 IP 对于7 系列设置有这么个问题,如果使用Ultrascale 系列,则可以全部选择

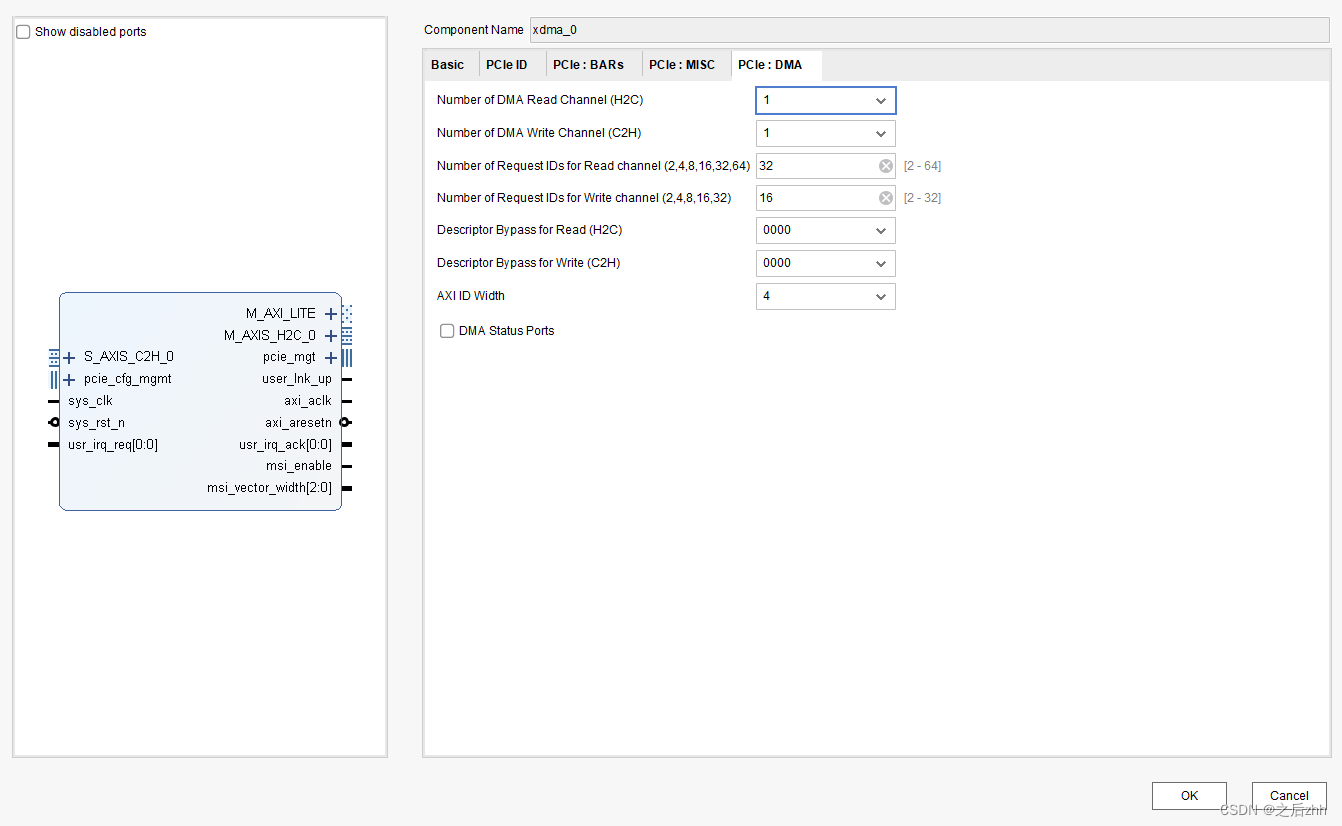

配置DMA 相关内容

Number of DMA Read Channel(H2C)和Number of DMA Write Channel(C2H)通道数,对于PCIE2.0 来说最大 只能选择 2,也就是 XDMA 可以提供最多两个独立的写通道和两个独立的读通道,独立的通道对于实际应用中 有很大的作用,在带宽允许的前提前,一个PCIE 可以实现多种不同的传输功能,并且互不影响。

Number of Request IDs for Read (Write)channel :这个是每个通道设置允许最大的outstanding 数量,按照默认即可。

其余选项保持默认。

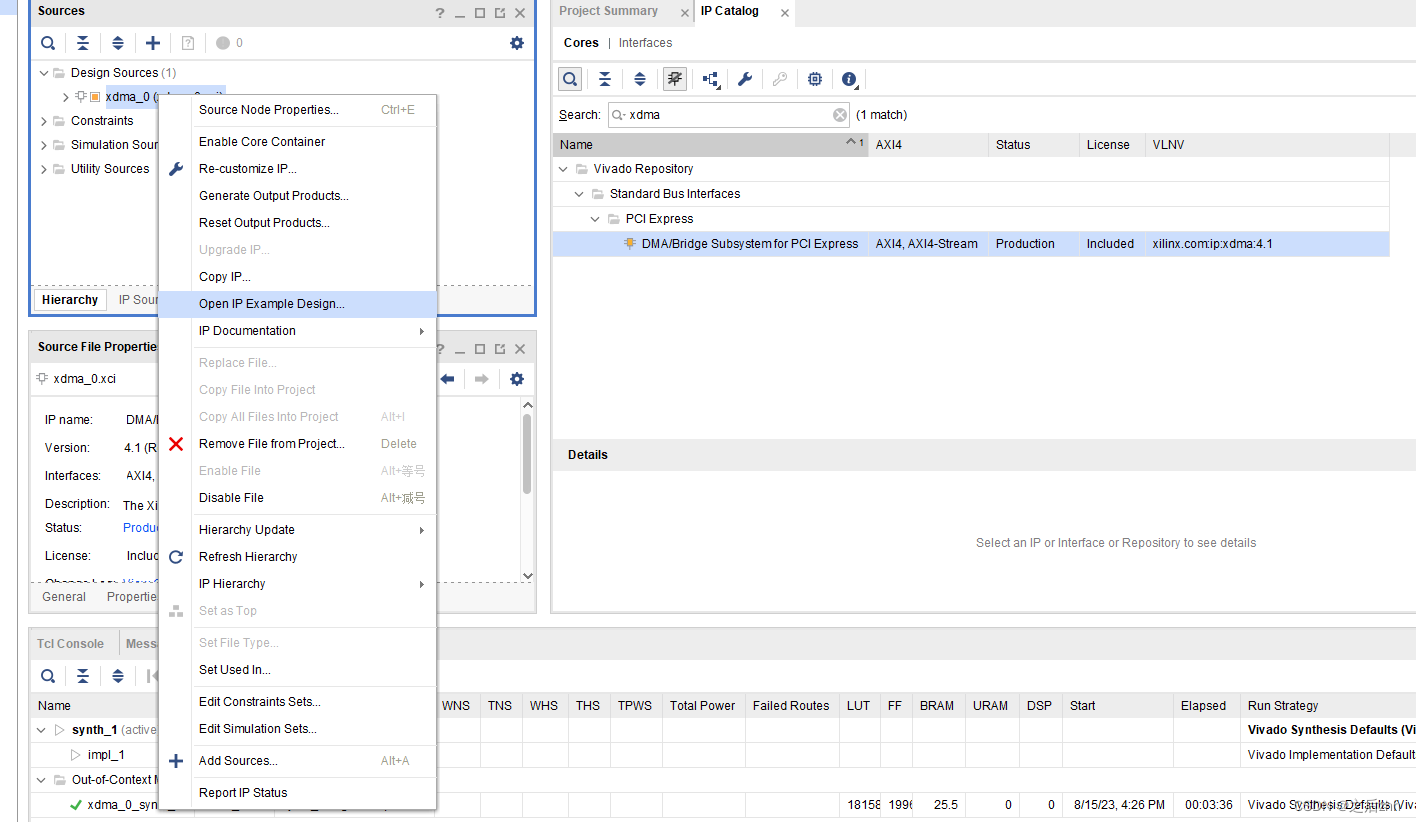

- 生成IP;

- 打开IP的example design;

注意,要等IP完全design完成之后才可以打开example design;

- 打开block之后添加约束即可加载比特流,不再赘述。

PC识别PCIE板卡

这个调试用了我大概两周的时间,下面来进行详细描述。主要用来记录调试过程中遇到的问题以及如何解决

我使用的开发板是KC705官方评估板,没有专用的原理图手册,只能去官方的uesr guide慢慢查找。

第一周调试:开发板支持X8接口,我使用的电脑上只有X1的接口。

购买了X8转X1的调试线,结果在此电脑上识别不了,于是换了一台电脑(看论坛都说这是个大坑索性直接换了一台之前不用的电脑),还是识别不出来。(陆陆续续调试了一周左右,还是都在门外,都没进门,主要写这篇也是为了方便大家更容易走进去),还有其他杂七杂八的事情就耽搁了一段时间

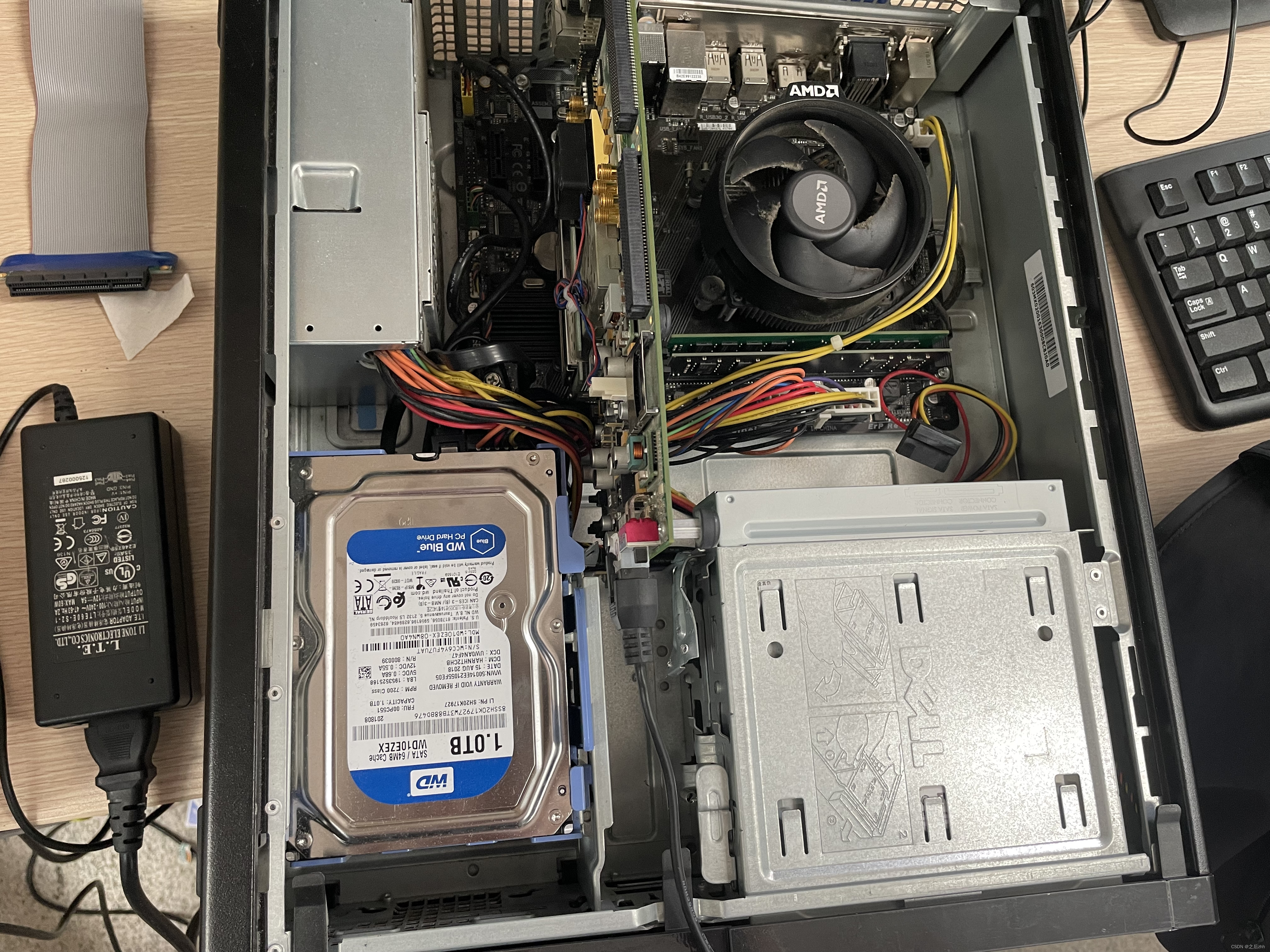

第二周调试:开发板支持X8接口,更换新的PC支持X16。于时购买了X8的延长线(注意可以直接买X16延长线;有条件可以直接插入到电脑主板上);

使用延长线还是不可以,然后我暴力拆解了电脑,方便我直接插入进去。

修改之后再次识别,还是识别不了,这个时候其实有点想放弃了,因为还没到数据识别错误的底部,还不用去加ila,仿真,仅仅识别都识别不了;;;

最后还是准备从头到尾分析一边,这里也带大家去理一下思路:首先,工程的建立都是按部就班来的,代码几乎都没有进行修改,打开XDC文件,我发现我的约束只有4个接口(这里使用的是X8接口,输入输出应该都是8个接口),好!能找到问题就行,赶紧修改。

可惜,还是识别不了。

按照https://hellocode.blog.csdn.net/,大佬文中描述,我使用了50的加速,上电顺序应该是没问题

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

应该还是xdc约束问题,因为大佬使用的板子和我的一样,所有io口的约束都一样,没想到

居然rst不一样!!!!

在我修改了rst引脚之后,直接识别到了,好吧,这也是我粗心的一个问题。历经两周,终于先把门给敲开了。

上位机调试

这里简单介绍一下AR65444工具,在win和linux里面是不一样的。(工具的使用挺难搞的)

windows:

这是windows所用到的工具,info是用来检测PCIE设备。

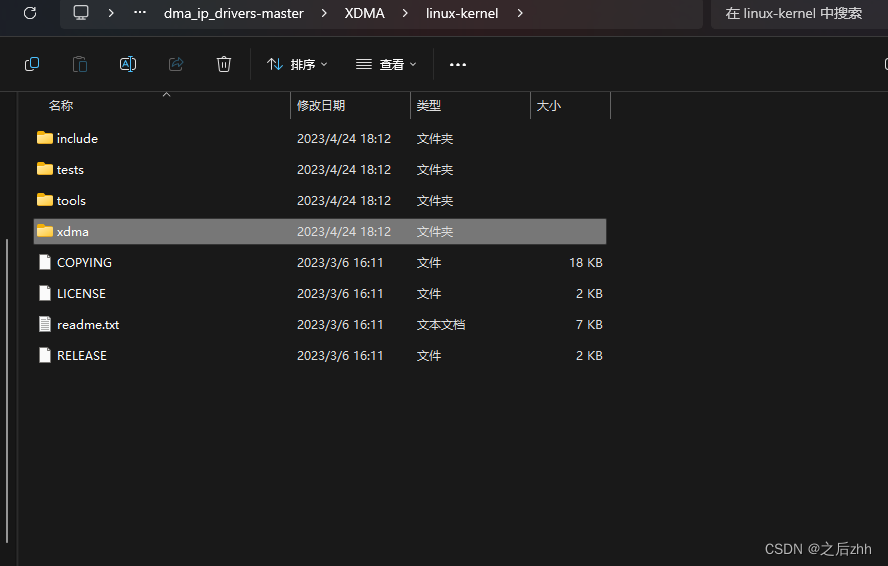

linux:

本次测试尚未使用此工具,使用windriver测试,均正确。

接下来使用AR65444进行调试,包括AXI-Lite,读写寄存器等,敬请期待

724

724

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?