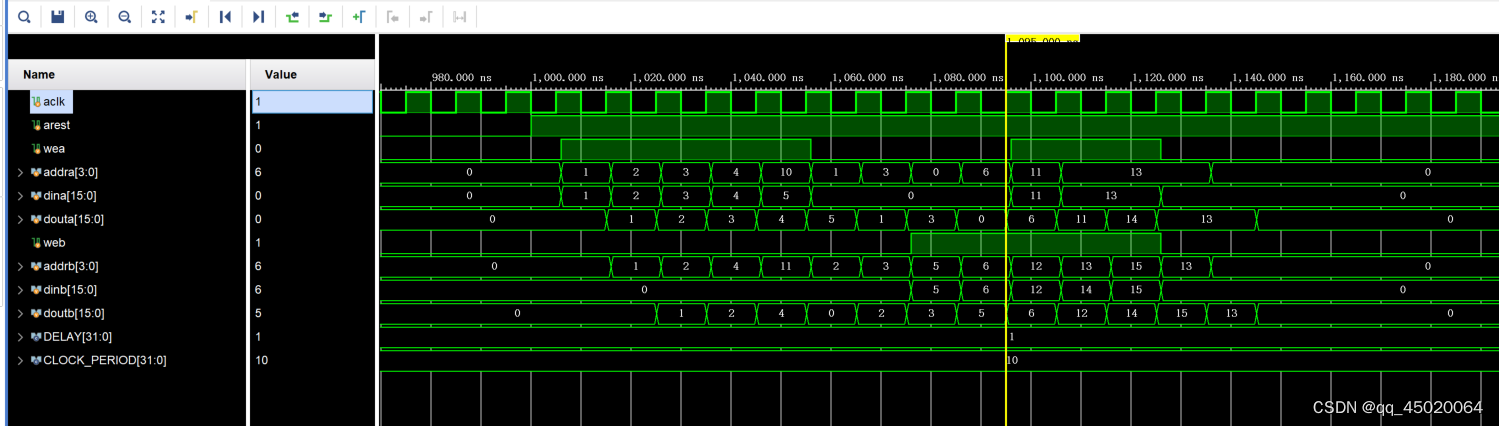

最近项目中,需要利用 block ram进行直方图统计,在生成过程中我使用了ture dual port 同步block ram,ab端口均设置为WF:仿真结果如下:

即当 true dual port 配置为common clk时,将ab设置为write first,当ab地址一致,且一端读、一端写,如a往4地址写4,b读地址为4,dout均为a现在写入的4;

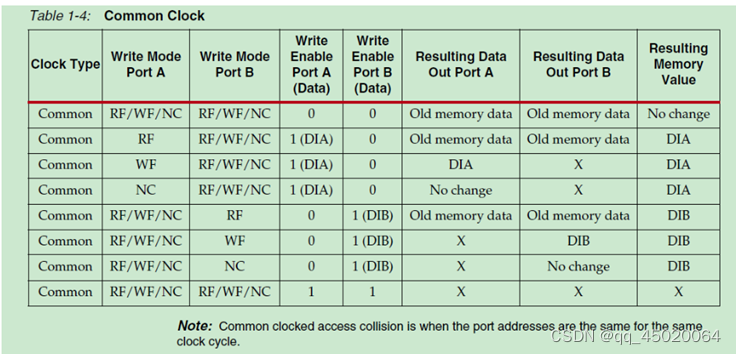

然而下板之后,每次测试的直方图统计结果不一致,查阅资料,发现:

读写冲突时,读出值为不定态X,和xilinx仿真模型不一致!!!!!!

建议读写地址冲突时,一定要自己做一个电路的旁路处理。

这里是引用

https://blog.csdn.net/linbian1168/article/details/88827360

620

620

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?