前言

本文通过引入Latch和Flip-Flop深入分析为何DFF需要setup time和hold time

Latch与Flip-Flop

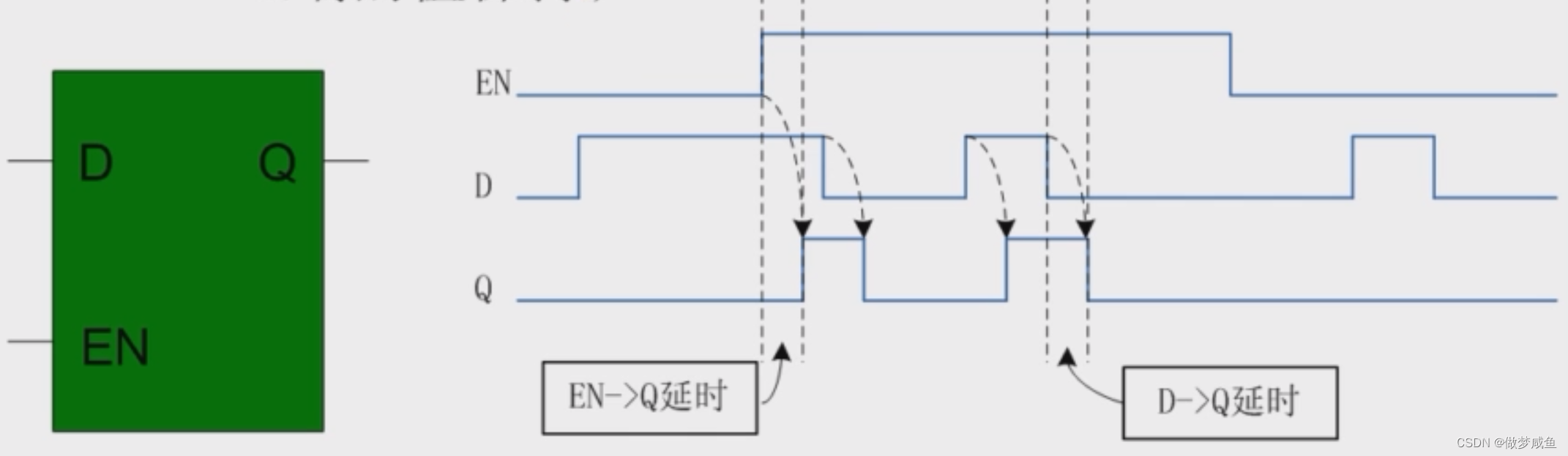

Latch属于组合逻辑电路,其时序图如下,最大的特点在于EN->Q以及D->Q均有延时

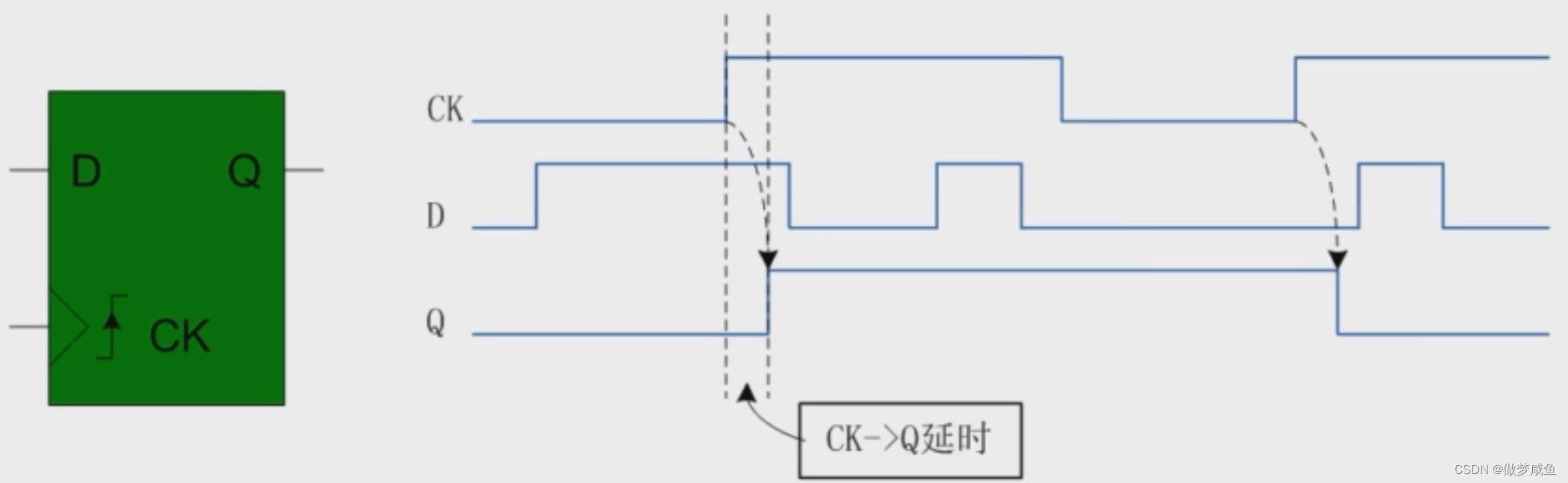

而Filp-Flop的延时来源于CK->Q

问题引入

为何Flip-Flop(DFF)没有D->Q的延时?

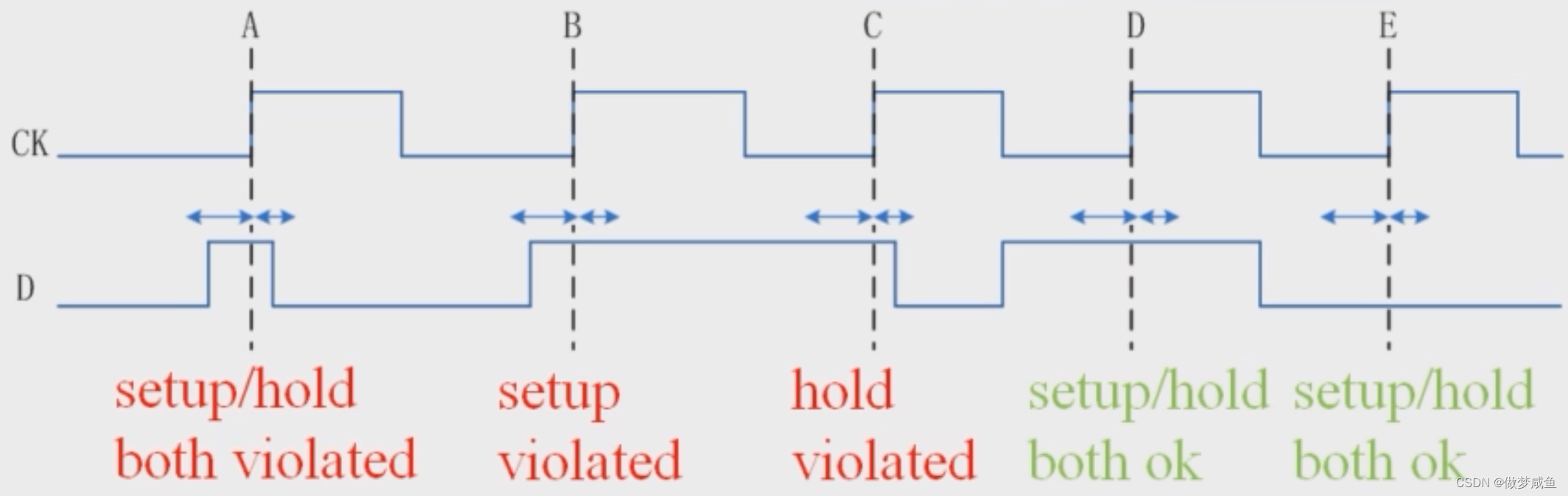

答: 在CLK上升沿的一瞬间,D端的信号必须保持稳定,在上升沿之前的一段稳定时间为建立时间setup time,在上升沿之后的稳定时间为维持时间hold time。

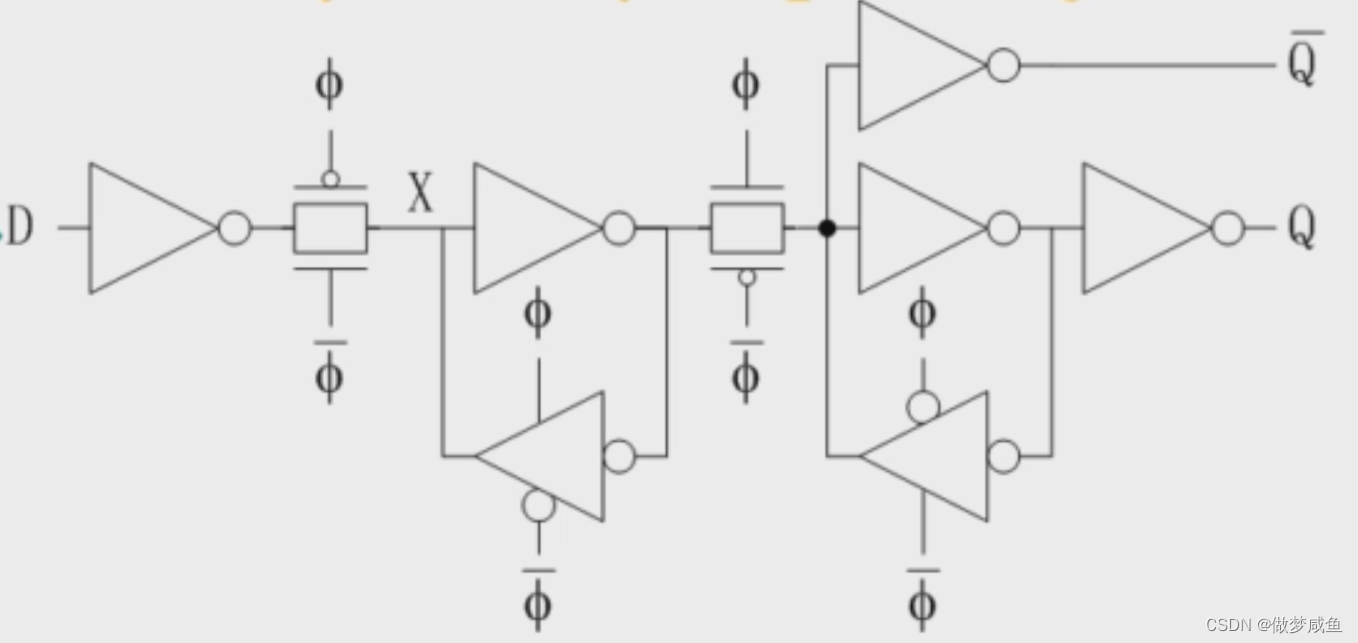

DFF电路结构

那么,为何DFF需要setup time和hold time?

这需要从DFF的电路结构理解,DFF的一种电路图如下所示,其中Φ为CLK信号

- 当CLK为0时,左侧的

传输门打开,D端信号通过传输门进入到反相器的输入端,也即X信号,而右侧的传输门会关闭,信号被锁存在中部电路- 当CLK为1时,左侧的传输门关闭,右侧的传输门打开,信号输出到Q端

那么,信号则必须从D端传入到X点之后传输门才能关闭,也即对应了setup time。并且CLK置1时,关断左侧传输门本身需要时间,这时D端信号不能变化,否则在传输门完全关断之前,D端信号依旧可以传输到DFF内部,也即对应了hold time

更详细的时间计算可参照这篇博客:为什么会有建立时间setup和保持时间hold要求

问题拓展

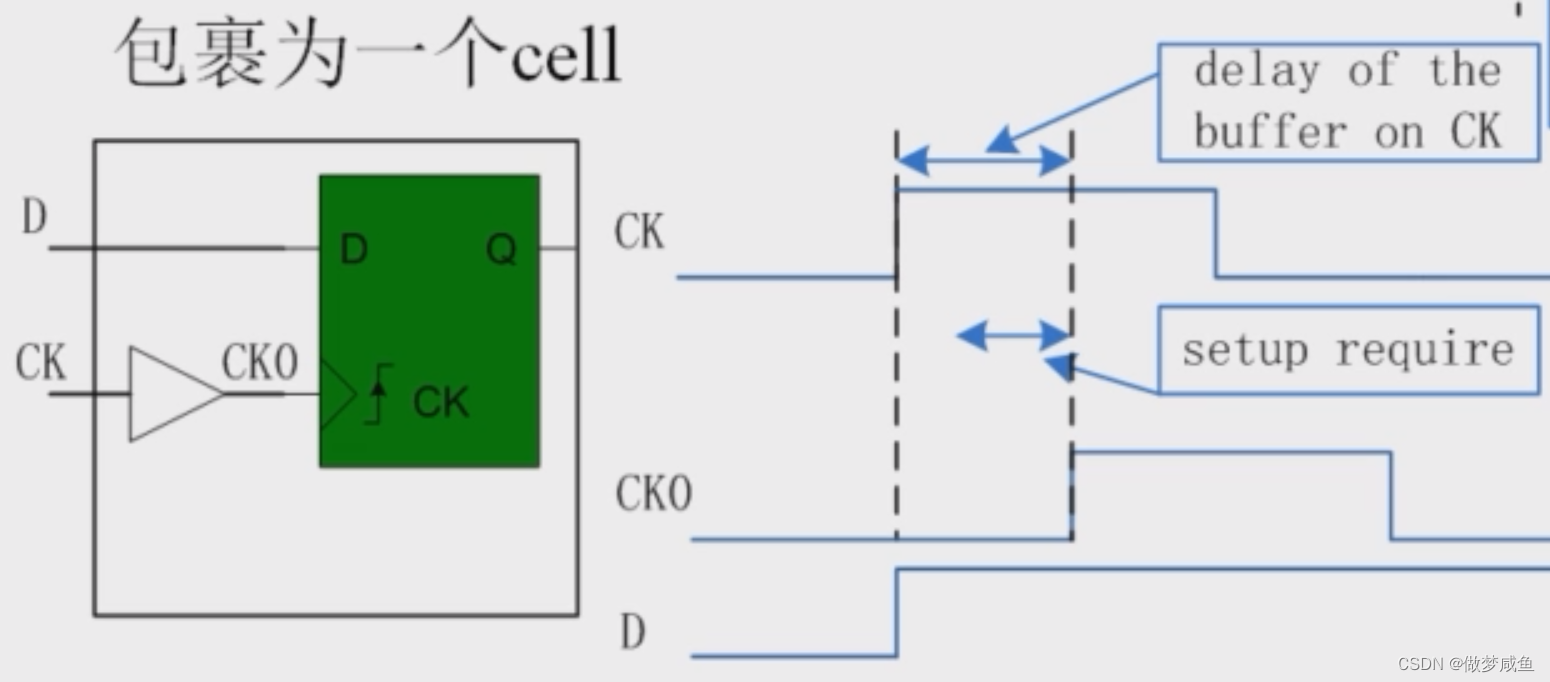

在cell library中DFF的setup time可以设置为0吗

答案是可以的,如下图所示,在CLK的前端加一个buffer,用于延时,相当于将clk的波形置前了,此时CK的上升沿可以与D端的上升沿对齐,甚至setup time可以为负数

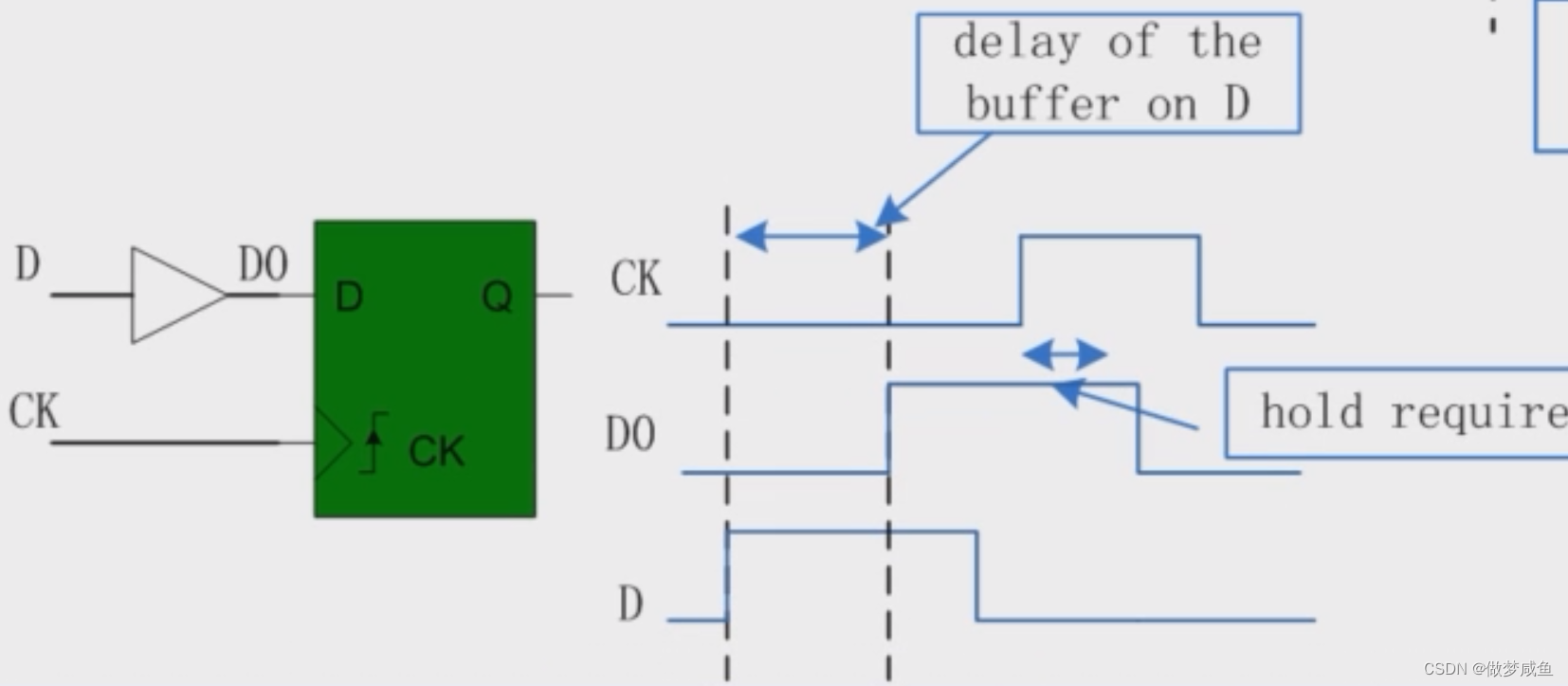

那么,在cell library中DFF的hold time可以设置为0吗

答案也是可以的,如下图所示,在D端的前面加上一个buffer,用于延时,相当于将D端口的波形置前了

那么,一个DFF cell的setup time和hold time可以同时为0吗?

显然是不可以的,因为setup time和hold time叠加本来就是一段时间,也就是setup time+hold time必须为正数,为一个时间窗口,且等于最基本的DFF的建立时间与维持时间之和

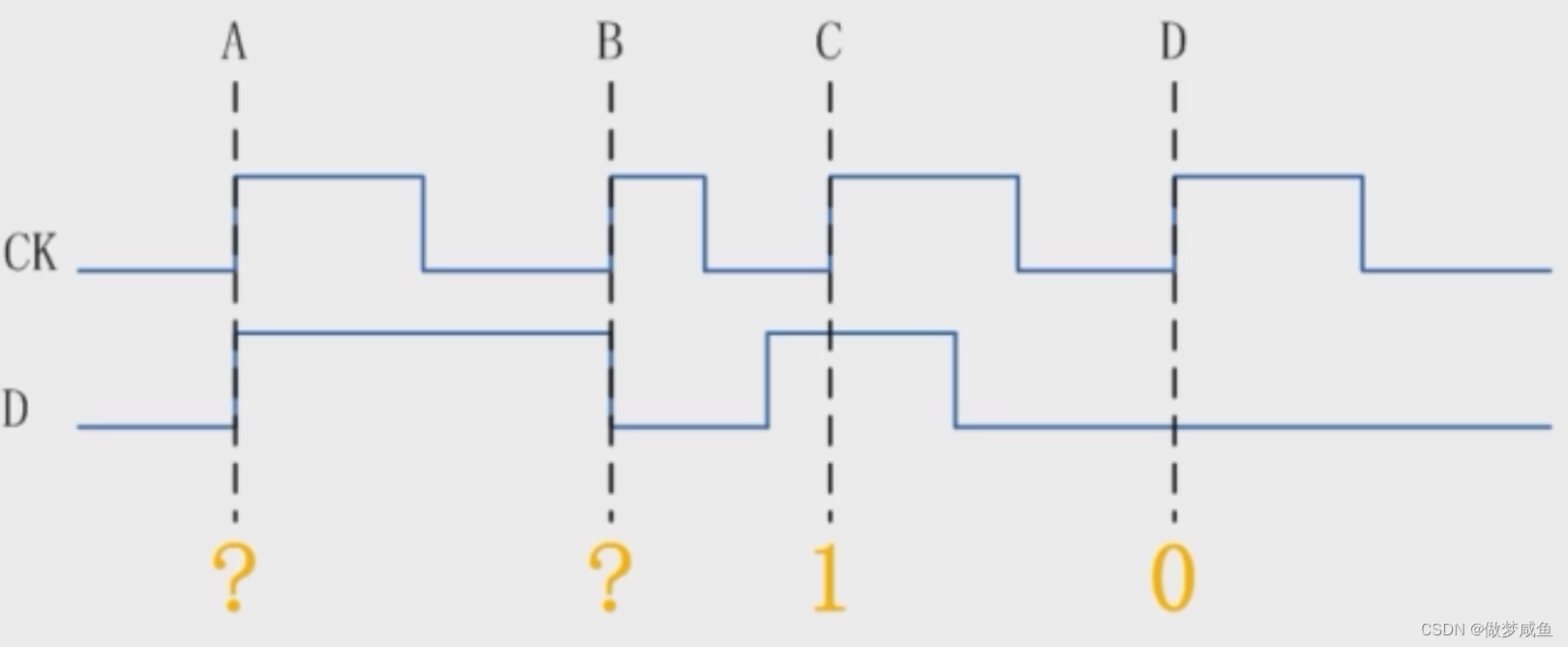

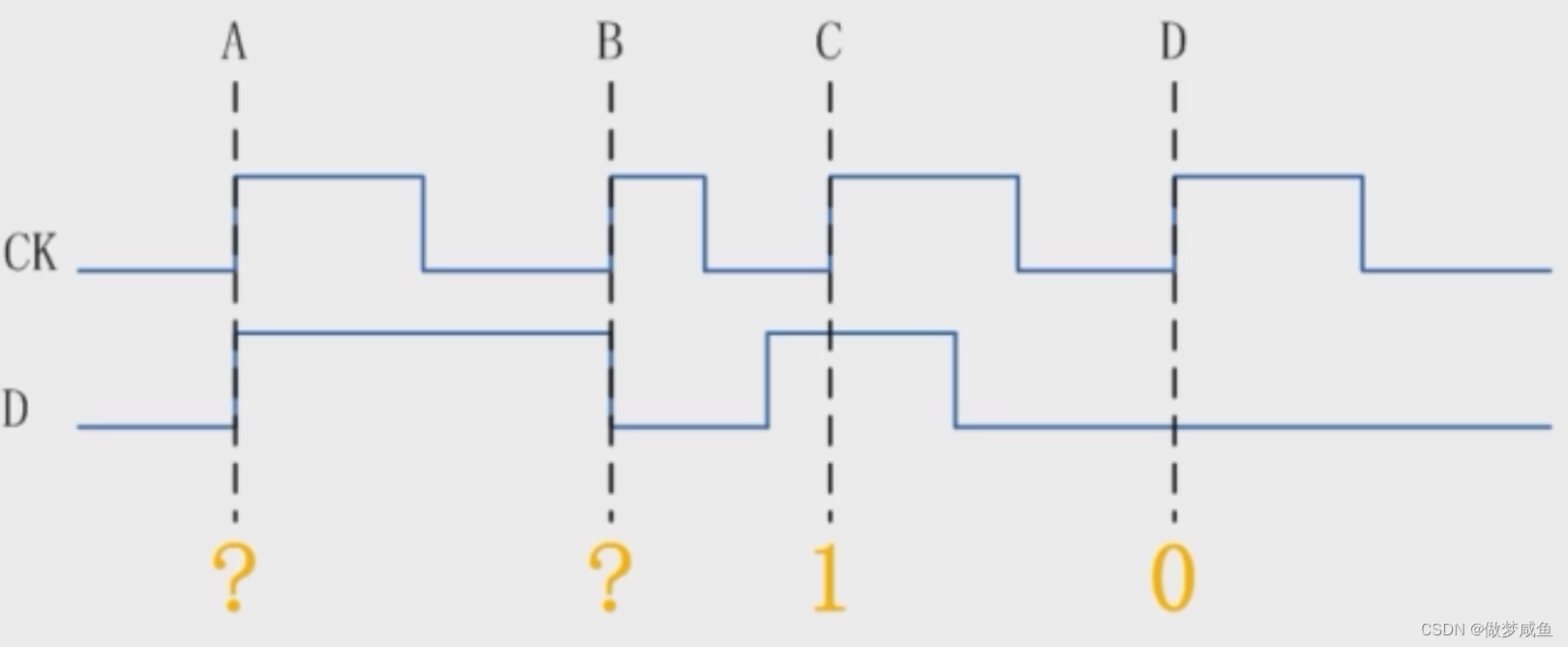

仿真歧义

再次拿出这张图,在Verilog仿真阶段该DFF可能有正常的输出,也有很多人质疑该时序图能够正常的输出,是因为仿真与实际电路是有区别的,仿真避开了电路的结构,可以直接输出CLK前一段时间的D端输入数据

码字不易,欢迎点赞+关注+收藏

3691

3691

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?