第一步 新建工程

新建工程选择开发板,进入vivado界面,这里就不多说了。

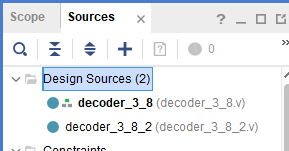

第二步 添加design souce

这一步就是写我们要测试的Verilog模块,因为只是仿真,所以我们不需要综合和实现,也因此我个人认为,在design souce里面的文件就不需要按照顶层到底层的方式写,而是将需要测试的模块都放在里面。

这里我添加了两个文件,分别是两种方式实现的38译码器:

其中各个文件的代码如下:

//decoder_3_8.v

`timescale 1ns / 1ps

module decoder_3_8(add,decode);

input[3-1:0] add;

output[7:0] decode;

assign decode = 8'h1 << add;

endmodule

//decoder_3_8_2.v

`timescale 1ns / 1ps

module decoder_3_8_2(

input wire[2:0] a,

output reg[7:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

819

819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?