文章目录

- 一.在Quartus II中用原理图输入法设计4位加法器

- 1.打开1位全加器项目文件

- 2.新建4位全加器原理图文件

- 3.新建波形文件

- 4.引脚绑定及测试

- 二.应用QuartusII 完成基本组合电路设计

- ①利用QuartusⅡ完成2选1多路选择器

- 1.新建工程

- 2.创建VHDL文件

- 3.编译

- 4.功能仿真

- 5.查看RTL电路和门电路

- 6.硬件测试

- ②双2选1多路选择器

- 1.新建VHDL文件

- 2.编译

- 3.新建波形图

- 4.查看RTL电路及门级电路

- 5.硬件测试

- 三.应用QuartusII 完成基本时序电路的设计

- ①设计触发器

- 1.新建工程

- 2.新建VHDL文件

- 3.编译

- 4.新建波形文件

- 5.查看RTL电路及门级电路

- 6.硬件测试

- ②设计锁存器

- 1.新建工程

- 2.新建VHDL文件

- 3.编译

- 4.新建波形文件

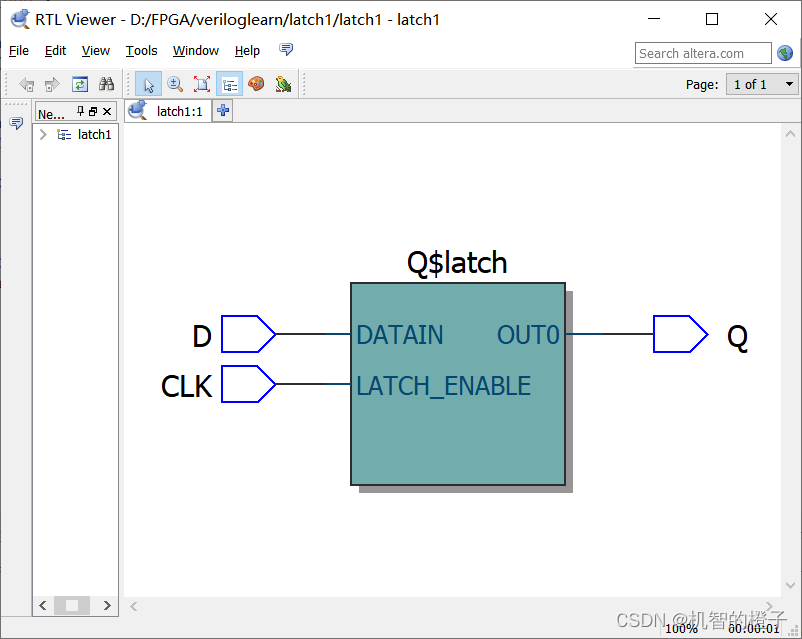

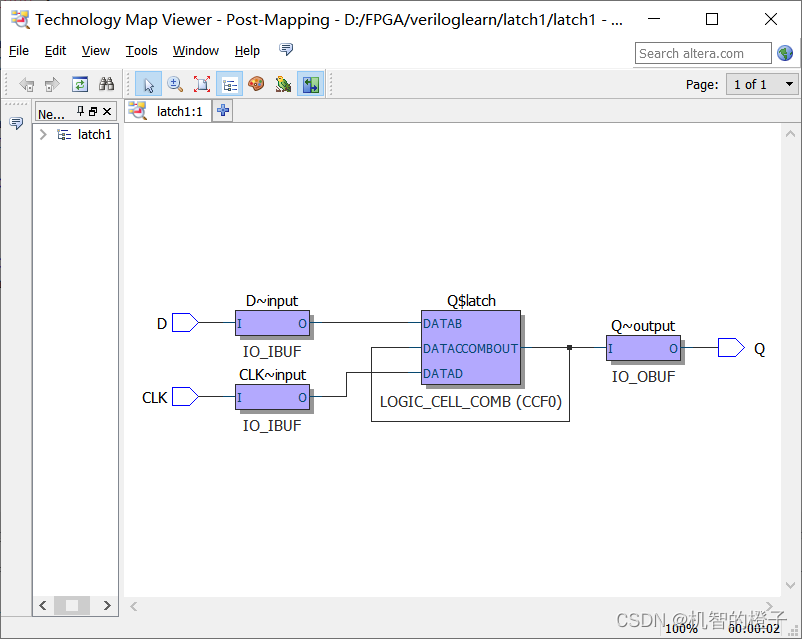

- 5.查看RTL电路及门级电路

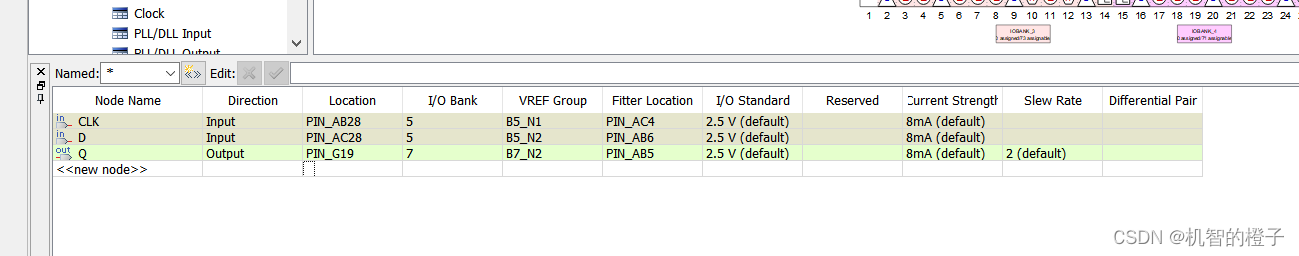

- 6.硬件测试

- 四.总结

- 5.参考链接

一.在Quartus II中用原理图输入法设计4位加法器

这里利用上次生成的一位全加器原理图(参考:https://blog.csdn.net/qq_45659777/article/details/123444666)

,通过四个一位全加器实现4位全加器

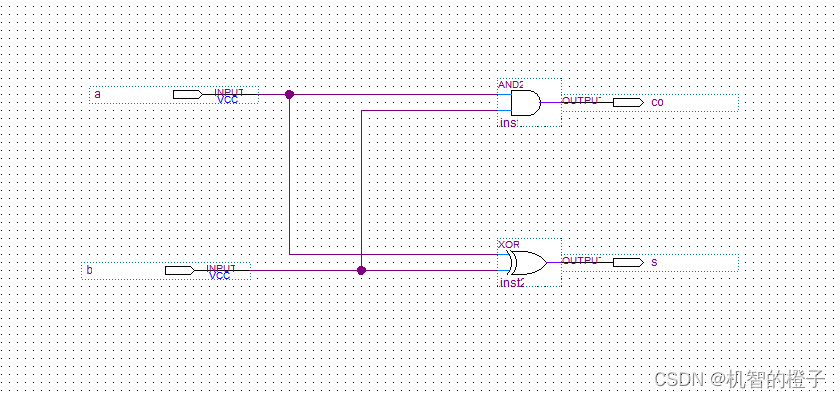

半加器原理图:

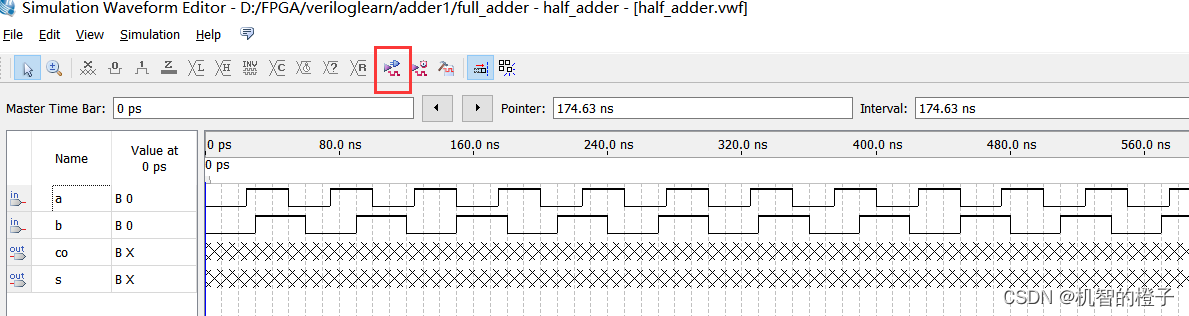

半加器波形文件:

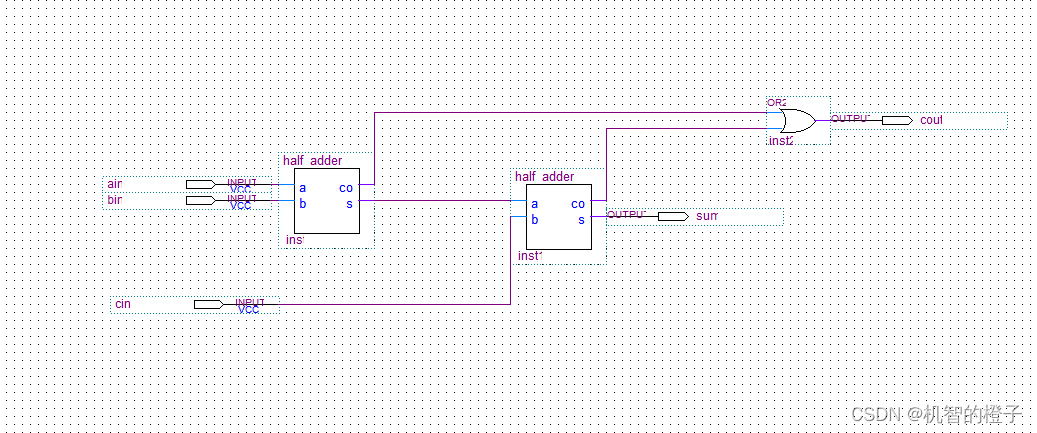

1位全加器原理图:

1位全加器波形图:

1.打开1位全加器项目文件

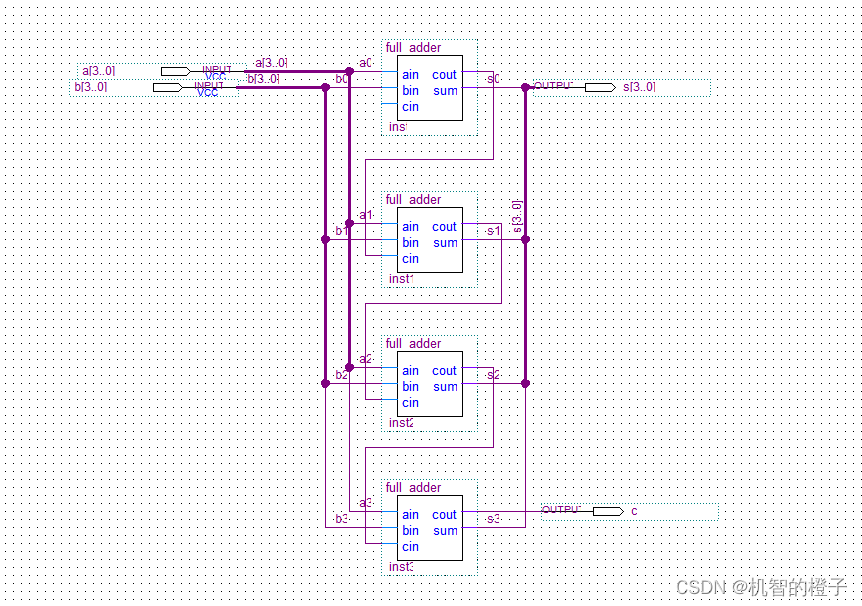

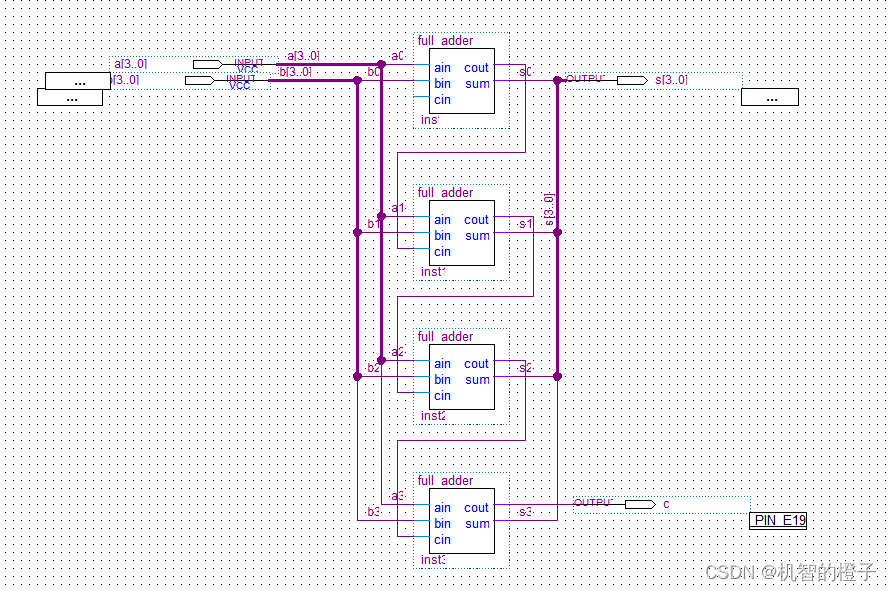

2.新建4位全加器原理图文件

注意这里用到了总线Bus Line

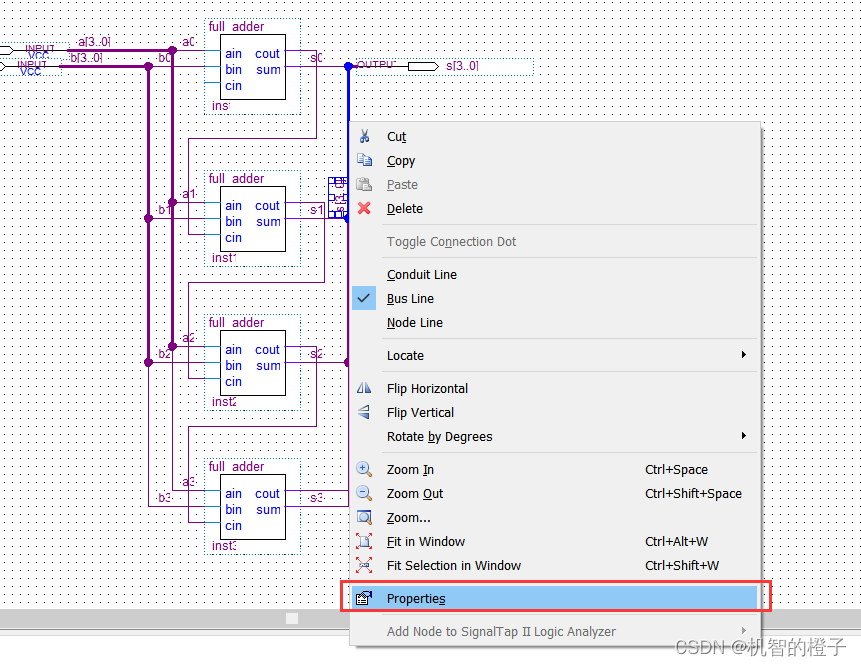

在对线命名的时候,选中该条线,然后右键,选择properties,就可以给线命名了。

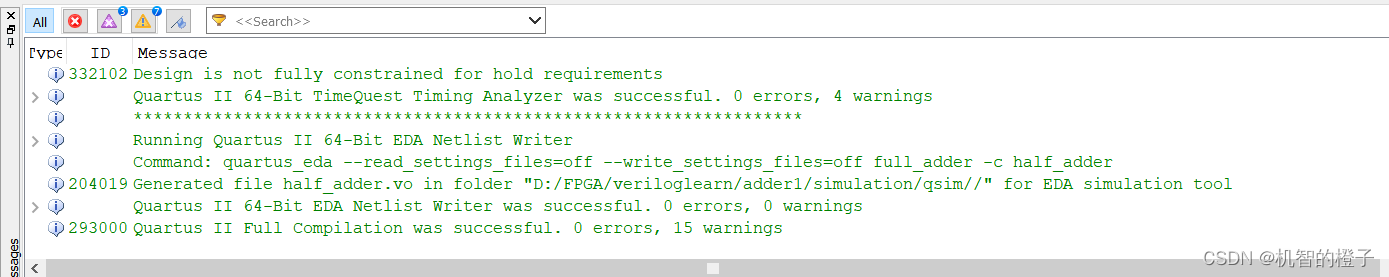

保存该文件,并编译

编译成功,无错误

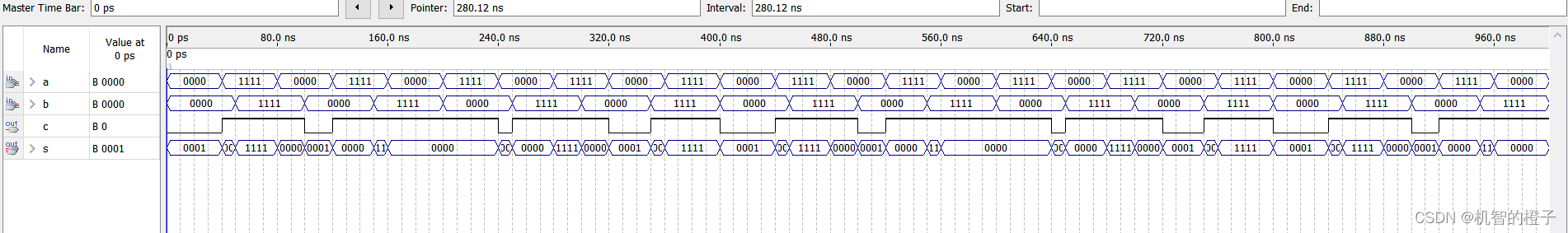

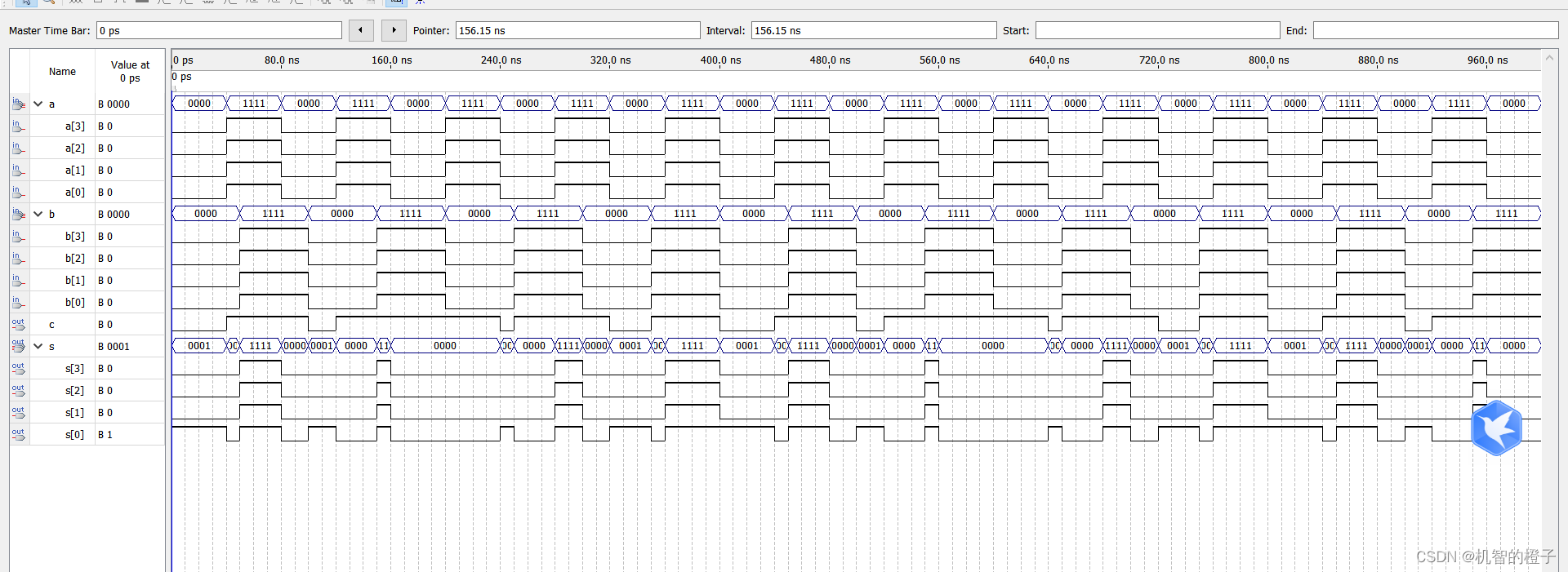

3.新建波形文件

保存,编译

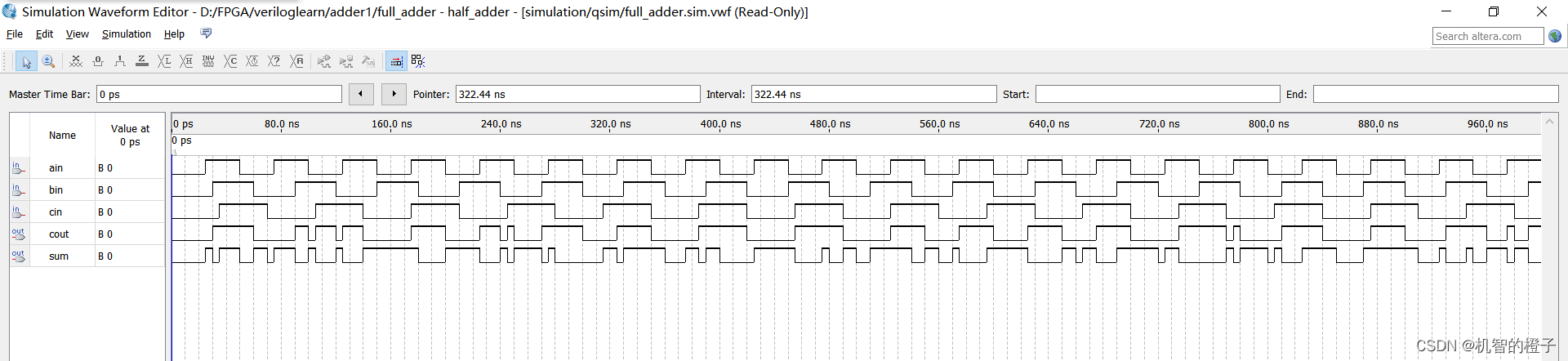

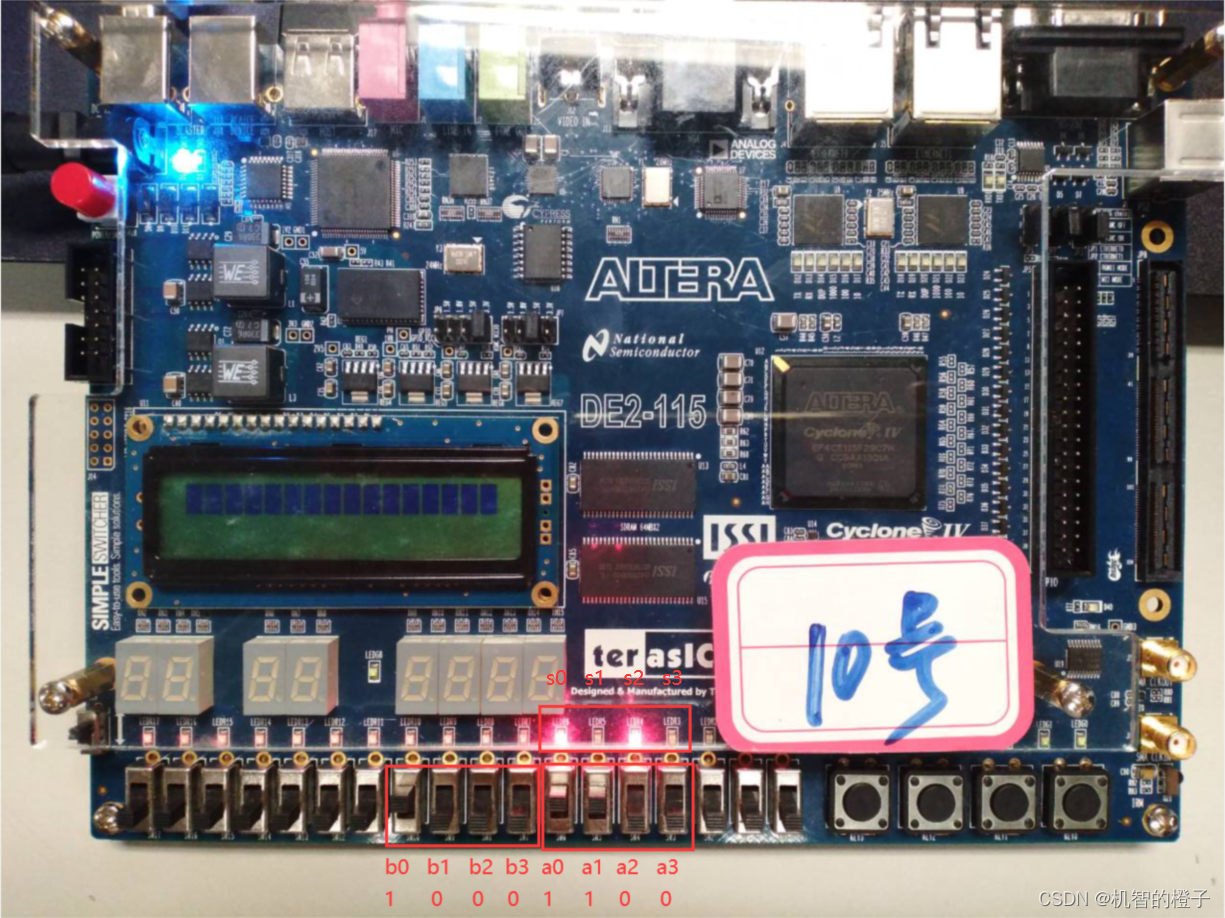

满足公式:s=a+b+c;s>15,进位c=1

该全加器为4位全加器,当低位数字开始相加时,会加上开始的进位,依次从低位开始相加,同时地位向高位进位。

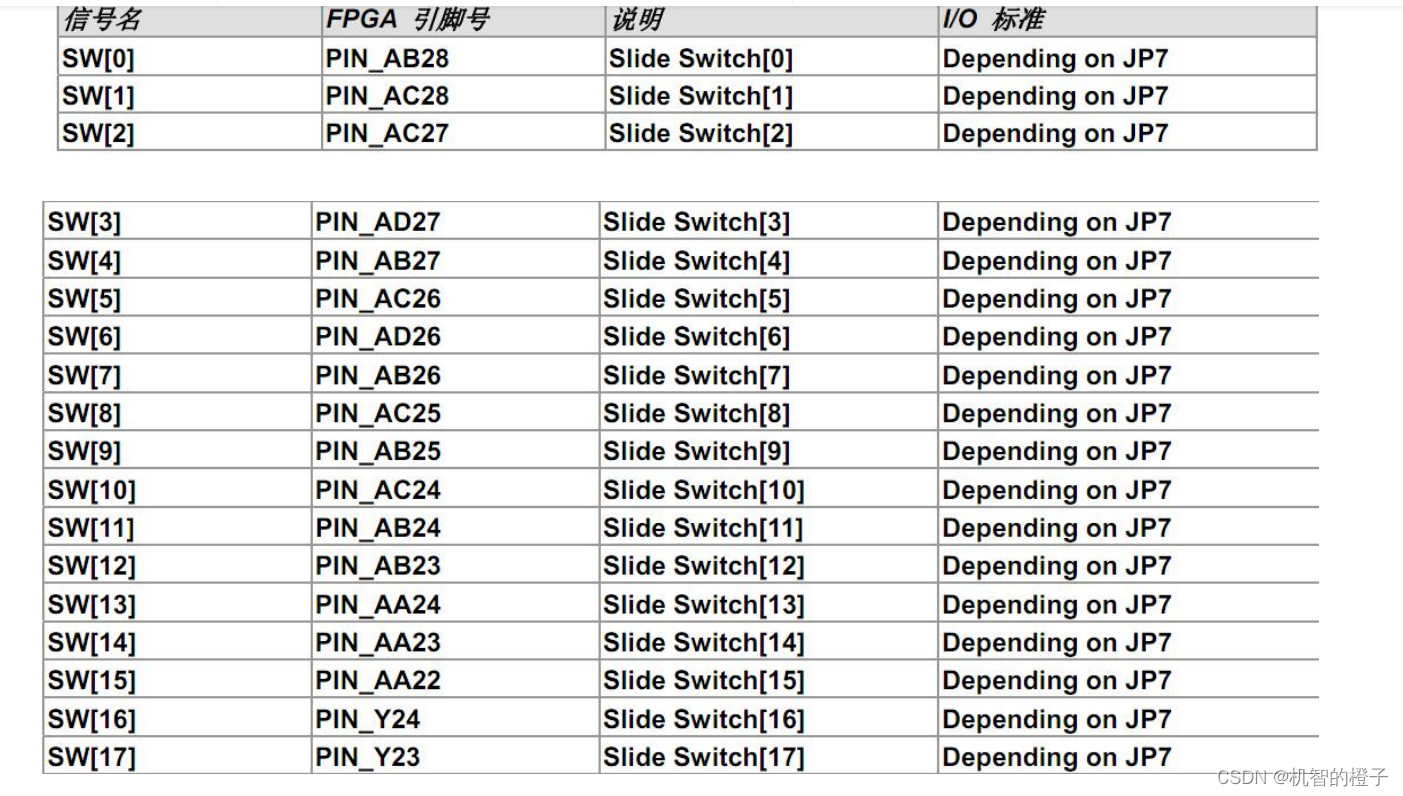

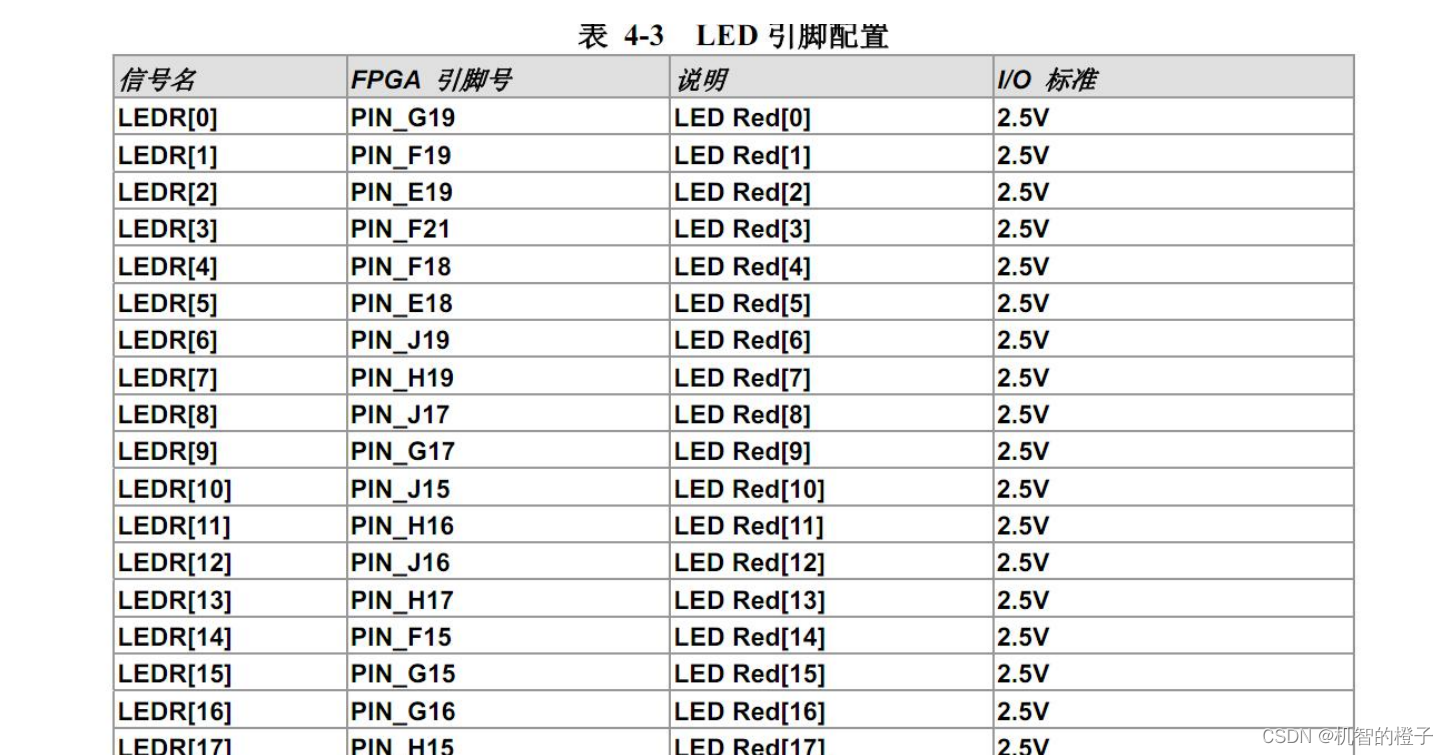

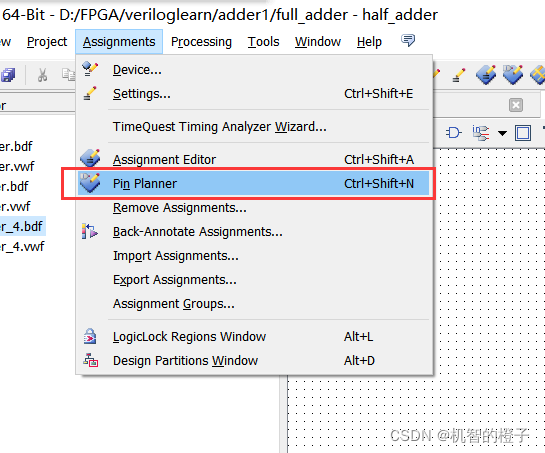

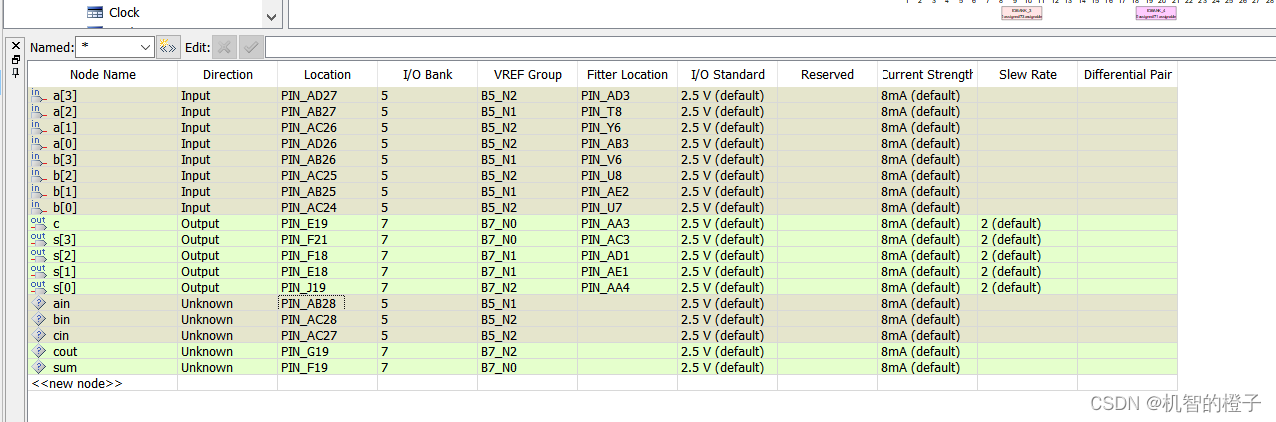

4.引脚绑定及测试

查看开发板引脚图,找到相关引脚,将需要使用的引脚,绑定到原理图上对应的输入处

相应找到LED引脚配置为输出

绑定引脚

绑定成功

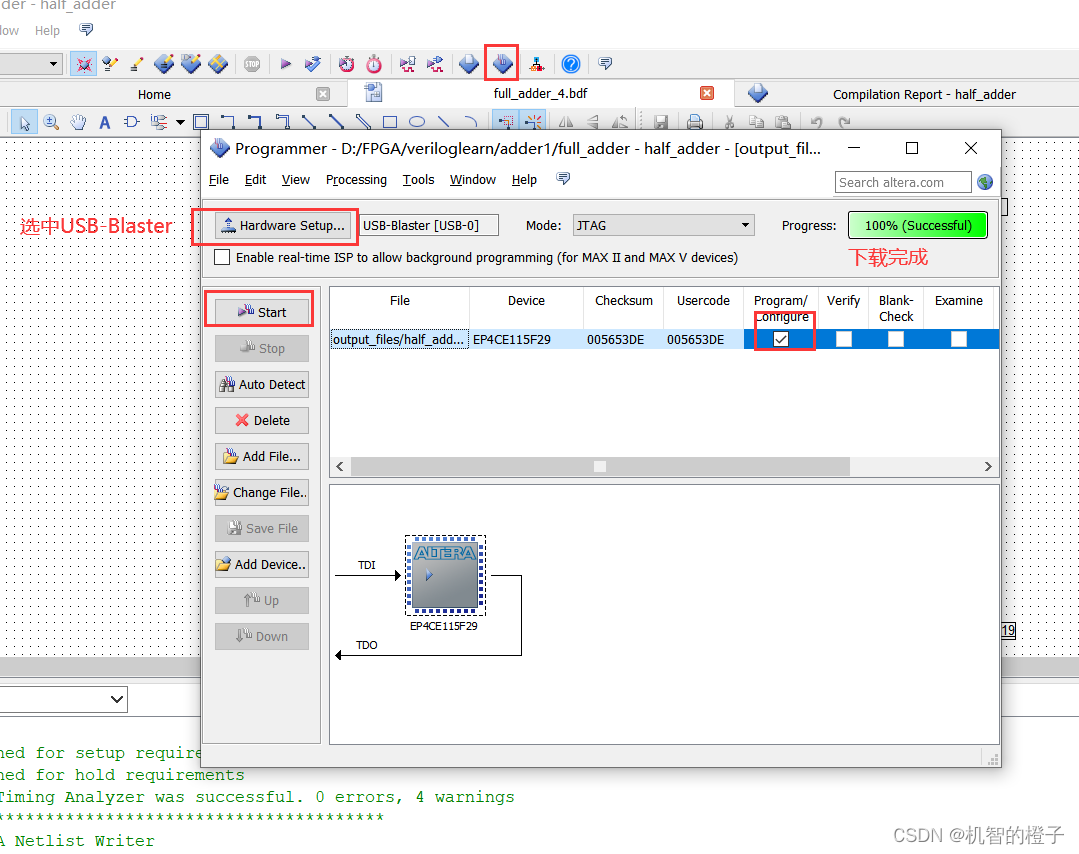

下载测试

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。点击软件工具栏上的按钮 ,则出现下载界面。第一次下载需安装硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USBblaster”,再点击“ok”,则硬件被安装上。

安装好硬件后,在下载的.sof文件后打钩,再点击start,看到100%(successful),下载成功

二.应用QuartusII 完成基本组合电路设计

①利用QuartusⅡ完成2选1多路选择器

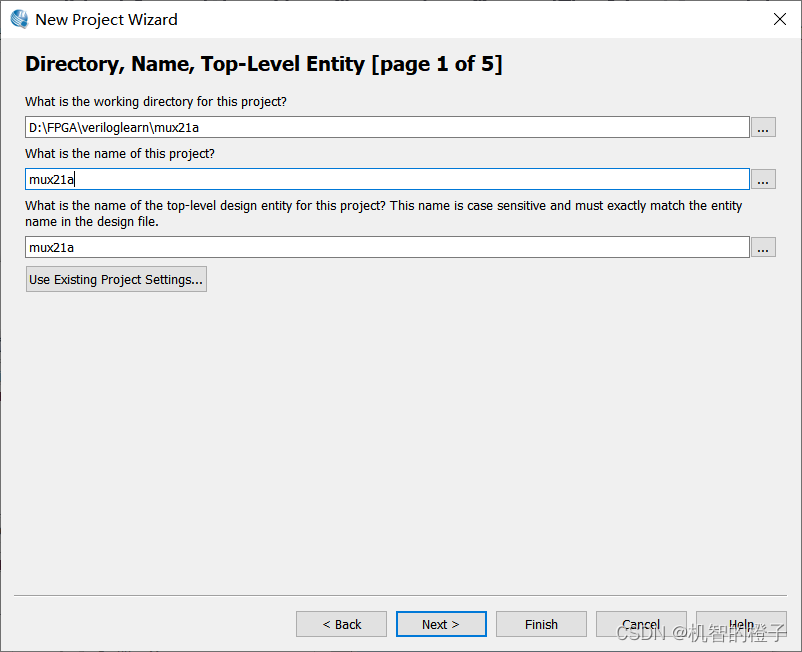

1.新建工程

项目命名:

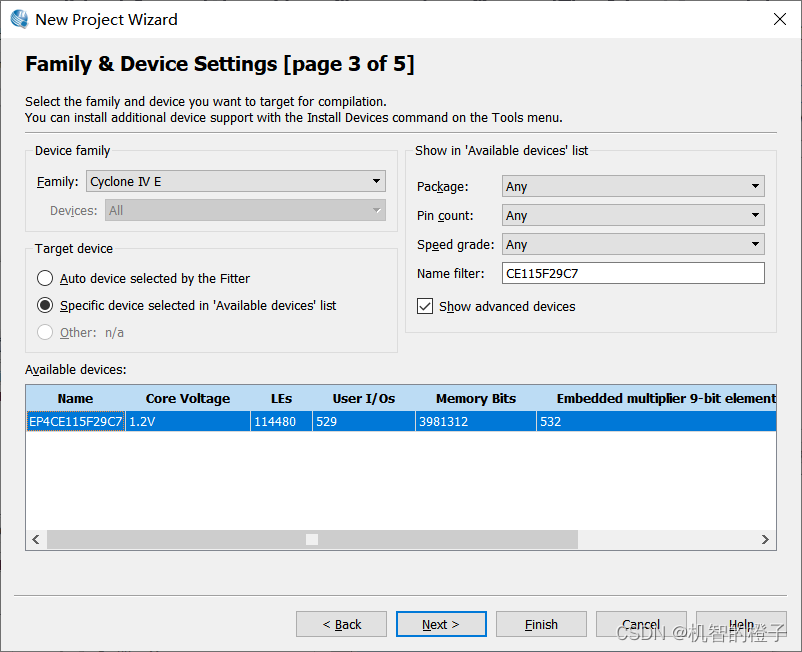

选择芯片:

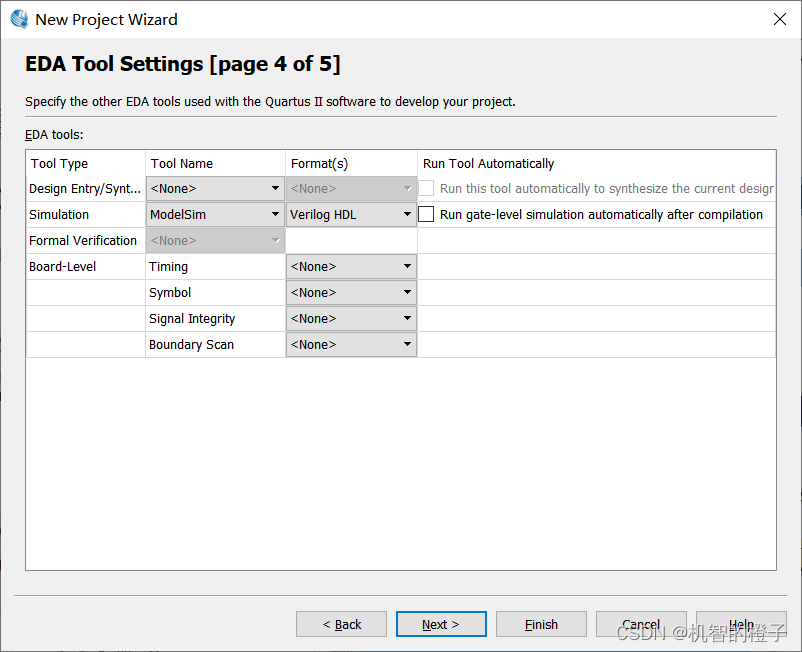

选择仿真软件:

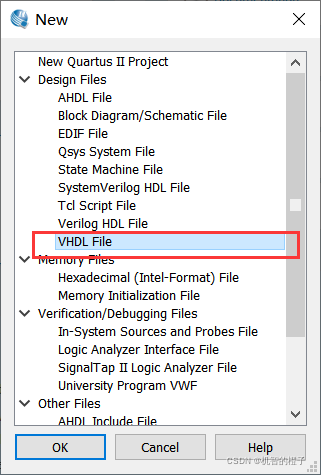

2.创建VHDL文件

点击File->New->VHDL File

编写代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY mux21a IS

PORT ( IN0,IN1,S1:in std_logic;

COUTY : OUT STD_LOGIC);

END mux21a;

ARCHITECTURE behav OF mux21a IS

BEGIN

COUTY<=IN0 when S1='0' ELSE IN1;

END behav;

保存文件为mux21a.vhd

3.编译

编译成功:

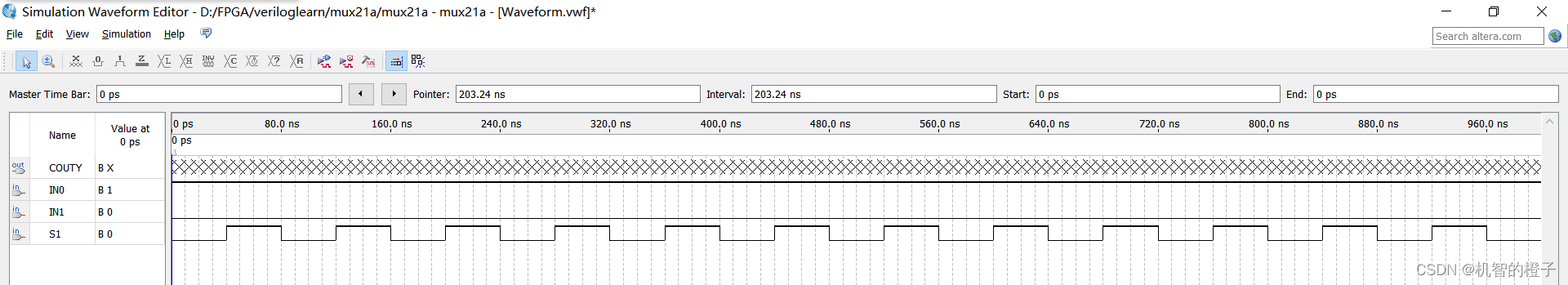

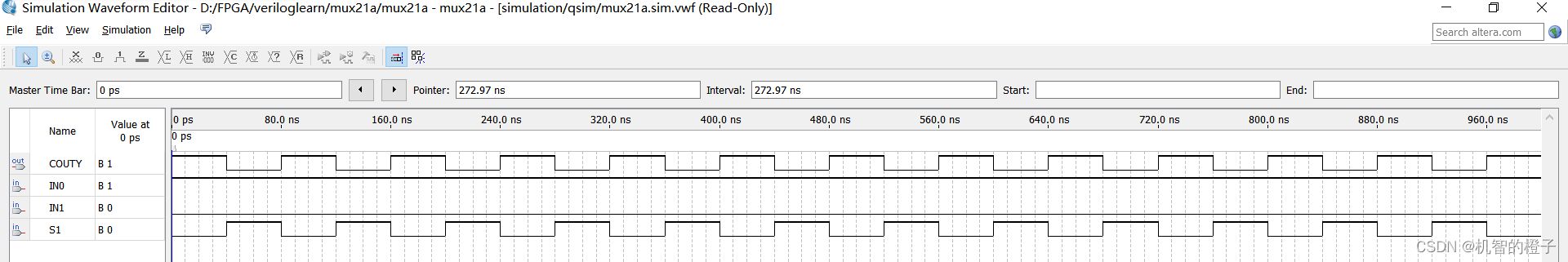

4.功能仿真

新建波形文件

保存为mux21a.vwf

点击运行:

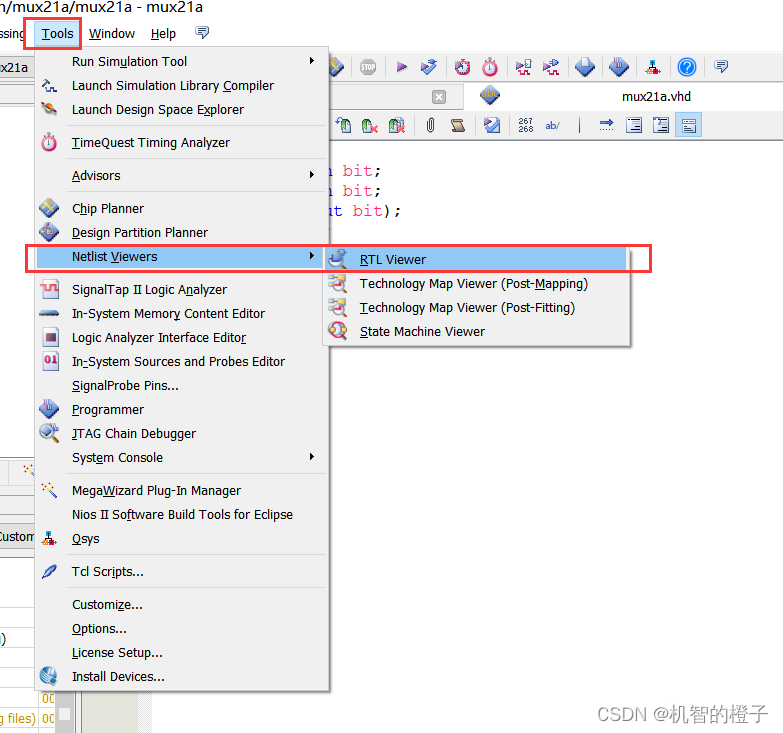

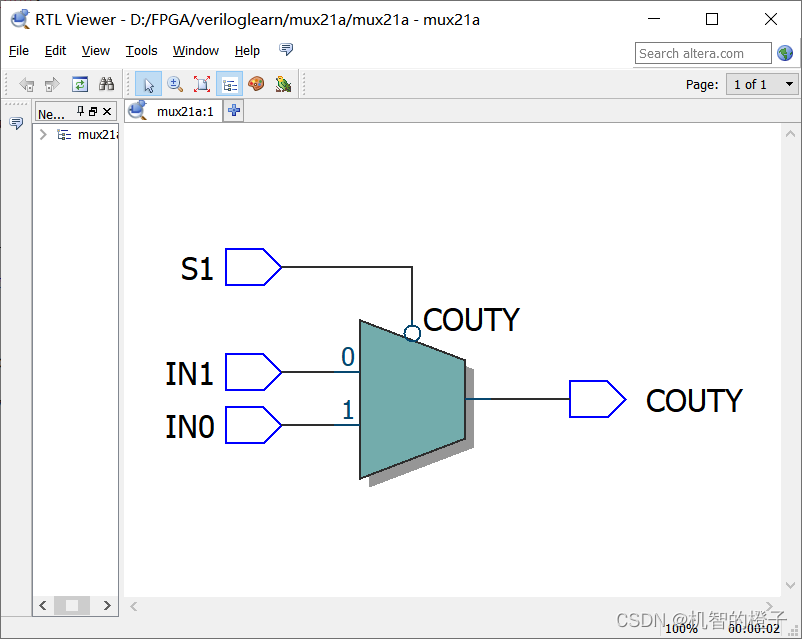

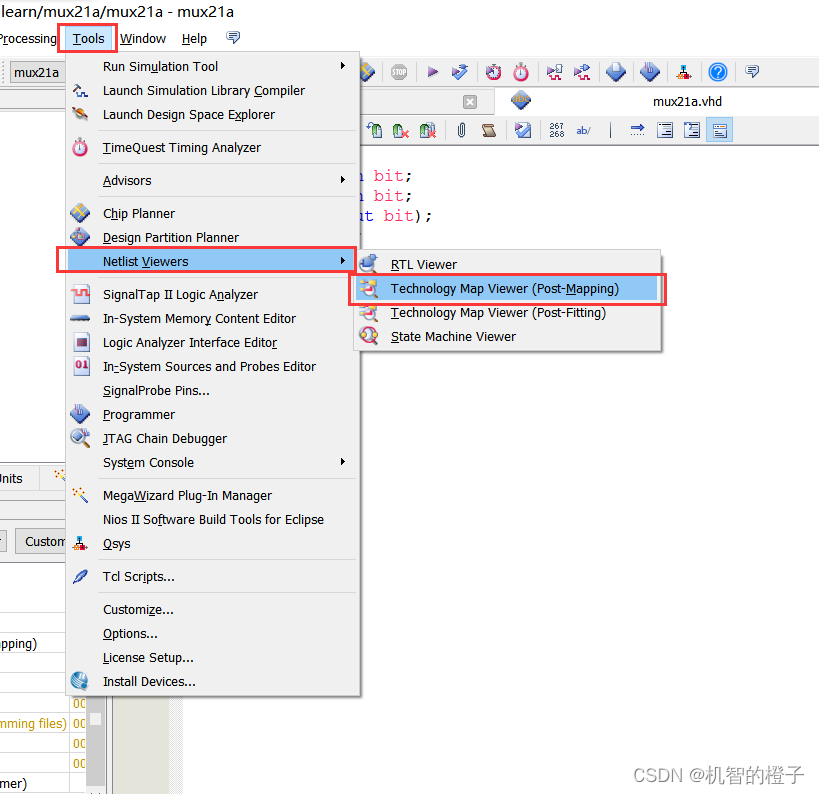

5.查看RTL电路和门电路

点击Tools->Netlist Viewers->RTL Viewer

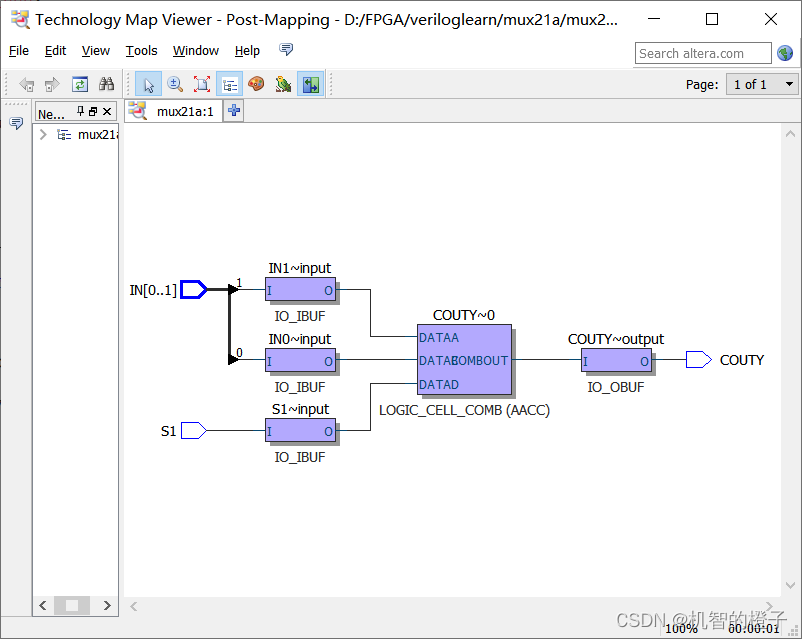

点击Tools->Netlist Viewers->Technology Map Viewer 生成如下门级电路

6.硬件测试

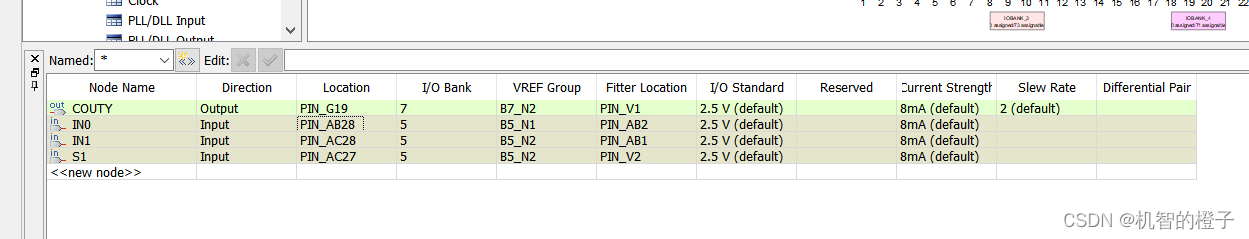

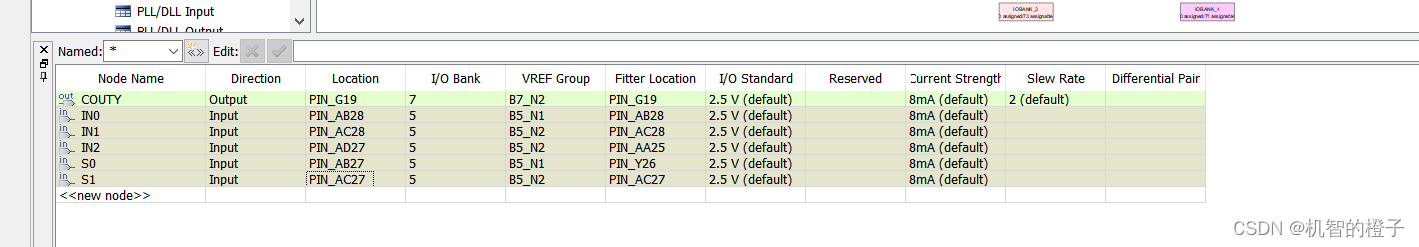

绑定引脚:

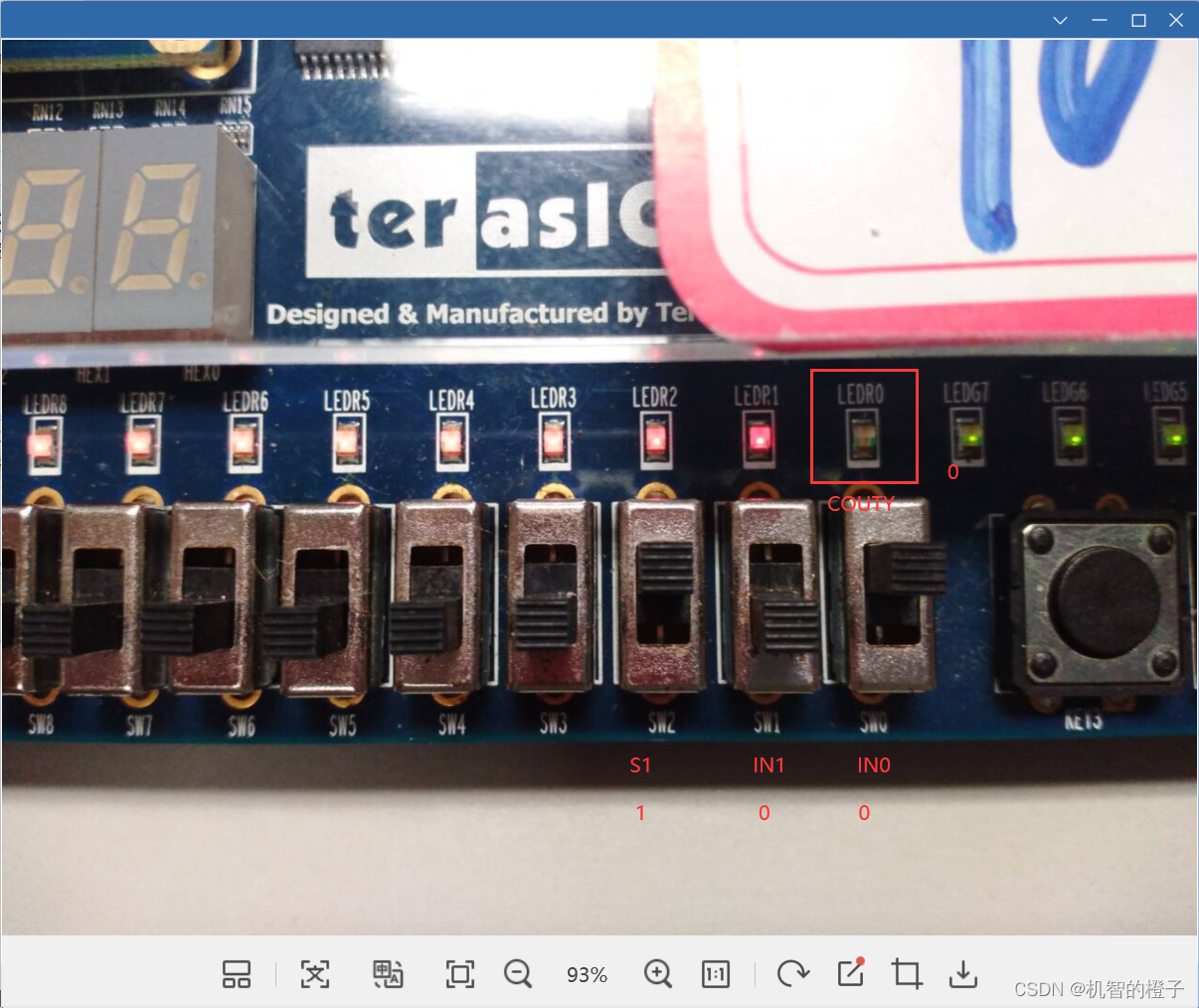

下载测试:

当s1为1时,COUTY=IN1=0

当s1为0时,COUTY=IN0=1

②双2选1多路选择器

1.新建VHDL文件

代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY dmux21a IS

PORT ( IN0,IN1,IN2,S0,S1:in STD_LOGIC;

COUTY : OUT STD_LOGIC);

END dmux21a;

ARCHITECTURE BHV OF dmux21a IS

COMPONENT MUX21A

PORT(IN0,IN1,S1:IN STD_LOGIC;

COUTY :OUT STD_LOGIC);

END COMPONENT;

SIGNAL tmp : STD_LOGIC;

BEGIN

u1 : MUX21A PORT MAP(IN0, IN1, S0, tmp);

u2 : MUX21A PORT MAP(IN2, tmp, S1, COUTY);

END BHV;

保存该文件为dmux21a.vhd

将该文件设置为顶层文件

2.编译

编译成功:

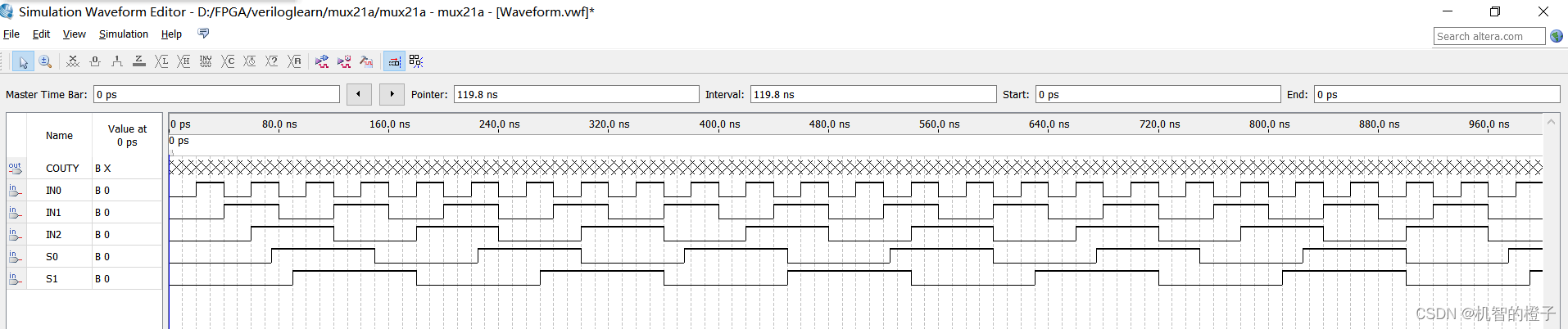

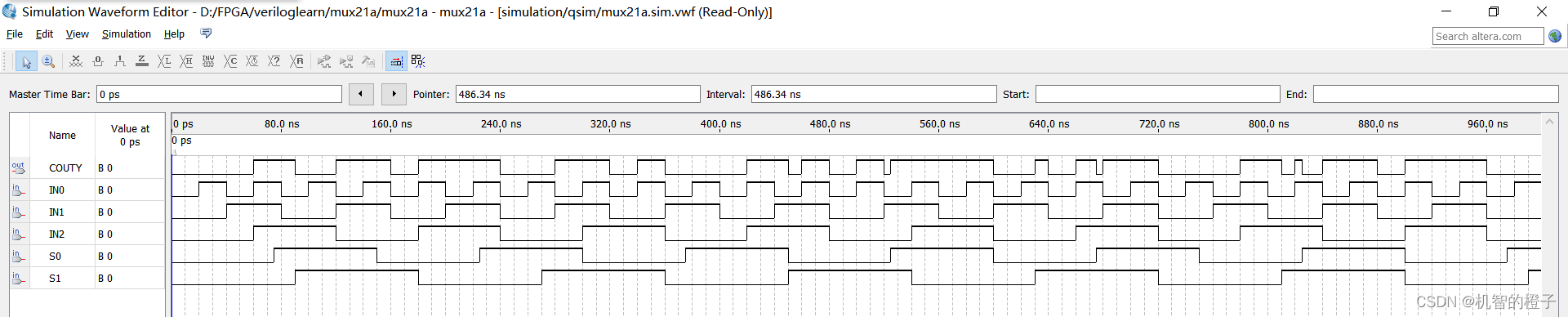

3.新建波形图

保存为dmux21a.vwf

运行:

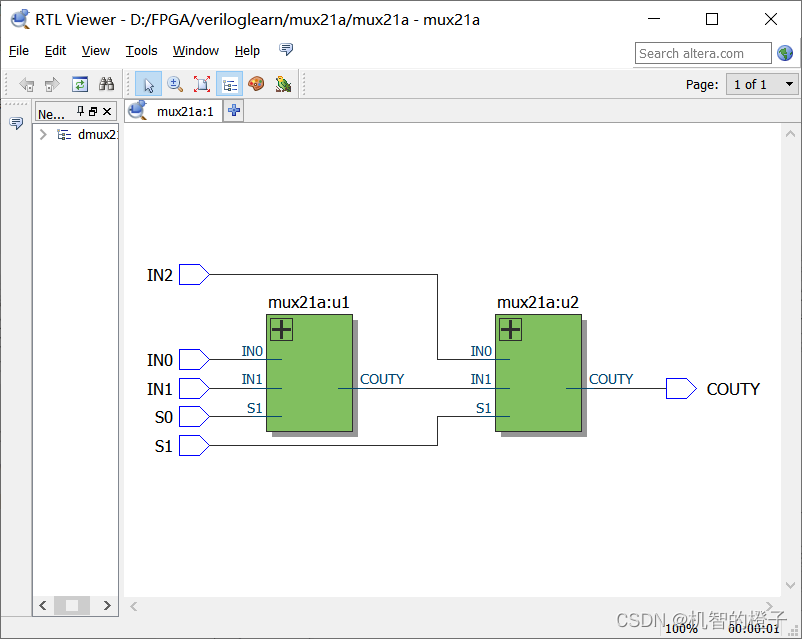

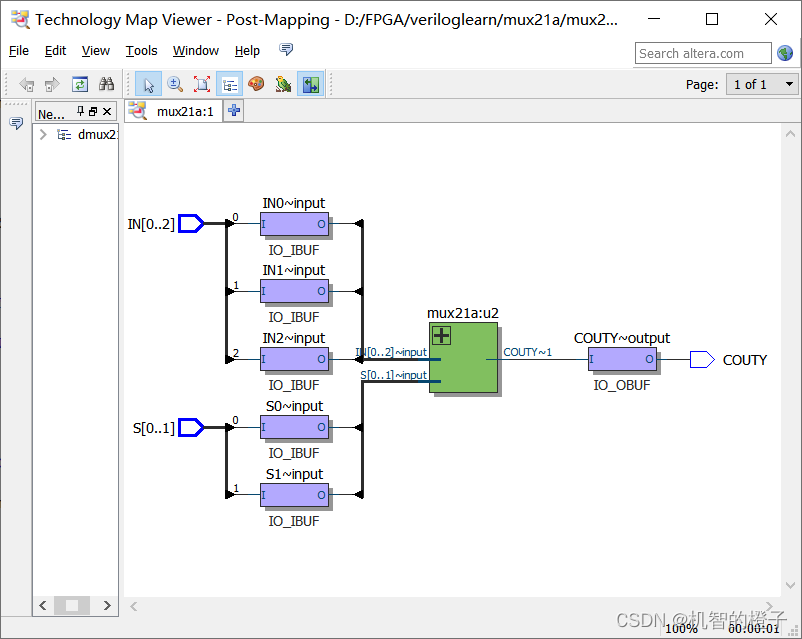

4.查看RTL电路及门级电路

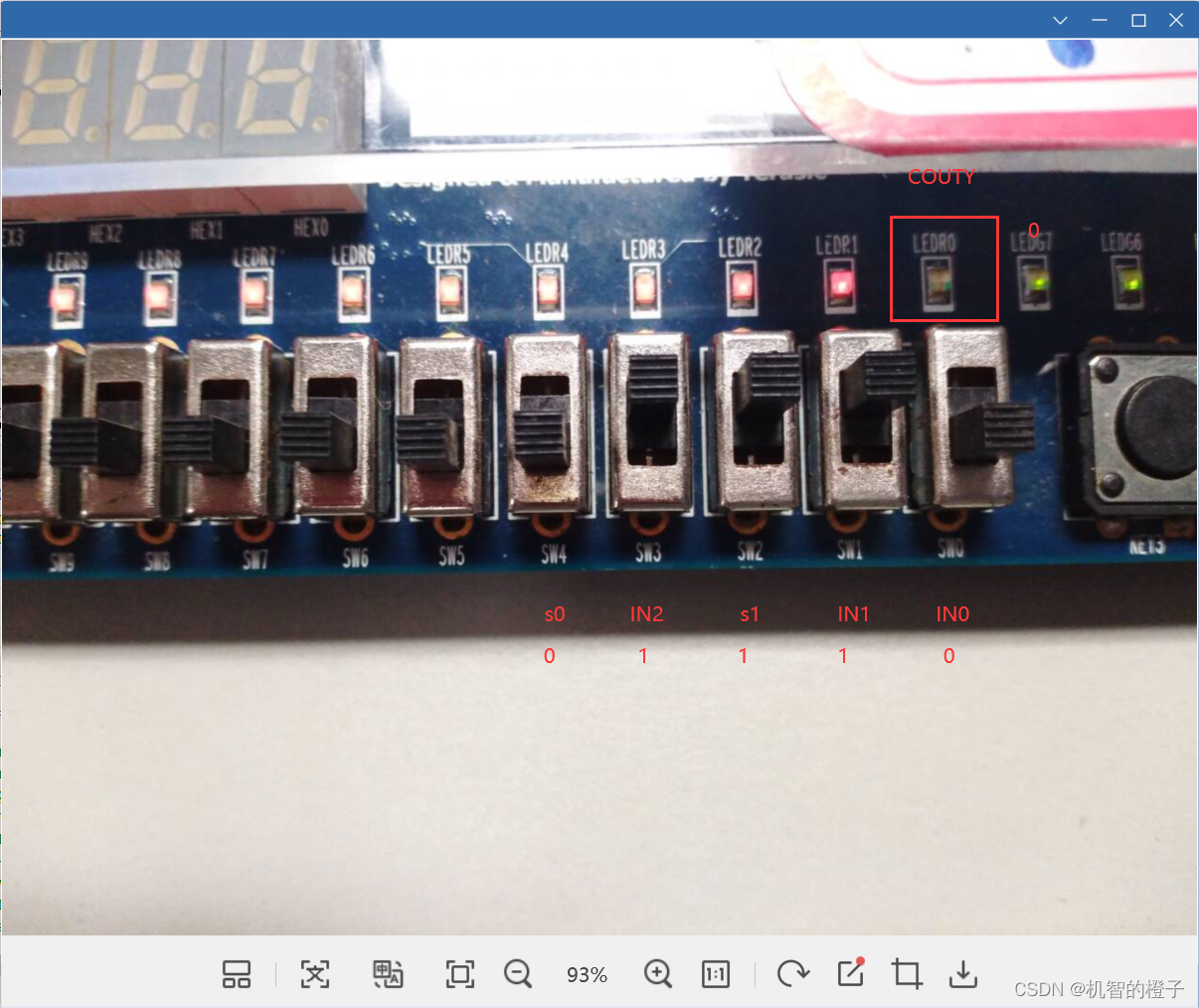

5.硬件测试

绑定引脚:

下载测试:

三.应用QuartusII 完成基本时序电路的设计

①设计触发器

1.新建工程

同上,工程名为trigger

2.新建VHDL文件

代码:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY trigger IS

PORT (CLK : IN STD_LOGIC ;

D : IN STD_LOGIC ;

Q : OUT STD_LOGIC );

END trigger;

ARCHITECTURE bhv OF trigger IS

SIGNAL Q1 : STD_LOGIC ; --类似于在芯片内部定义一个数据的暂存节 点

BEGIN

PROCESS (CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN Q1 <= D ;

END IF;

END PROCESS ;

Q <= Q1 ; --将内部的暂存数据向端口输出(双横线--是注释符号)

END bhv;

文件保存为trigger.vhd

注意!实体名和文件名保持一致

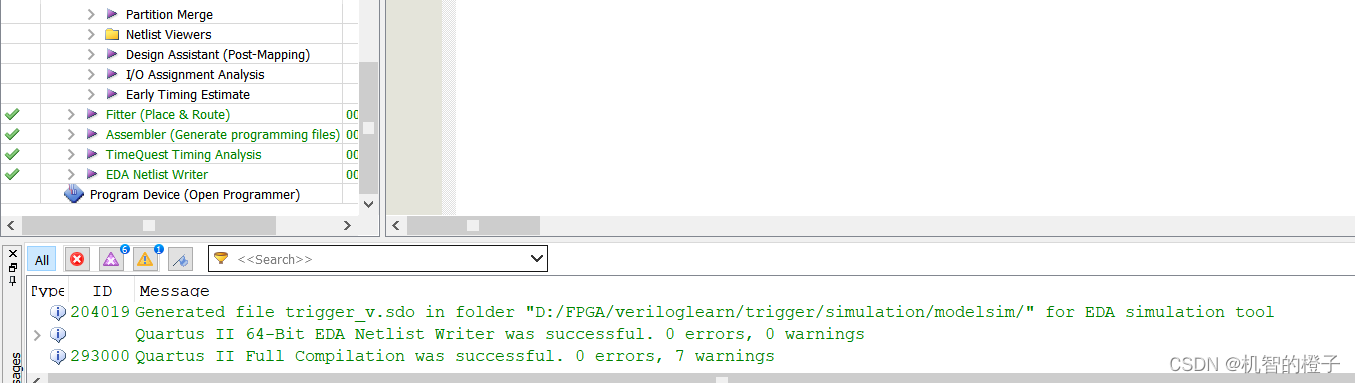

3.编译

编译成功:

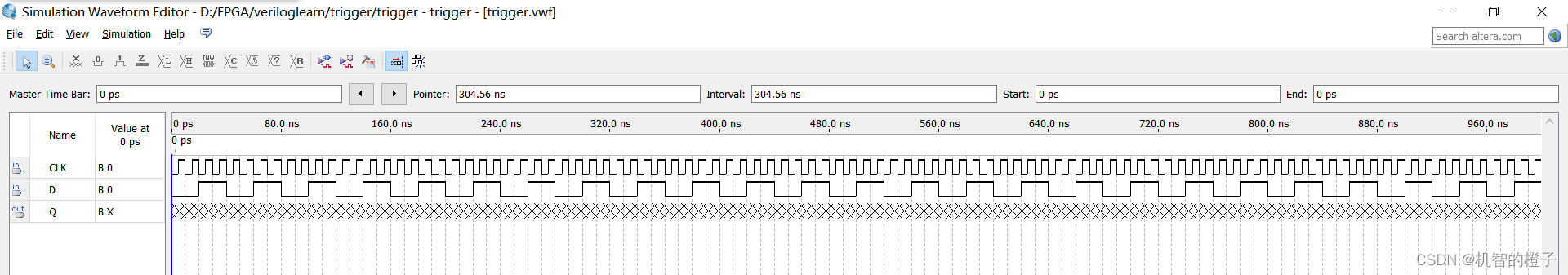

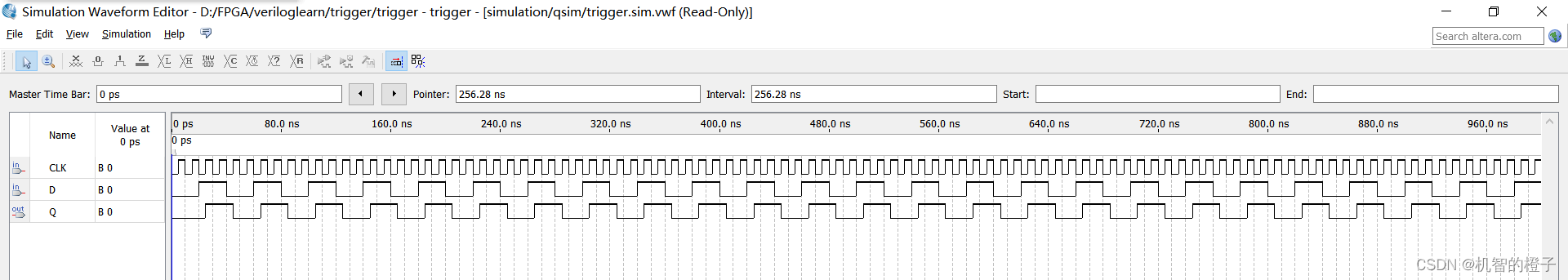

4.新建波形文件

运行:

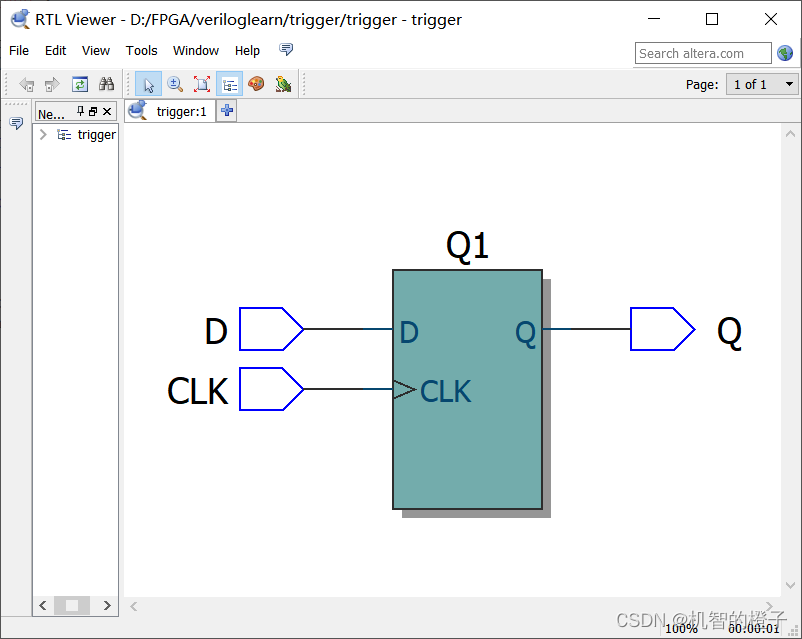

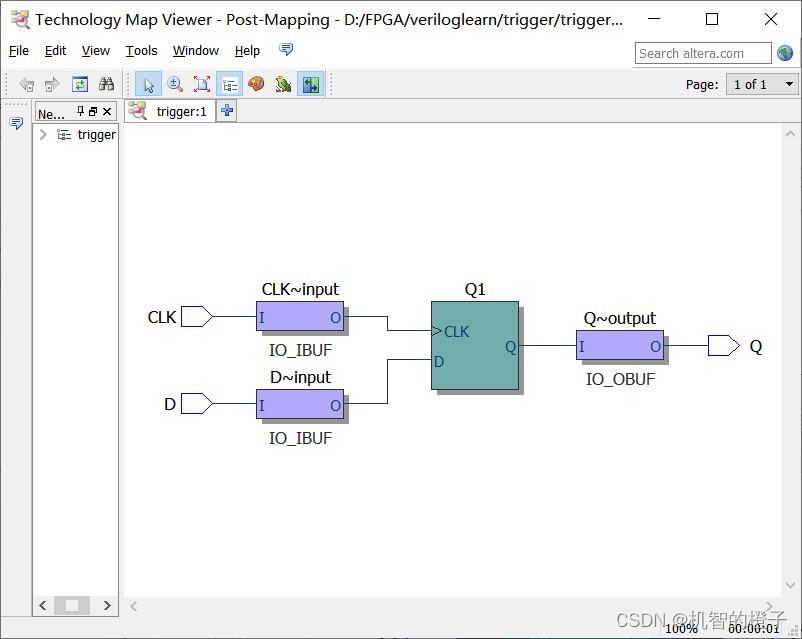

5.查看RTL电路及门级电路

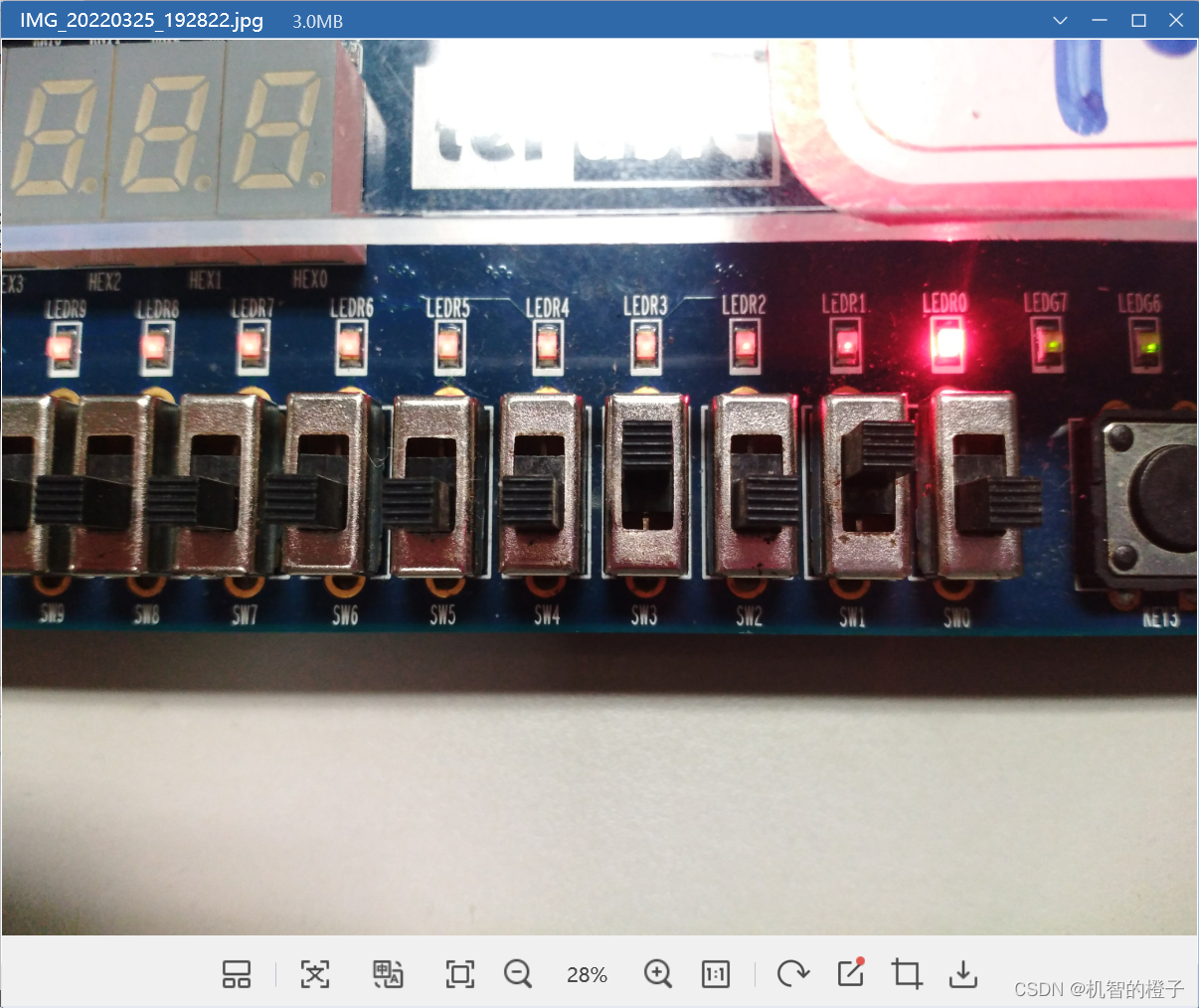

6.硬件测试

绑定引脚:

下载测试:

②设计锁存器

1.新建工程

同上,工程名为latch1

2.新建VHDL文件

代码:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY latch1 IS

PORT (CLK : IN STD_LOGIC ;

D : IN STD_LOGIC ;

Q : OUT STD_LOGIC );

END latch1;

ARCHITECTURE bhv OF latch1 IS

BEGIN

PROCESS (CLK,D) BEGIN

IF CLK = '1' --电平触发型寄存器

THEN Q <= D ;

END IF;

END PROCESS ;

END bhv;

文件保存为latch1.vhd

注意!实体名和文件名保持一致

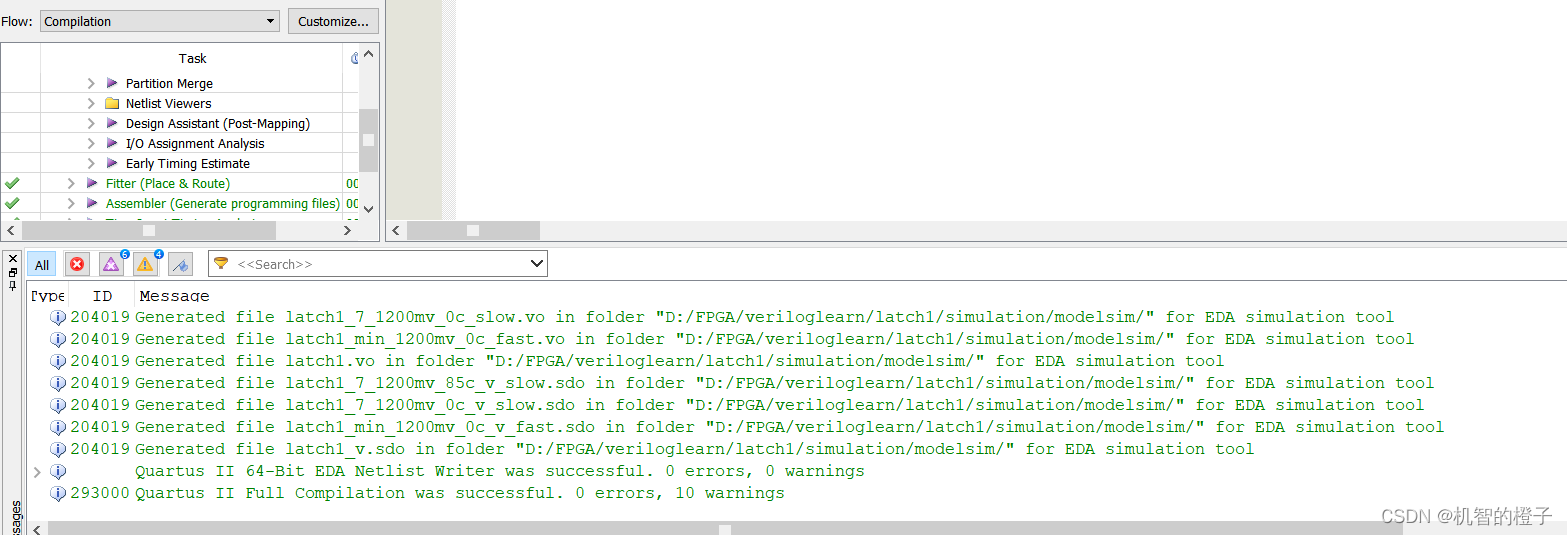

3.编译

编译成功:

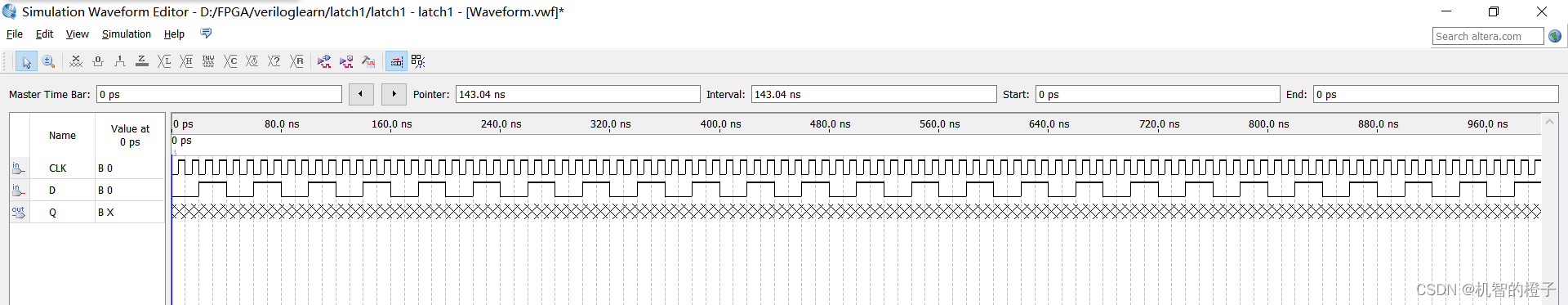

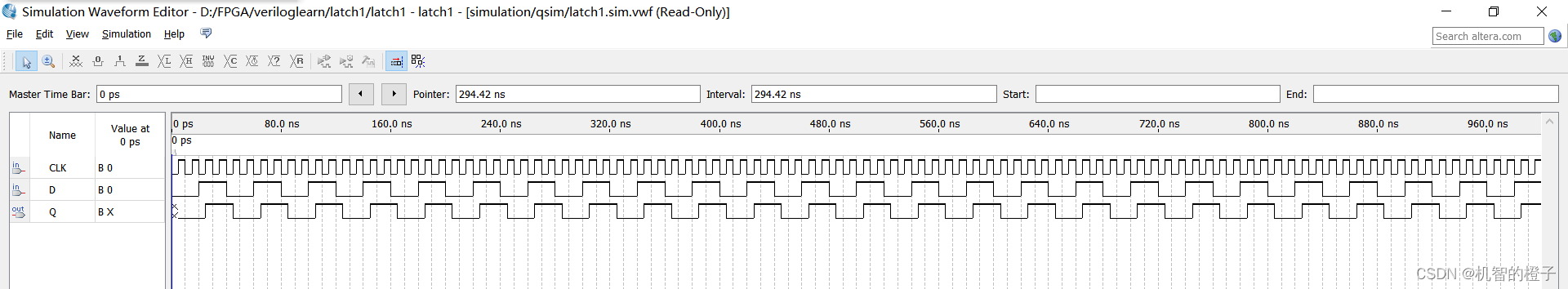

4.新建波形文件

保存为latch1.vwf

运行:

5.查看RTL电路及门级电路

6.硬件测试

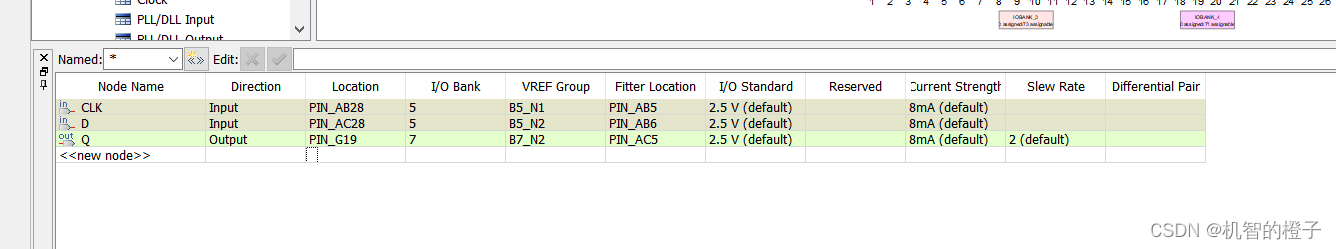

绑定引脚:

下载测试:

四.总结

完成一个比较复杂的电路设计时,可以分解到比较小的电路然后集成,将小电路封装成一个小的单元,然后在实现更复杂电路时,不在关心小电路的内部组成,直接调用,能够简化电路设计。

本文详细介绍了如何使用Quartus II进行VHDL设计,包括4位加法器、2选1/双2选1多路选择器、触发器和锁存器的原理图输入、编译、仿真和硬件测试。通过实例展示了基本组合和时序电路的设计流程。

本文详细介绍了如何使用Quartus II进行VHDL设计,包括4位加法器、2选1/双2选1多路选择器、触发器和锁存器的原理图输入、编译、仿真和硬件测试。通过实例展示了基本组合和时序电路的设计流程。

2626

2626

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?